00

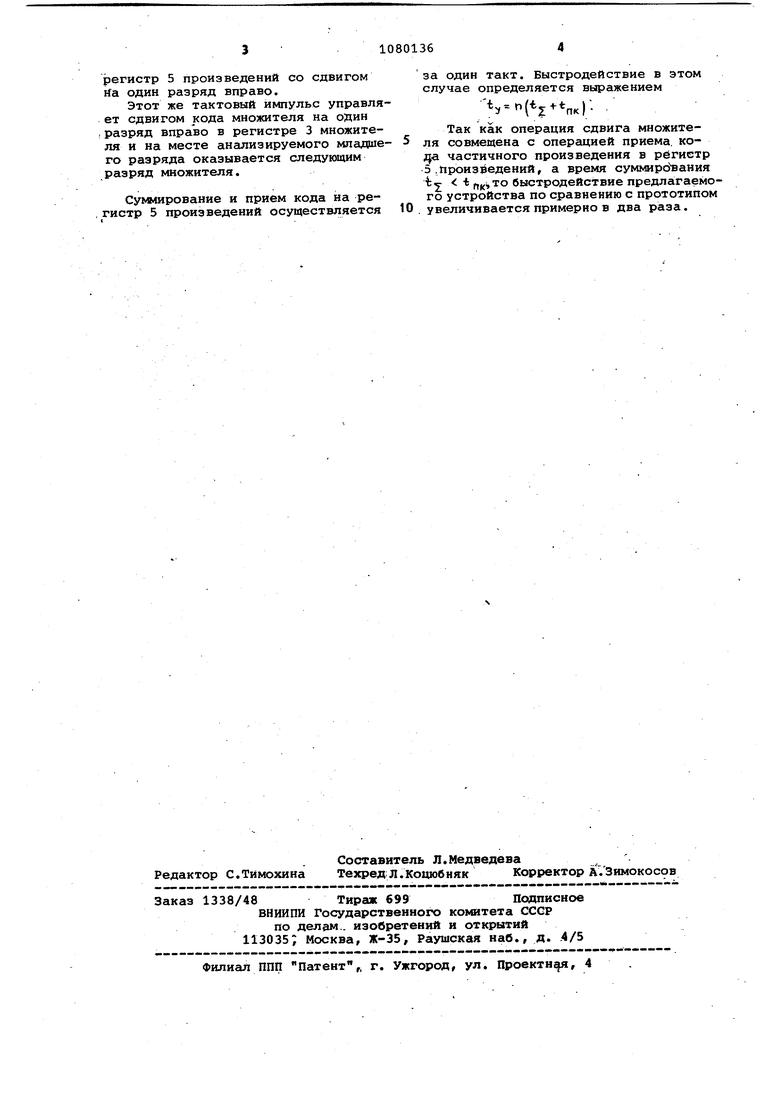

о Изобретение относится к вычисли тельной технике, предназначено для умножения двоичных чисел, представ ленных параллельным кодом, и может быть использовано при построении арифметических устройств специализированных и универсальных ЦВМ. Известно устройство для умножени чисел, содержащее регистр множимого, сдвиговый регистр множителя, комбинационный сумматор частичных произведений, регистр произведений с цепями сдвига вправо, элемент иС Однако это устройство достаточно сложно и обладает невысоким быстродействием. Наиболее близким к предлагаемому является устройство для умножения, содержащее регистр множимого, выходы которого соединены с первыми вхо дами группы элементов И,вторые вход которых объединены и соединены с вы ходом младшего разряда сдвигового р гистра множителя,а выходы соединены с первыми входс1ми комбинационного сумматора частичных произведений, вторые входы которого соединены с соответствующими выходами регистра произведений, входы регистра произведений соединены с выходами сумматора, причем первый вход соединен со вторым выходом, второй - с треть им, ... (п - 11-й - с п-ым, -ый вход соединен с выходом переноса сумматора, вход приема кода регистра произведений соединен с первым тактовым входом устройства, вход сдвига регистра множителя соединен со вторым тактовым входом устройств ваС2, Это устройство упрощено за счет исключения цепей сдвига в регистре произведений путем введения косой передачи с выхода сумматора на вход регистра произведений. Недостатком известного устройства является большое время выполнения операции. Быстродействие устройства опреде ляется выражением t nftj-ttn i) , где 2 . СА соответственн время суммирования, время приема кода на регистр произведений и время сдвига кода в регистр множителя, О: - разрядность множителя. Сумма с выхода сумматора передается на вход регистра произведений со сдвигом на один разряд вправо, т.е. прием кода в регистр произведе ний и сдвиг числа в этом регистре срвг ещены во времени. Сдвиг множителя производится в следующем такте. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройстве, содержащем регистр множимого, регистр множителя, комбинационный сумМатор, регистр произведений, группу элементов И, причем выходы разрядов регистра мно-,, жимого сЪединены соответственно с первымы входами элементов И группы,вторые .входы-которых соединены с выходом младшего разряда регистра множителя, вход сдвига которого соединен с тактовым входом устройства, выходы элементов И группы соединены соответс.тйенно с первой группой информационных входов комбинационного сумматора, вторая группа информационных входов которого соединена с выходами разрядов регистра произведений, входы с первого по (h - 11-и разрядов которого соединены соответственно с выходс1ми со второго по ft-ый разрядов комбинационного сумматора, выход переноса которого соединен с входом п-го разряда регистра произведений, вход приема кода регистра произведений соединен с входом сдвиг га регистра множителя. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит регистр 1 множимого, группу элементов И 2, регистр 3 множителя, комбинационный сумматор 4 и регистр 5 произведений. Вход сдвига регистра. 3 множителя и вход приема кода регистра 5 произведений объединены и подвлючены к тактовому входу устройства. Устройство работает по методу , умножения, начиная с младших разрядов со сдвигом суммы частичных проиэ ведений вправо. Если анализируемая цифра младшего разряда множителя равна 1, то к , сумме частичных произведений при- : бавляется множимое; если эта цифра равна О, прибавление не производится, затем производится сдвиг суммл частичных произведений вправо на один разряд и сдвиг множителя. Эти операции последовательно выполняются для всех цифров разрядов множителя, начиная с младшего. В исходном состоянии в регистрах 1 и 3 множимого и множителя хранятся сомножители; комбинационный сумматор 4 и регистр 5 произведений обнулены. В зависимости от значения О или младшего разряда множителя элеенты И 2 группы либо закрыты, либо ткрыты, и к частичному произведет ию, находящемуся в комбинационном умматоре 4, прибавляется либо нуль, ибо множимое. С приходом тактового импульса олученная сумма передается с выхоа комбинационного сумматора 4 на регистр 5 произведений со сдвигом tia один разряд вправо. Этот же тактовый импульс управля ет сдвигом кода множителя на один ,разряд вправо в регистре 3 множителя и на месте анализируемого младше го разряда оказывается следующим разряд множителя. Суммирование и прием кода на регистр 5 произведений осуществляется за один такт. Быстродействие в этом случае определяется выражением 4,.n(,)-. Так как операция сдвига множителя совмещена с оперещией приема, коца частичного произведения в регистр 5 .Произведений, а время суммирования t -t быстродействие предлагаемого устройства по сравнению с прототипом увеличивается примерно в два раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1975 |

|

SU1206773A1 |

| Устройство для умножения | 1989 |

|

SU1732341A1 |

| Устройство для умножения | 1984 |

|

SU1275432A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения последовательных двоичных кодов | 1987 |

|

SU1495786A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистр множимого, регистр множителя, комбинационный сукфяатор, регистр произведений, группу элементов И, причем выходы разрядов регистра множимого соединены соответственно с первыми входами элементов И группы, вторые входы которых соединены с выходом младшего разряда регистра множителя, вход сдвига которого соединен ,с тактовым входом устройства,выходы элементов И группы соединены соответственно с первой группой информационных входов комбинационного сумматора, вторая группа информационных входов которого соединена с выходами разрядов регистра произведений, входы с первого по (п - 1|-й разрядов которого соединены соответственно с выходами со второго по h-й разрядов комбинационного сумматора, выход переноса которого соеди- р нен с входом п -го разряда регистра ig произведений, отличающее(Л с я тем, что, с целью повышения быстродействия, в нем вход приема кода регистра произведений соединен с входом сдвига регистра множителя,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Самофалов К.Г | |||

| и др | |||

| Электронные цифровые маиганы | |||

| Киев, 1976, с..299, р | |||

| ТЕЛЕФОННЫЙ АППАРАТ, ОТЗЫВАЮЩИЙСЯ ТОЛЬКО НА ВХОДЯЩИЕ ТОКИ | 1920 |

|

SU274A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Каган Б.м | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М., Энергия, 1979, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1984-03-15—Публикация

1983-01-10—Подача