00 ел

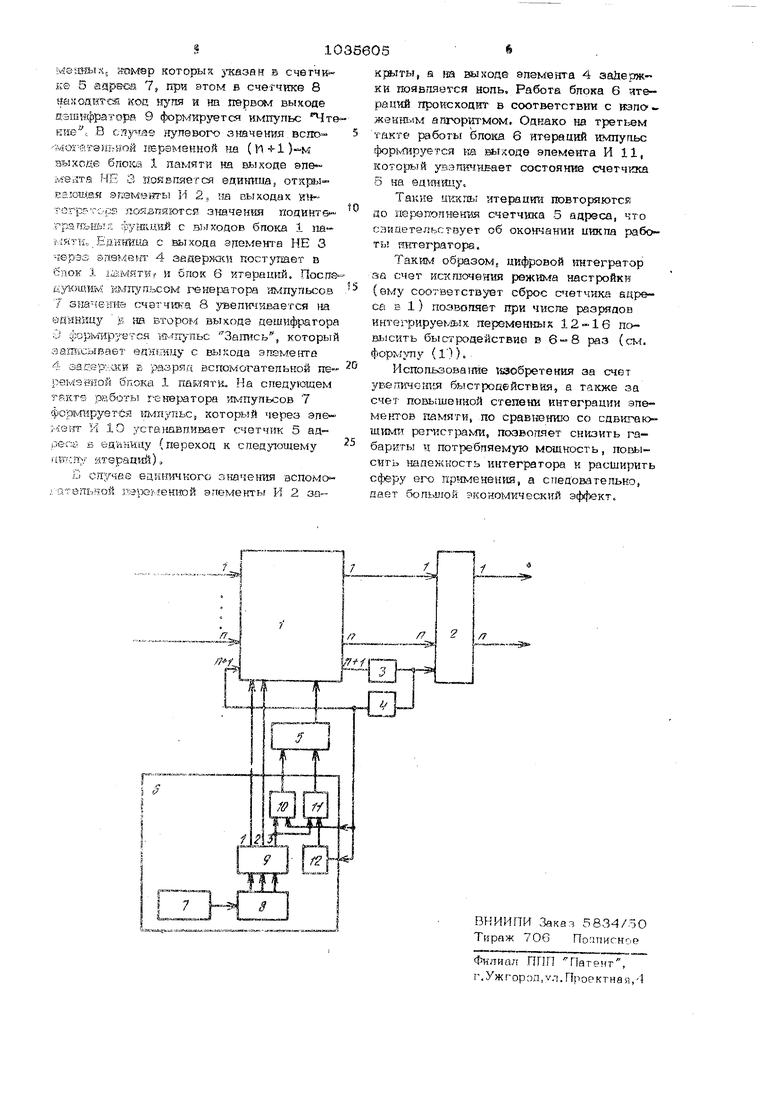

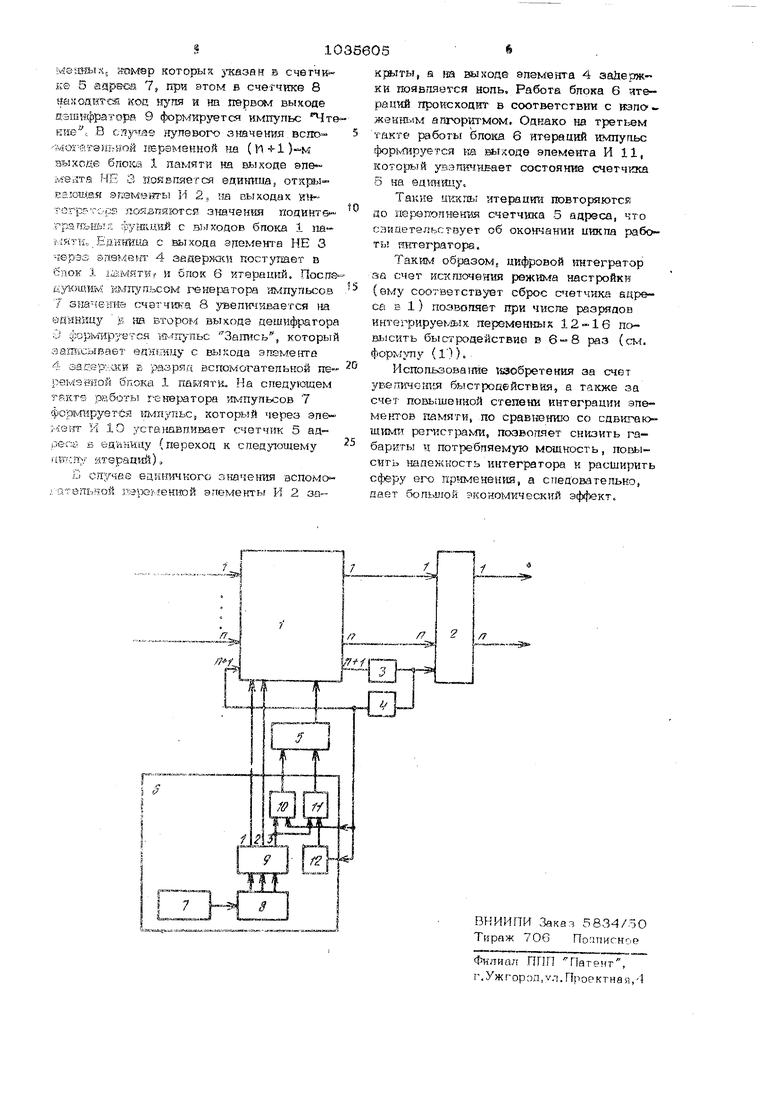

О5 f1 Изобретение относится к вычиспитепь ным устройствам систем управпе тя и может быть использовано в системах числового программного управпения про- изводственгным оборудованием. Известен интегратор, содерхощнй бпо преобразова шя подинтеграпьной функции, первый эпемент И, бдок итераций, про граммный бпок, содержащий сдвигчэвый регистр, сумматор, первый вход которого подсоединен к выходу блока итераций, второй вход - к выходу сдвигового регис тра, а первый выход - к входу сдвиговог регистра, эпемент задержки, входом со© диненный со вторым выходом сумматора, допопнитепьно введен второй эпемент И, первый вход которого соединен с выходом эпемента задержки, второй вход соединен с выходом бпока итераций, а вь(ход подсоединен к третьему входу сумматора первый вход первого эпемента И подсое- динен к первому выходу сумматора, второй вход первого эпемента И подсоединен к выходу сдвигового регистра, третий вход первого эпемента И подсоединен к выходу бпока преобразования подинте грапьной функции . В гаком устройстве объем комбинационной части, включающий в себя первый эпемент И, эпемент задержки и сумматор огратгч.ен и не растет с ростом числа разрядов. Однако объем комбинационной части по-прежнему остается зЕшчитепьны Недостатками интегратора являются бопьшив затраты аяпаратныл средств на его реализацию и сложные связи, Паибопее близким к предлагаемому является цифровой интегратор, к котором исключен сумматор. Такой цифровой интегратор содержит регистр подинтеграпьдай функции, регистр сдвига, первый эпемент И, блок итераций, второй элемент И, первый вход которого под ключен к первому выходу блока итераций второй выход которого подключен к ут равллющим входам регистра подкнтеграпь ной функции и регистра сдвига, выход которого подключен к его входу, а также через элемент НЕ подключен к входу эпемвнта задержки, выход которого подключен ко второму входу первого эле- Meirra И, входу бпока итераций и к второму входу второго элемента И, выход которого подключен к входу первого разряда регистра сдвига. Первьгй вход первого эпемента И подключен к выходу регистра гюдинтеграпьной функции, а выход первого эпемента М является выхо05дом интегратора, В исходном состоянии регистр сдвига обвупен, а в регистре подинтегральной функции записано значение интегрируемой фушшии. Информация в peniCTpe сдвига сдвигается в сторону младших разрядов, а в регистре подинтегральиой функции - в сторону старших разрядов. Если в первом разряде регистра сдвига записан нупь, то на выходе элемента НЕ возникает единица, которая поступает на элемент задержки. В первом такте эта единица через открытый второй элемент И записывается в первъ й разряд регистра сдвига, открывает первый элемент И и на выходе появляется значение подинтеграпьной функции. Единица с выхода эпемента задержки поступает также на вход блока итерации, что переводит его в режим настройки, в котором информация в регистре подинтегральнои функции и регистре сдвига нормализуется ( старший и мпадший разряды соответственно занимают правое положение). Еспи в первом разряде зйписана единица, то сдвиг информации происходит до разряда, в котором записан нуль, после чего цифровой интегратор работает так же, как .описано выше 2. Недостатками такого интегратора являются низкое быстродействие ввиду необходимости включения режима настройки в рабочий цикп и все еще достаточно большая агатарагная реализашад. Повышение быстродействия за счет исключения режима настройки можно охарактеризовать следующим ..приближенным расчетом. Общее число тактов дгш данного ин1егратора составляет 1С 2., где 1( - число разрядов интегрируемых перемен ых. Однако чиспо рабочих тактов (общее число тактов за вычетом гактов нормализации) Составляет лишь - 1. Таким образом выигрыш в быстродействии интегратора при отсутствии режима настройки составляет k-n „ 19 „.. -±, - -4-(1) 21Г - 1Г Цепь изобретения - повышение быстродействия интегратора за счет искпючешш ежима настройки из его рабочего цикла и снижение аппаратных затрат на его реализацию. Указанная цепь достигается тем, что в цифровой интегратор, содержащий бпок тераций, эпементов И, эпемент НЕ, эпемент задержки, причем выход элемента НЕ через эпемент задержки подкгаочен к входу бпока итераций, введе ны счетчик адреса и блок памяти, причем Y входов бпока памяти соединены со входами интегратора, а и выходов блока памяти соединены с первыми входами элементов И гру1шы, (и+1)-й выход бпока памяти соединен со входом эпемек та НЕ, выход которого подключен ко вто рым входам эпементов И группы, выход элемента задержки подключен к (И+1) -му входу блока памяти, первый выход блока итераций подключен к входу задания режима чтения бпока памяти, второй выход бпока итераций подключен к входу задания режима записи блока памяти, третий выход блока итераций соединен с входом установки счетчика адреса в единицу, четвертый выход блока итераций соединен со счетным входом счетчика адреса, выходы которого соединены с адресными входами блока памяти. На чертеже представлена структурная схема предлагаемого цифрового интегратора. Интегратор содержит блок 1 памяти группу эпементов И 2, элемент НЕ 3, элемент 4 задержки, счетчик 5 адреса, блок 6 итераций. Блок итераций состоит из поспедовательно соединенных-генератора импульсов 7, счетчика по модулю три 8, дешифратора 9, элементов И 10 и 11. и элемент НЕ 12. Первый вход элемента И 10 подключен к выходу элемента задержки 4 не посредственно, а первый вхоц элемента И 11 - через элемент НЕ 12. Блок 1 памяти представляет собой массив запоминающих ячеек объемом (VI +1) 1, гае и - число интегрируемых переменных, а 1 - разрядность указанных переменных. В строках от 1 до и помещены интегрируемые переменные, а в (у +1)-й - вспомогательная переменная. Счетчик адреса 5 принимает значения от 1 до k и указывает номер разряда интегрируемых и вспомогательной переменных, к которому производится обраще ние, причем при значении счетчика адреса, равном 1, происходит обращение к старшему разряду интегрируемых переменных и к младшему - вспомогательной. Блок 6 итераций обеспеч шает в устройстве подачу определенной последовательности сигналов, управляющих работой устройства. Элемент задержки 4 задерживает информацию на половину такта работы блока итераций 6. Интегратор работает следующим образом. Пусть имеется функция времени VCt ), BbinontniB квантование по уровню и времени, получаем дискретную функцию (-i) квантованного времени -Ь . Требуется воопроизвести интеграл 3(ТГ)--Ь(г)аг. о По формуле прямоугольников ;(r)3a)z4(0ut-i (i)1-1i-iВыходным сигналом предложенного интегратора является поток приращений и теграла. Для этого .X ( i ) должны быть преобразованы в поток единичных приращений Y : ( Н ). Для реализации ци4ро-частотного преобразования подинтегральной функции (Y-t) в поток единичных приращений AYj (О каждый квант времени депится на 2 циклов итерации. Значение фушшии V ( t) в течение каждого кваига времени постоянно (Х( О), а изменение функции Y (-t) происходит при переходе к следующему временному кванту. Рассмотрим один квант времени. При этом значение подинтегральной функции подразумевается постоянным . ti)--., где лУх ( -i ) О или 1; 1с - число двоичных разрядов подинтеграпьной функции. Для реализации указанного уравнения предназначена вспомогательная переме - ная, которая формирует квазиравномерный поток единичных приращений путем ледова тельного во времени опроса разрядов подинтегральной функции способом частотной модуляции, имеющим следующий вид .Mi,,),SaV,N4.N,(, ГДР VK значение V -го разряда 4(1); .г- г Yli) В исходном состоянии в и строках блока памяти 1 находятся интегр1фуемыв переменные, а вспомогательная поременная обнулена. Счетчик 5 адреса установлен в единицу. Цикл работы интегратора начинается с чтения КЗ блока 1 памяти разряда rsepe

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1978 |

|

SU739566A1 |

| Цифровой интегратор | 1978 |

|

SU698017A1 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

| Цифровое вычислительное устройство | 1977 |

|

SU646337A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

ЦИФРОВОЙ ИНТЕГРАТОР, содержащий бпок итераций, группу элементов И, элемент НЕ и элемент эадерз ки, причем выход элемента НЕ через элемент задержки подключен к входу блока итераций, выходы элементов И группы соединены с выходами интегратора, о тличаюшийся тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, в него ввепеял CHOTW чик адреса и бткж памяти, причем ii входов бшка памяти соедивешл с вхоаами интегратора, а И шлхоаов блока памяти подключены к первым входам элементов И групшл, (И-4-1)-й выход бпока памяти соединен со входом элемента НЕ, выхоц которого подключен ко вторым входам элементов И группы, выход элемента зд1 ержки подключен к (И+1)-му входу блока 11амяти, первый выход блока итераций подключен к входу задания режима чтения блока памяти, второй выход блока итераиий подключен к входу задания режима записи блока памяти, третий выход блока итераций соединен с входом устаг /новки счетчика адреса в едитшу, четвер« (Л тый выход блока итераций соединеи со счетным входом счетчика адреса, выходы которого соединены с адресными входами блока памяти. §

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой интегратор | 1976 |

|

SU720427A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой интегратор | 1978 |

|

SU739566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-15—Публикация

1981-08-31—Подача