Изобретение относится к автоматике и вычислительной технике и предназначено дпя преобразования данных без изменения объема информации.

Известны преобразователи параллельных двоичных кодов в число-импупьсный код ij. Эти гфеобразователи имеют сложную конструкцию.

Наиболее близким по технической сущности к изобретеншо является преобразоватепь параллельното двоичного кода в число-импульсный код, содержащий регист счетчики, логические элементы Г2. В схеме такого преобразователя равномерность следования выходных им1ульсов достигается за счет выбора максимальной разрядности счетчиков.

Однако и этот преобразователь отличается конструктивной сложностью, что снижает его надежность.

Цепью изобретения является упрощение преобразователя.

Это достигается введением в преобразователь блока формирователей импульсов и элемента задержки, причем выходы

счетчика через блок формирователей импульсов соединены с входами элемента ИЛИ, выход которого через элемент за«epjfcKH подключен к выходу преобразователя н к счетному входу счетчика, разрядные входы которого являются информационными входами преобразователя.

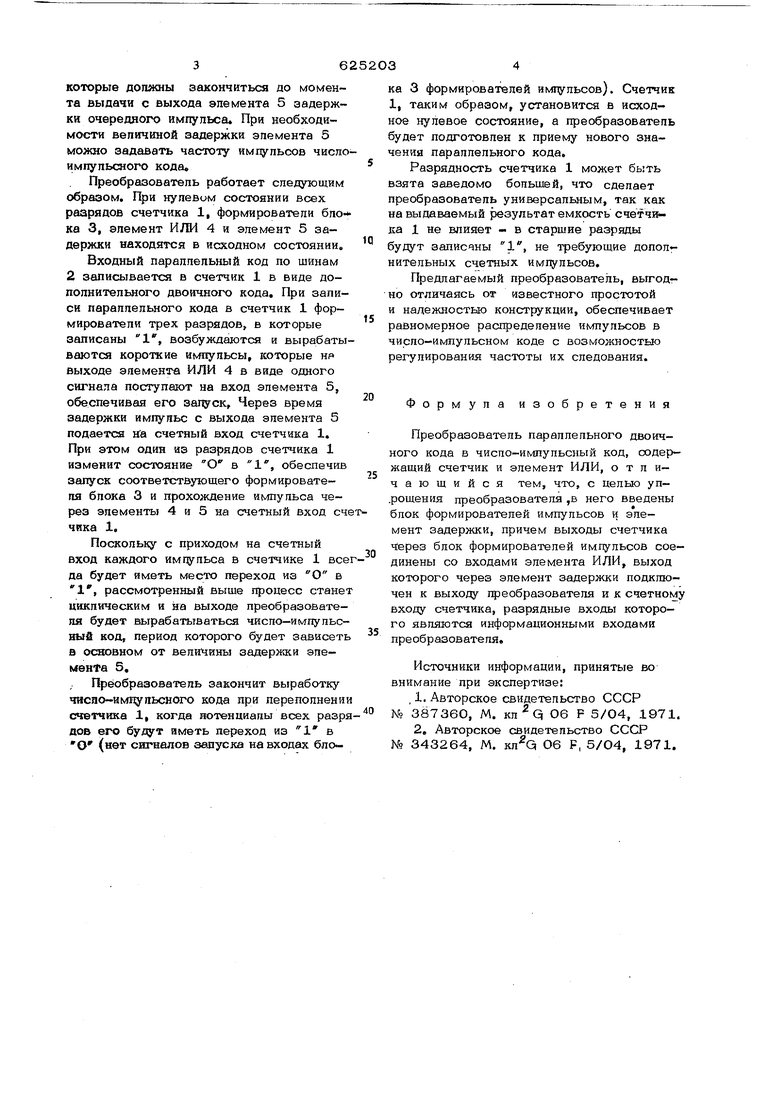

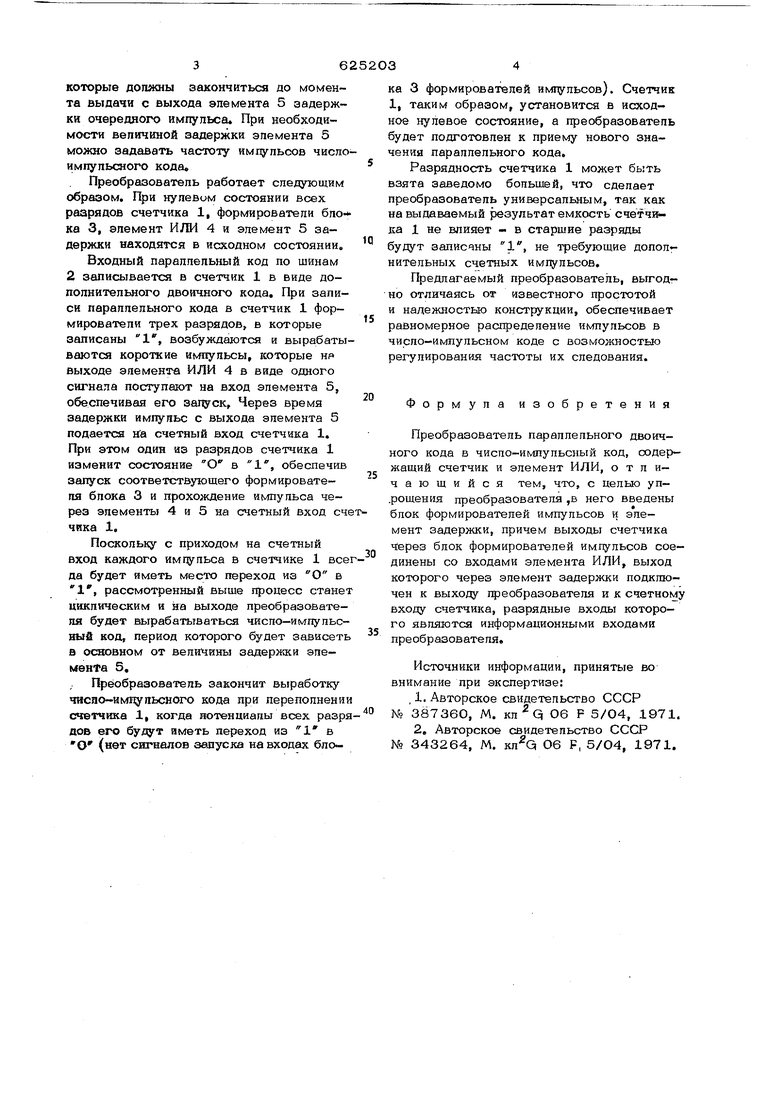

На чертеже представлена блок-схема преобразователя параллельного двоичного кода в число-имгульсный код.

Предлагаемый преобразователь содержит счетчик 1, информационные входы 2, блок 3 формирователей импульсов, элемент ИЛИ 4, элемент 5 задержки.

Блок 3 предназначен для формирования коротких импульсов от перепада потенциала в соответствующих разрядах счетчика 1 при переходе а состояние , и в простейщем случае может быть реализован в виде дифференцир ших цепочек, пропускающих импульсы одной полярности.

Величина задержки элемента 5 выбирется из расчета длительности переходных процессов в элементах 1, 3 и 4, 6 которые должны закончиться до момента выдачи с выхода элемента 5 задержки очередного импульса. При необходимоспги величиной задержки элемента 5 можно задавать частоту импульсов число импульсного кода. Преобразователь работает следующим образом. При нулевом состоянии всех разрядов счетчика 1, формирователи блока 3, элемент ИЛИ 4 и элемент 5 задержки находятся в исходном состоянии. Входный параллельный код по шинам 2 записывается в счетчик 1 в виде дополнительного двоичного кода. При записи параллельного кода в счетчик 1 формирователи трех разрядов, в которые записаны 1, возбуждаются и вырабаты ваются короткие импульсы, которые HP выходе элемента ИЛИ 4 в виде одного сигнала поступают на вход элемента 5, обеспечивая его зацуск. Через время задержки импульс с выхода элемента 5 подается на счетный вход счетчика 1. При этом один из разрядов счетчика 1 изменит состояние О в i, обеспечив запуск соответствующего формирователя блока 3 и прохождение импульса через элементы 4 и 5 на счетный вход сч чика 1. Поскольку с приходом на счетный вход каждого имгульса в счетчике 1 все да будет им;еть место переход из О в 1, рассмотренный выше процесс стане циклическим и на выходе преобразователя будет вырабатываться число-импульсный код, период которого будет зависеть в осаовном от величины 3af№p KKH элемен1 а 5, Преобразователь закончит выработку чисио-имиуиьсного кода при переполнени счетчика 1, когда нотеициалы всех разр дов его будут иметь переход из I в О (нет сигналов запуска на входах бло34ка 3 формирователей импульсов). Счетчик 1, таким образом, установится в исходное нулевое состояние, а преобразователь будет подготовлен к приему нового значения параллельного кода. Разрядность счетчика 1 может быть взята заведомо большей, что сделает преобразователь универсальным, так как на выдаваемый результат емкость счетчика 1 не влияет - в старшие разряды будут записаны 1, не требующие дополнительных счетных импульсов. Предлагаемый преобразователь, выгодно отличаясь от известного простотой и надежностью конструкции, обеспечивает равномерное распределение импульсов в число-импульсном коде с возможностью регулирования частоты их следования. Формула изобретения Преобразователь параллельного двоичного кода в число-импульсный код, содержащий счетчик и элемент ИЛИ, отличающийся тем, что, с целыо уп- .рощения преобразователя ,в него введены блок формирователей импульсов и элемент задержки, причем выходы счетчика Через блок формирователей импульсов соединены со входами элемента ИЛИ, выход которого через элемент задержки подключен к выходу преобразователя и к счетному входу счетчика, разрядные входы которого являются информационными входами преобразователя. Источники информации, принятые во внимание при экспертизе: , 1. Авторское свидетельство СССР № 38736О, М. Об Р 5/04, 1971. 2, Авторское свидетельство СССР № 343264, М. Об F, 5/О4, 1971.

« е

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в число-импульсный код | 1983 |

|

SU1164692A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство преобразования последовательного двоичного кода в код десятичный | 1978 |

|

SU782155A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1262732A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

о 6

Авторы

Даты

1978-09-25—Публикация

1977-05-03—Подача