Изобретение относится к вычисли .тельной, технике и может быть исполь зовано в запоминающих устройствах ЦВМ с последовательной обработкой и формации. Известно запоминающее устройство (ПЗУ) с вьвдачей информации в последовательном коде, содержащее регистр входы которого соединены с соответствующими логическими шинами адресные шины, элементы И и ИЛИ, причем первые входы элементов И соединены с соответствукадими выходами регистра, вторые - с соответствующими адресными шинами, а выходы - со входами элемента ИЛИ Недостатком этого устройства является большое количество разрядов регистра при хранении большого количества чисел, так как для хранения mn-разрядных чисел необходим ре5истр разрядности m +п-1, где m - количество чисел,п -разрядность записанных чисел.. Наиболее близким к изобретению по технической сущности является портоянное запоминающее уст;ройство, содержащее регистр сдвига, элементы И по числу разрядов регистра сдвига .и элементы ИЛИ, причем выходы регис |тра сдвига соединены с информационными входами элементов И, управляющий вход которых подключен к соответствующей адресной шине, а выход соединен со входом элемента ИЛИ, входы регистра сдвига подключены к соответствующим шинам логических нуля и единицы, соответствующий вход регистра сдвига соединен с .шиной Обращение,, а выход последнего разряда регистра сдвига подключен ко входу его первого разряда 2j. Недостатком данного ПЗУ является его сложность при хранении больших массивов чисел. Цель изобретения - повышение информационной емкости устройства. Поставленная цель достигается тем, что в устройство, содержащее первый кольцевой регистр сдвига, входы которого подключены соответственно к шинам логических нуля и единицы, тактовой шине, шине Обращение и шине установки в исходное состояние, элемент ИЛИ, входы iifoTopoго С9един(экы с выходгияи элементов И группы, адресные шины введены регистр сдвига, триггер, элемент И, второй кольцевой регистр сдвига, две группы элементов ИЛИ., входы которых подключены к соответствующим адресным шинам. Выходы элементов ИЛИ первой группы подключены к управляющим входам элементов И группы, а выходы элементов ИЛИ второй группы подключены к информационным входам регистра сдвига, информационный выход которого подключен к. входу разрешения записи второго кольiieBoro регистра сдвига и единичному входу триггера, нулевой вход которого соединен с шиной устанрвки в исходное состояние, выход триггера соединен с первым входом элемента И, второй вход которого соединен с шиной тактовых импульсов, а выход - с тактовыми входами второго кольцевого регистра сдвига, установочные входы которого соединены с установочными входами первого кольцевого регистра сдвига, информационные входы второго кольцевого регистра сдвига соединены с информационными выходами первого кольцевого регистра сдвига, а информационные выходы - с информационными входами элементов И группы, шины Обращение и тактовая подключены к соответствующим входам регистра сдвига.

Предлагаемое устройство позволяет уменьшить количество ячеек памяти регистров сдвига и элементов в сравнении с известным устройством при. хранении одинакового количества чисел.

Это достигается благодаря возможности разбиения эйлерова графа на подграфы с равным количеством ребер что эквивалентно представлению массива 2 п-разрядных чисел в виде п-разрядных групп с различньм количеством единиц и различным сочетание единиц и нулей в них. Это позволяет начальный код числа представить в виде нескольких начальных кодов чисел которые записываются соответствующим образом в кольцевом регистре сдвига, из которого эти начальные коды чисел считываются в другой кольцевой регистр сдвига, из которого уже выбирается непосредственно необходимое число.

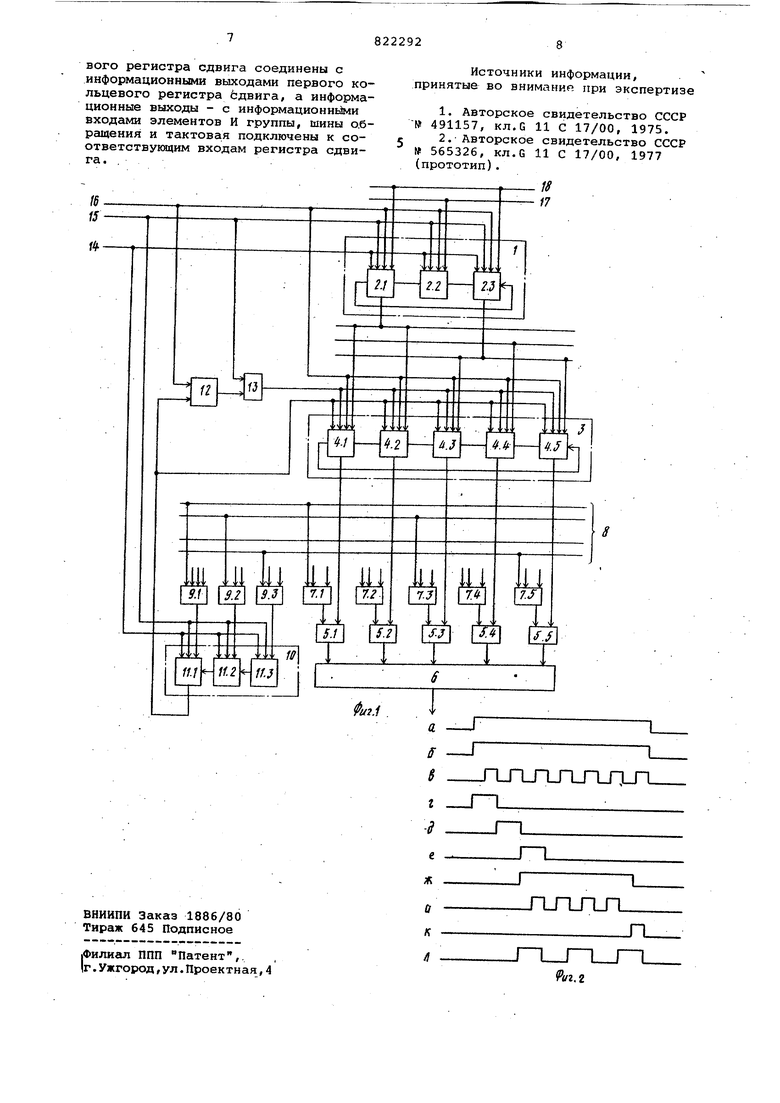

На фиг.1 представлена блок-схема устройства на 15 пятиразрядных двоичных числах; на фиг.2 - временная диаграмма работы устройства.

На диаграмме выделены (фиг.2) а- сигнал Обращение на шине

.управления Обращение ; б- сигнал на выбранной адресной

шине; в - тактовые импульсы «а тактово

шине управления; г,д.ие -сигналы на выходах регистра

сдвига;

ж- сигнал на выходе Триггера; и- сигналы на тактовых входах второго кольцевого регистра сдвига;

к - сигнал на шине установки в

исходное состояние; л- сигналы на выходе устройства. Предлагаемое ПЗУ (фиг.1) содержит ервый кольцевой регистр 1 сдвига, остоящий из ячеек памяти, втоой кольцевой регистр 3 сдвига, сотоящий из ячеек памяти, элемены И 5 , элемент ИЛИ 6, первую группу элементов ИЛИ 7, адресные шины 8, вторую группу элементов ИЛИ 9, регистр 10 сдвига, состоящий из ячеек 11, памяти, триггер 12, элемент И 13, шины 14 управления Обращение, 15 тактовую, 16 установки в исходное состояние, 17 и 18 логических 1 и О соответственно.

Кольцевые регистры 1 и 3 сдвига предназначены для записи начальных кодов чисел, определяемьах подсоединением информационных параллельных входов регистров, причем входы первого кольцевого регистра 1 сдвига подсоединяются к шинам 17 и 18 логических 1 и О, а входы второго кольцевог6 регистра 3 сдвига - к информационным выходам первого кольцевого регистра 1 сдвига, и образуют накопитель информации. Изменяя подсоединение информационных параллельных входов кольцевых регистров 1 и 3 сдвига, можно изменять записываемые начальные коды чисел, тем самым изменять массив.хранимых в устройстве чисел..

Регистр 10 сдвига предназначен для организации выборки определенного начального кода чийла из первого кольцевого регистра 1 сдвига.

Две группы элементов ИЛИ 7 и 9служат для организации произвольной выборки чисел из устройства по данному адресу путем соединения входов ЭТИХ элементов к соответствующим адресным шинам 8, причем для выборки одного числа к выбранной адресной шине 8 надо подключить по одному . входу соответствующих элементов ИЛИ 7 и 9.

Количество чисел, записанных в устройство, равно п х р , где п и рколичество ячеек 4 и 11 памяти во втором кольцевом регистре 3 сдвига и регистре 10 сдвига, а разрядность записанных в устройстве чисел равняется разрядности чисел, записанных во втором кольцевом регистре 3 сдвига-.

Предлагаемое ПЗУ работает следующим образом.

В исходном состоянии регистры 1, 3 и 10 и триггер 12 находятся в нулевом состоянии. При поступлении импульса Обращение с шины 14 на входы разрешения записи регистров 1 и 10 приходит разрёшакиций сигнал, и в регистр 1 записывается начальный код числа, а в регистре 10 подготавлива)ются информационные входы. Одновременно с поступлением импульса Обращение возбуждается одна выбранная ад ресная шина 3, с которой разрешающи сигнал через соответствующий элемен ИЛИ 7 поступает на управляющий вход одного элемента И 5, а через соотве ствующий элемент ИЛИ 9 сигнал посту пает на информационный вход одной ячейки 11 памяти, а так как все яче ,ки 11 памяти уже подготовлены импул сом Обращение, то в эту ячейку 11 записывается логическая 1. Затем на шину подеется первый та товый сигнал, который сдвигает по кольцу на один разряд начальный код числа в первом кольцевом регистре 1 сдвига, подключая к информационнымвходам регистра 3 вторые разряды чи сел, записанных в регистре 1. Одновременно первый тактовый сигнал в регистре 10 сдвигает записанную 1 влево в соседнюю ячейку 11 памяти. При поступлении последующих тактовы сигналов по шине 15 происходит сдви по кольцу начального кода числа в регистре 1 с подключением к информа ционным входам регистра 3 последующих разрядов чисел, записанных в регистре 1, и перенос в соседние ячейки 11 памяти 1 в регистре 10 до тех пор, пока 1 не запишется в ячейку 11.1 памяти, с выхода которой сигнал поступает на единичный вход триггера 12, устанавливая на его еди ничном выходе разрешающий сигнал, и на вход разрешения записи регистра 3, записывая в него те разряды чисел записанных в регистре 1, которые к этому моменту устанавливаются на его выходе. Из этих разрядов чисел в регистре 3 формируется начальный код числа, -соответствующий г-разрядным числам, первые разряды которых посту пают на информационные входы элементов И 5. С выхода элемента И 5, на управляющем входе которого установле разрешающий сигнал, первый разряд выбранного разрядного числа через элемент ИЛИ 6 поступает на выход уст ройства. Затем на шину 15 подается следующий тактовый сигнал, который сбрасывает сигнал на выходе ячейки 11.1 памяти и формирует на выходе элемента И 13 первый сигнал, который поступает на тактовые входы регистра 3, сдвигая начальный код числа в нем на один разряд по кольцу, подключая к выходу устройства второй разряд выбранного г-разрядного числа. С поступлением на шину 15 последующих тактовых сигналов на выходе элемента И 13 формируются тактовые сигналы, которые сдвига,ют в регистре 3 начальный код числа, подключая к выходу устройства следующие разряды выбранного г-разрядного числа. После поступления с выхода элемента И 13 г-1 тактового сигнала на регистр 3, на выходе устройства сформируется последний разряд выбранного числа. Затем на шине 16 установки в исходное состояние формируется сигнал, который устанавливает регистры 1 и 3 и триггер 12 в нулевое состояние. Устройство готово к следующему обращению. Предлагаемое устройство лучше всего использовать в ПЗУ для хранения чисел небольшой разрядности (не более восьми), так как при большой разрядности надо будет строить начальные коды чисел по эйлерову графу с большим количеством ребер. Так, для десятиразрядных чисел потребуется граф 2° с ребрами.. Само по себе построение такого графа сложно, не говоря уже о трудности выбора оптимальных начальных кодов чисел для записываемого массива информации. Предлагаемое устройство можно использовать в ПЗУ с невысоким быстродействием, но к которым предъявляются жесткие требования по количеству оборудования и потребляемой мощности. Предлагаемое устройство по сравнению с известным дает выигрыш в количестве оборудования при хранении равных массивов информации. Формула изобретения Постоянное запоминающее устройство, содержащее первый кольцевой регистр сдвига, входы которого подключены соответственно к шинам логического нуля и единицы, тактовой шине, шине Обращение и шине установки в исходн.ое состояние, элемент ИЛИ, входы которого соединены с выходами элементов И группы, адресные шины, отличающееся тем, что, с целью повышения информационной емкости устройства, в него . введены регистр сдвига, триггер, элемент И, второй кольцевой регистр сдвига,две группы элементов ИЛИ, входы которых подключены к соответствующим гадресным шинам, выходы элементов ИЛИ перг вой группы подключены к управляквдим входам элементов И группы, а выходы элементов ИЛИ второй группы подключены к информационным входам регистра-сдвига, информационный выход которого подключен к входу разрешения записи второго кольцевого регистра сдвига и единичному входу триггера, нулевой вход которого соединен с шиной установки в исходное состояние , выход триггера соединен с первым входом элемента И, второй вход которого соединен с шиной тактовых импульсов, а выход - с тактовыми входами второго кольцевого регистра двига, установочные входы которого оединены с установочными входами ервого кольцевого регистра сдвига, нформационные входы второго кольцевого регистра сдвига соединены с информационными вьаходами первого кольцевого регистра Ьдвига, а информационные выходы - с информационными входами элементов И группы, шины о.бращения и тактовая подключены к соответствукяцим входам регистра сдвига. .

{6

IS

/ Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР -№ 491157, кл.С 11 С 17/00, 1975.

2.Авторское свидетельство СССР 565326, кл.С 11 С 17/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU815769A2 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Запоминающее устройство | 1980 |

|

SU900317A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Авторы

Даты

1981-04-15—Публикация

1979-06-29—Подача