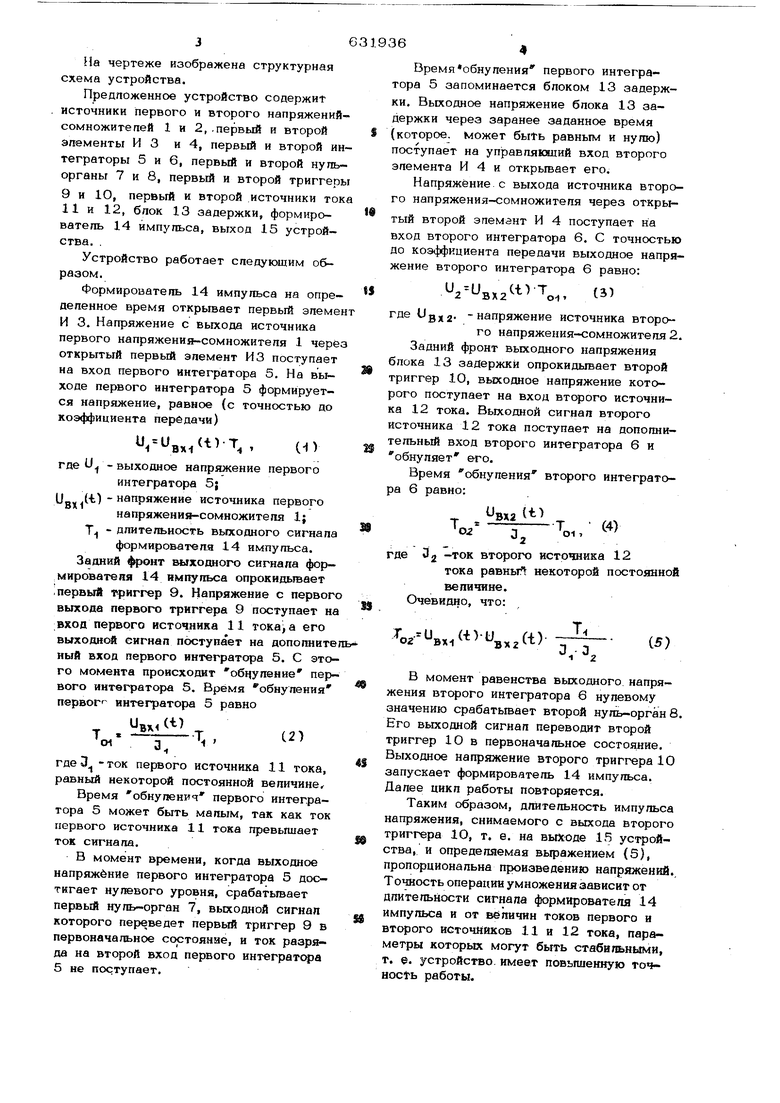

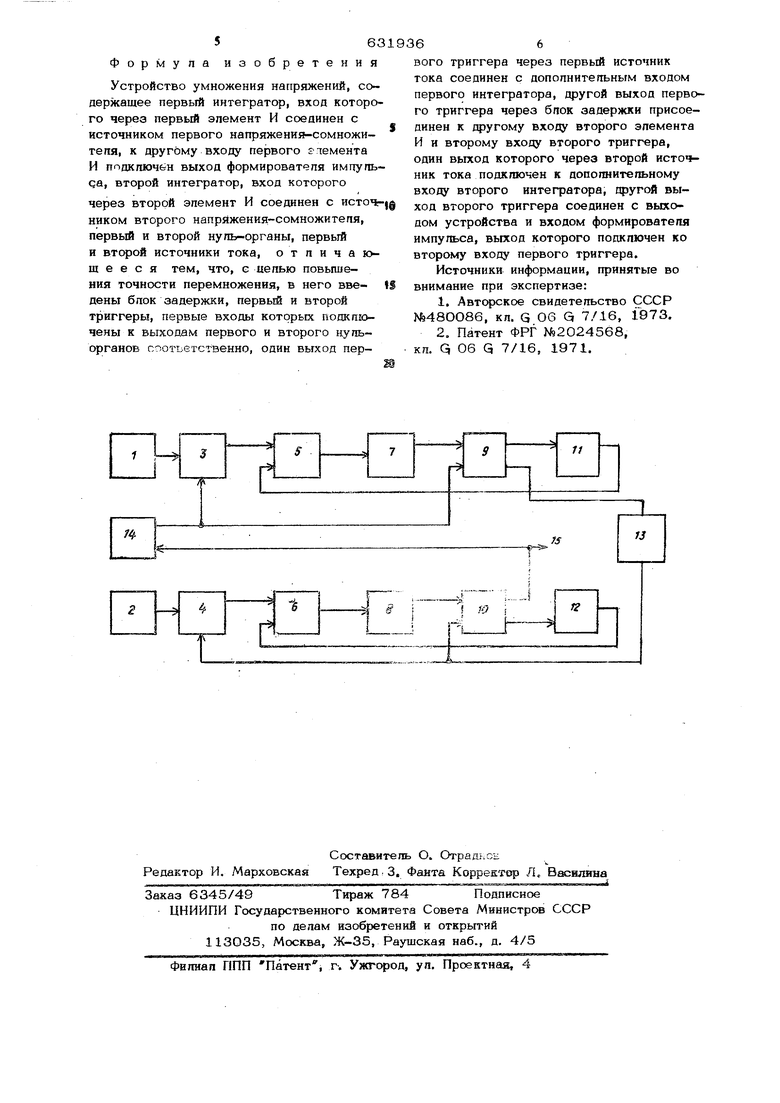

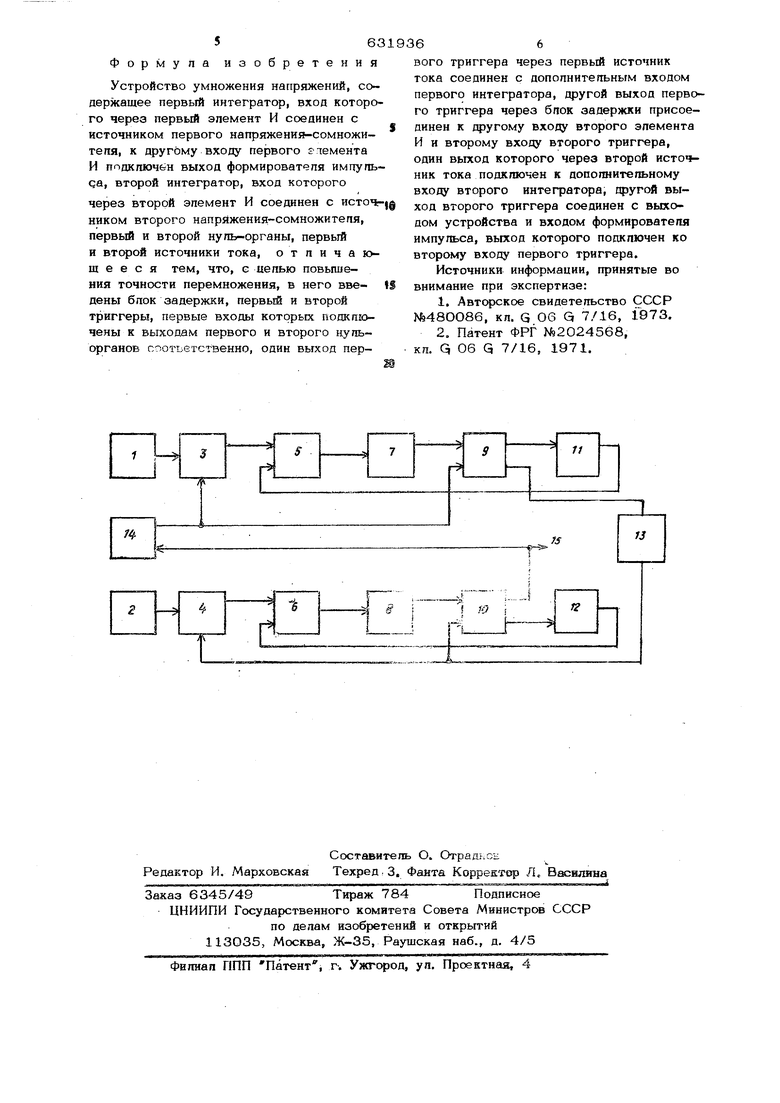

Изобретение касается эпектрических вычиспитеньных устройств и может быть использовано в вычвс/штепьных машинах. Известны устройства, предназначеннью дпя умножения напряжений и содержа щие соединенные последовательно первый источник напряженвя-сомножитепя, ннтегратсф, компаратор н фазочувствитепь №ьЛ выпрямитель, второй источник напряжения-сомножителя P.J. Это устройство характеризуется сравнительно низкой точностью работы. -.. . . , - Наибопёе блвзкнм по технической cyia ности к предложенному является устройст во умножения напряжений, содержащее пер вый интегратор, вход которого через первый элемент И соединен с источником первого напряжения-сомножителя, к пругому входу первого элемента И подКлкь чен выход формирователя импульса, второй интегратор, вход которого через вто рой элемент 41 соединен .с источником второго напряжения-сомножителя, первый R втсфой нулЕ -органьц первый и второй источники тока 121. Это устройство имеет сравнительно большую погрешность перемножения вспвоствие недостаточной линейности каскадов преобразования входных напряжений. Цепью изобретения является повышение точности перемножения. Для этого в него введены блок заоержки, первьЕй н второй триггеры, первые входы которых подключены к выходам первого и второго нульг-органов соответственно, один выход первого триггера через первый источник тока соединен с дополнительным входом первого интегратора, РРУГО& выход первого триггера через блок задержки присоединен к другому входу второго зпел1ента И и второму входу второго триггера, один В1ыход которого через второй источник тока подклх чен к дополнительному входу второго интегратора, выход второго триггера соединен с выходом устройства н входом формирователя импульса, выход подключен ко втсфому входу первого тршпгера. На чертеже изображена структурная схема устройства. Предложенное устройство содержит источники первого и второго напряжений сомножителей 1 и 2, .первый и второй элементы ИЗ и 4, первый и второй ин теграторы 5 и 6, первый и второй нупьорганы 7 и 8, первый и второй триггер 9 и 10, первый и второй источники ток 11 и 12, блок 13 задержки, формирователь 14 импульса, выход 15 устройства. . Устройство работает следующим образом. Формирователь 14 импульса на опре- деленное время открывает первый элеме И 3. Напряжение с выхода источника первого напряжения-сомножителя 1 чере открытый первый элемент ИЗ поступает на вход первого интегратора 5. На выходе первого интегратора 5 формируется напряжение, равное (с точностью до коэффициента передачи) . где и - выходное напряжение первого интегратора 5; и (-t) - напряжение источника первого ВХ I напряжения-сомножителя 1; Т - длительность выходного сигнала формирователя 14 импульса. Задний фронт ВЫХОДНОГЧ5 сигнала формирователя 14 импульса опрокидьгеает .первый ррнггер 9. Напряжение с первог выхода первого триггера 9 поступает н вход первого источника 11 тока,а его выходной сигнал поступает на дополните ный вход первого интегратора 5. С это го момента происходит обнуление пер вого интегратора 5. Время обнуления первог интегратора 5 равно UBX 3, где 3 - ток первого источника 11 тока, равный некоторой постоянной величине. Время обнуленич первого интегратора 5 может быть малым, так как ток первого источника 11 тока превышает ток сигнала. В момент времени, когда выходное напряжение первого интегратора 5 достигает нулевого уровня, срабатьтает первый нуль-орган 7, выходной сигнал которого переведет первый триггер 9 в первоначальное состояние, и ток разряда на второй вход первого интегратора 5 не поступает. Времяобнуления первого интеграора 5 запоминается блоком 13 задержи. Выходное напряжение блока 13 заержки через заранее заданное время которое, может бы1-ь равным и нулю) оступает на управляющий вход второго лемента И 4 и открьтает его. Напряжение с выхода источника второо напряжения-сомножителя через открыый второй эпемант И 4 поступает на ход второго интегратора 6. С точностью о коэффициента передачи выходное напряение второго интегратора 6 равно: ) т, (3) де -напряжение источника второго напряжения-сомножителя 2. Задний фронт выходного напряжения лока 13 задержки опрокидывает второй триггер Ю, выходное напряжение котоого поступает на вход второго источниа 12 тока. Выходной сигнал второго источника 12 тока поступает на дополнительный вход второго интегратора 6 и обнуляет его. Время обнуления второго интегратора 6 равно; «JBXZ (t л./ f где Зд -ток второго источника 12 тока равный некоторой постоянной величине. Очевидно, что: r,,.u,,(). .J ,j В момент равенства выходного напряжения второго интегратора 6 нулевому значению срабатьтает второй нуль-орган 8. Его выходной сигнал переводит второй триггер 1О в первоначальное состошие. Выходное напряжение второго триггера 10 запускает формирователь 14 импульса. Далее цикл работы повторяется. Таким образом, длительность импульса напряжения, снимаемого с выхода второго триггера 10, т. е. на выходе 15 устройства, и определяемая вьфажеиием (5), пропорциональна произведению напряжений. Точность операции умножения зависит от длительности сигнапа формирователя 14 импульса и от величин токов первого и второго источников 11 и 12 тока, параметры которых могут быть стабильными, т. е. устройство, имеет повьпиеиную точHoctb работы.

Формула изобретения

Устройство умножения напряжений, содержащее первый интегратор, вход которого через первый элемент И соединен с источником первого напряжени5 -сомножитепя, к другому входу первого элемента И подкпючб н выход формирователя импульqa, второй интегратор, вход которого

через второй элемент И соединен с источг НИКОМ второго напряжения-сомножителя, первый и второй нуль органы, первый и второй источники тока, отличающееся тем, что, с цепью повышения точности перемножения, в него введены блок задержки, первьй и второй триггеры, первые входы которых подключены к выходам первого и второго нульорганов соотъетственно, один выход первого триггера через первый источник тока соединен с дополнительным входом первого интегратора, другой выход первого триггера через блок задержки присоединен к другому входу второго элемента И и второму входу второго триггера, один выход которого через второй источник тока подкгаочен к допо пните пьному входу второго интегратора, другой выход второго триггера соединен с выходом устройства и входом формирователя импульса, выход которого подключен ко второму входу первого триггера.

Источники информации, принятые во внимание при экспертизе:

1,Автс юкое свидетельство СССР №48ОО86, кл. G Об (3 7/16, 1973.

2.Патент ФРГ №2024568, кп. q 06 Q 7/16, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перемножения напряжений | 1976 |

|

SU599271A1 |

| Устройство для умножения | 1977 |

|

SU686035A1 |

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Частотно-импульсное множительное устройство | 1979 |

|

SU857988A1 |

| Устройство для вычисления синуса и косинуса суммы двух углов | 1980 |

|

SU922788A1 |

| Аналого-цифровое множительное устройство | 1978 |

|

SU769557A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Способ умножения двух сигналов | 1978 |

|

SU748437A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Устройство синхронизации электроразведочных приемников | 1987 |

|

SU1449961A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-08—Подача