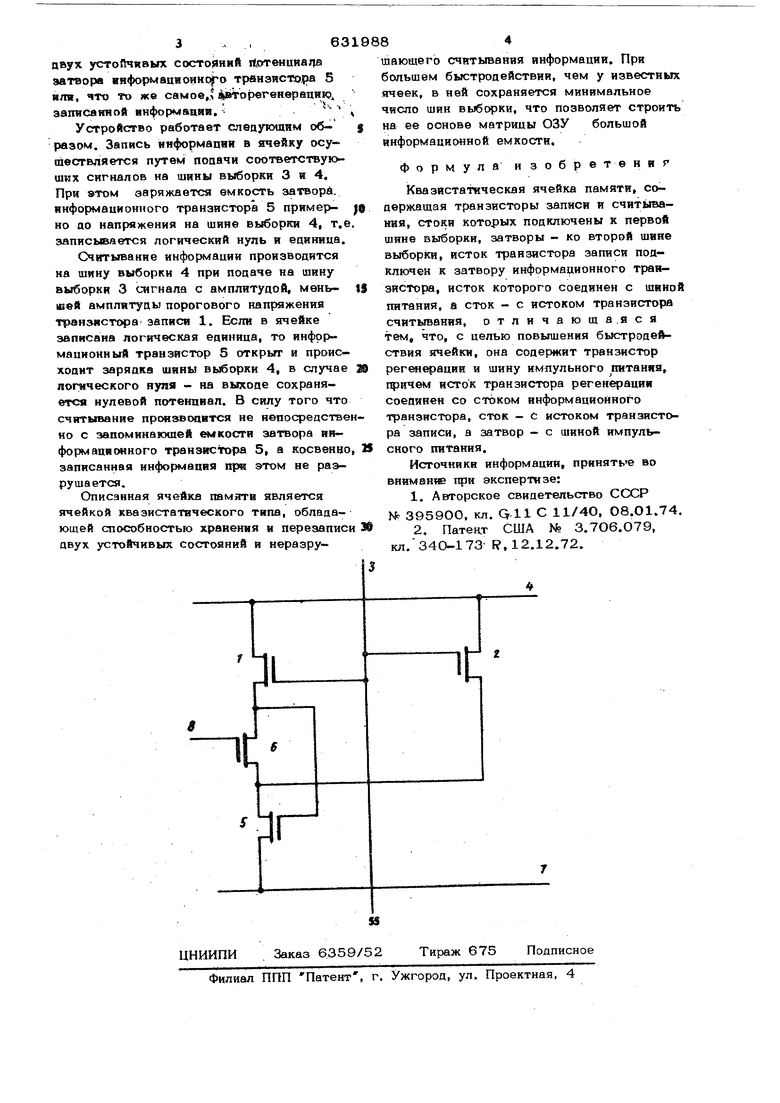

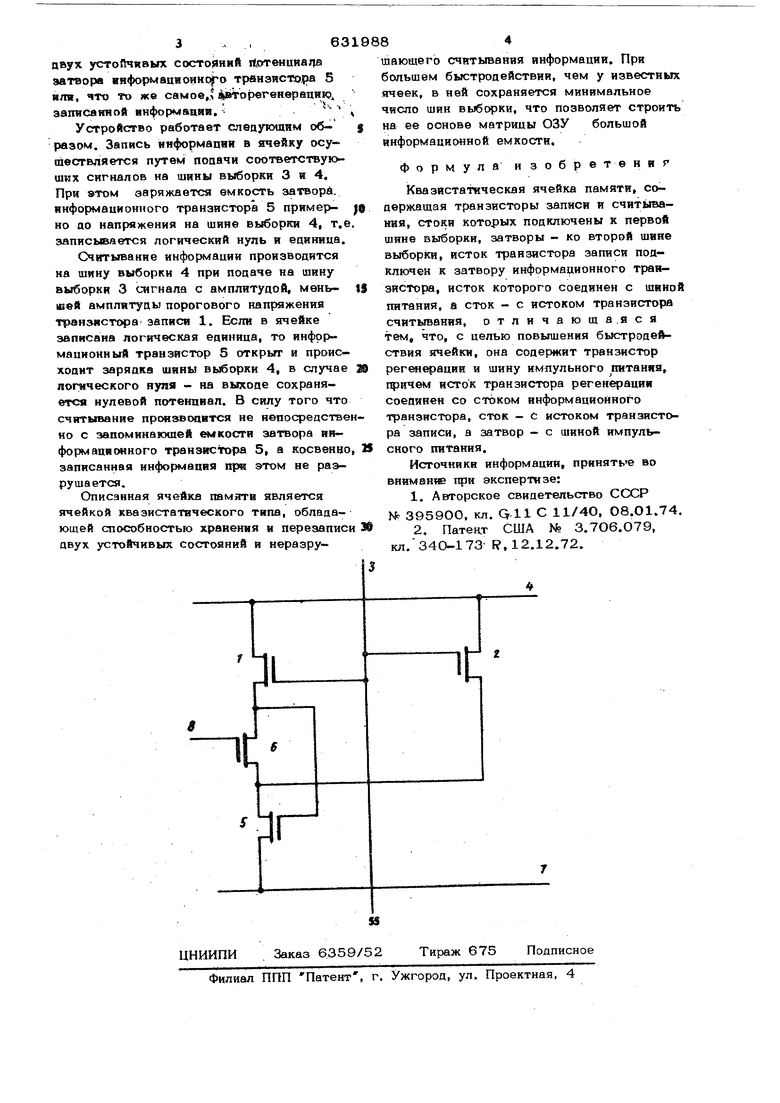

Изобретение относится к вычислител ной технике, в частности к запоминающим устройствам. Известна «сва зистатическая ячейка памяти, выполненная на трех МДП-транзисторах fll . Эта ячейка занимает большую плошадь на подложке и имеет низкое быстродействие. Наиболее близким техническим решеивем к предложенному является квази статическая ячейка памяти, содержащая транзисторы записи и считывания, стоки которых подключены к первой шине выборки, затворы - ко второй шике выбор Исток транзистора записи подключен к затвсфу информационного транзистора, исток которого соединен с шиной питания, а сток - с истоком транзистора считывания J . Эта ячейка также имеет низкое быстродействие из-за необходимости периодической регенерации информации. Цель изобретения - повышение быстр действия ячейки памяти. Указанная цель достигается тем, что ячейка содержит транзистор регенерации и шину импульсного питания, причем исток транзистора регенерации соединен со стоком информационного транзистх ра, сток - с истоком транзистора записи, а затвор - с шиной импульсного питания. На чертеже представлена принципиальная схема 5гчейки памяти. Ячейка содержит транзистор записи 1, транзистор считывания 2, шины выборки 3, 4, информационный транзистор 5, транзистор регенерации 6, шнну питания 7, шину 8 импульсного питания. Транзистор регенерации 6 имеет два уровня порогового напряжения вдзль линии канала. Более высокое значение порогового иапряжения, чем у остальных транзисторов, имеет также транзистор записи 1. Часть ячейки памяти, включающая в себя информационный транзистор 5 и транзистор регенерации 6, при наличии питающих напряжений, приложенных к шинам 7, 8| обеспечивает поцдержанне

двух устойчивых состояний «(отенциапа затворе внформаавоннс|о транзисто.)а 5 нля, что чх же самое, а Ьрегенерапию затгасйиной информации.-,

Устройство работает следующим образом. Запись информапян в ячейку осуществляется путем поаачи соответс-геукушмх сигналов на шины выборки 3 н 4. При этом ааряжается емкость затвори, информационного транзистора 5 примерно до напряжения на шине выборки 4, т.е записьюается логический нуль и ецнница.

Считывание информации производится на шину выборки 4 при подаче на шину выборки 3 сигнала с амплитудой, меньшей амплитудь порогового напряжения транзистора записи 1. Если в ячейке звписана логическая единица, то иифр()мационный транзистор 5 открыт и происходит зарядка шины выборки 4, в случае логического нуля - на выходе сохраняется нулевой потенпиал. В силу того что считывание произвоовтся не непосредствено с запоминающей емкости затвора ийформацнонного транзистора 5, а косвенно записанная информация при этом не разрушается.

Описанная ячейка памяти является ячейкой квазнстатвческого типа, обладающей способностью хранения и перезаписи двух устойчивых состояний и неразрушающего считывания информации. При большем быстродействии, чем у известны ячеек, в ней сохраняется минимальное число шин выборки, что позволяет строит на ее основе матрицы ОЗУ большой информационной емкости.

Формула изобретениг

Квазистатическая ячейка памяти, содерншщая транзисторы записи и счит ования, стоки которых подключены к первой шине выборки, затворы - ко второй шине выбор1П1, исток транзистора записи подключен к затвору информационного транзистора, исток которого соединен с шино питания, а сток - с истоком транзистора считывания, отлнчающа.яся тем, что, с целью повышения быстродействия ячейки, она содержит транзистор рег«1ерации и шину имлульного питания, щэичем исток транзистора регенерации соединен со стоком информационного транзистора, сток - с истоком транзистора записи, а затвор - с шиной импульсного питания.

Источники информации, принятье во внимание при экспертизе:

1.Авторское свидетельство СССР

№ 395900. кл. Q 11 С 11/4О, 08.О1.74

2.Патент США № 3,7О6.О79, кл.340-173- R, 12.12.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Ячейка памяти | 1982 |

|

SU1327187A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

1

S

зг

t

Авторы

Даты

1978-11-05—Публикация

1976-05-17—Подача