Изобретение относится к вычислительной технике и может быть использовано для создания интегральных схем энергонезависимых оперативных запоминающих устройств (ЭОЗУ) большой информационной емкости, способных производить обмен информацией между оперативной и долговременной памятью, сохранять информацию ОЗУ после отключения питания, запоминать промежуточную информацию ОЗУ или же содержать энергонезависимую, электрически сменяемую подпрограмму,например, в микропроцессорных и других системах.

Целью изобретения является упрощение ячейки памяти.

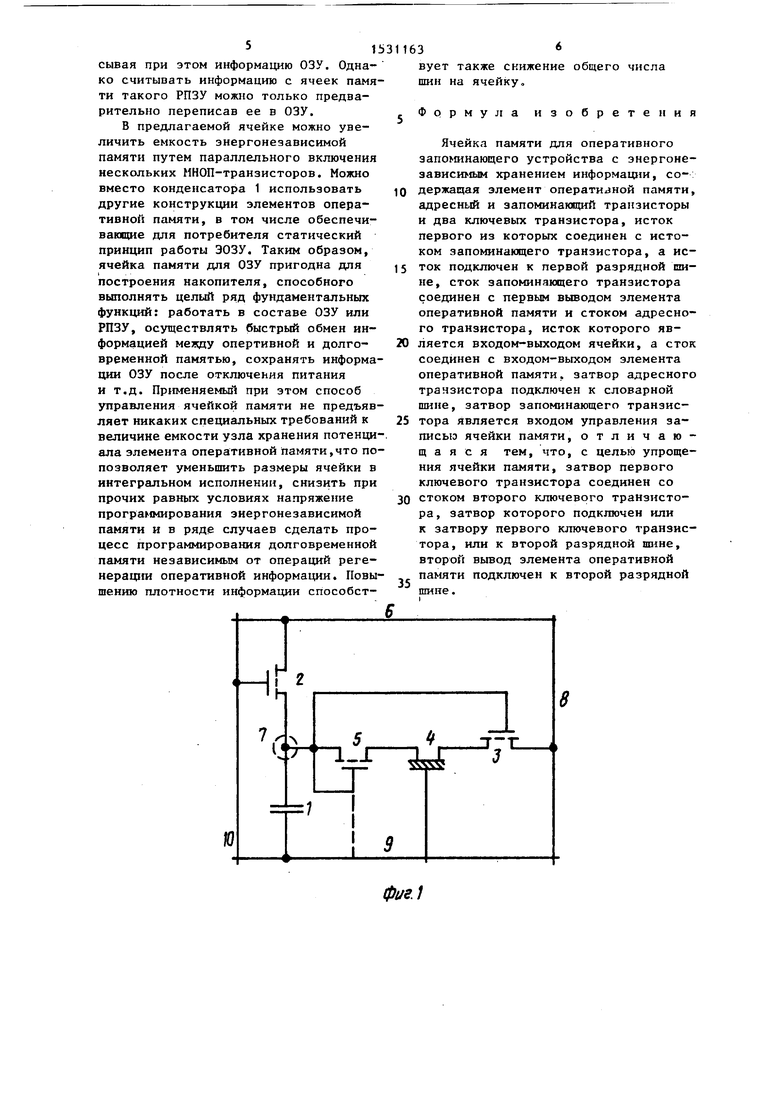

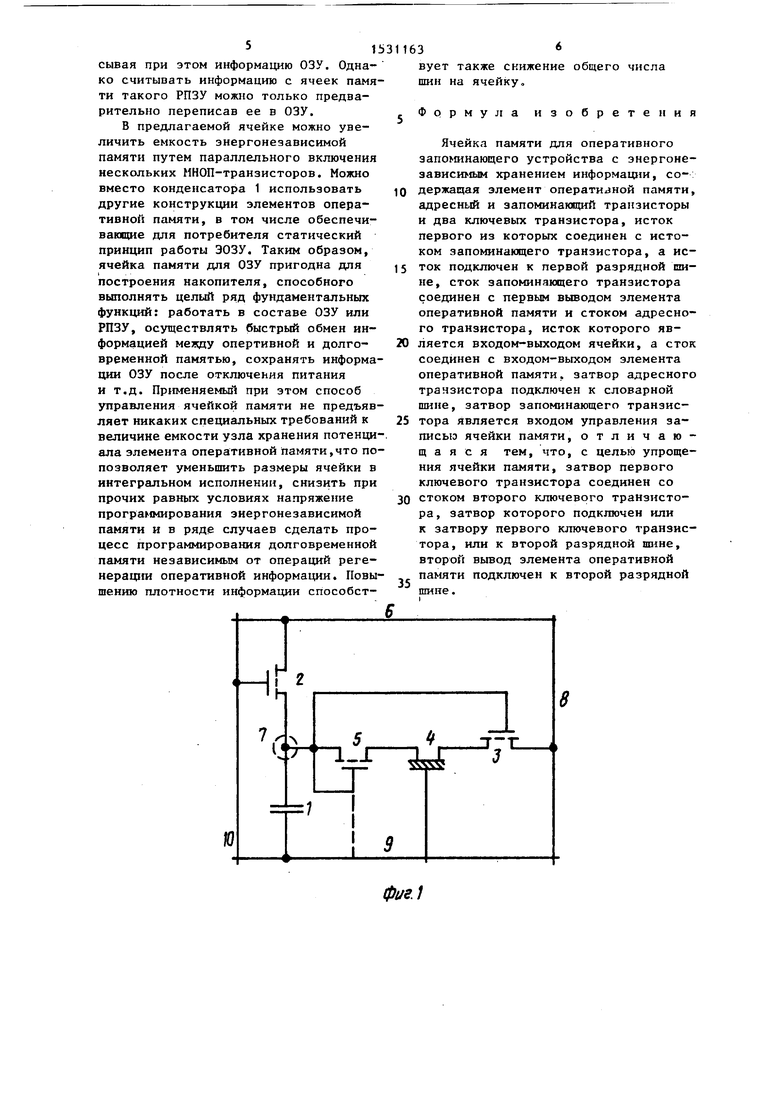

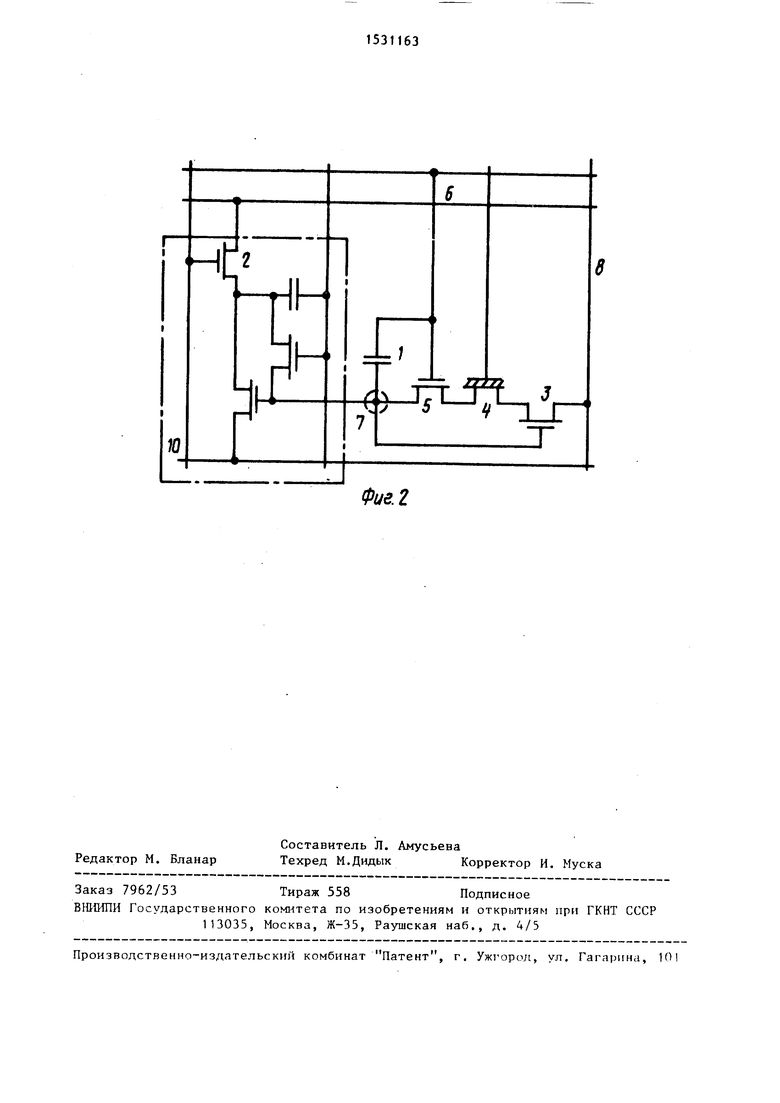

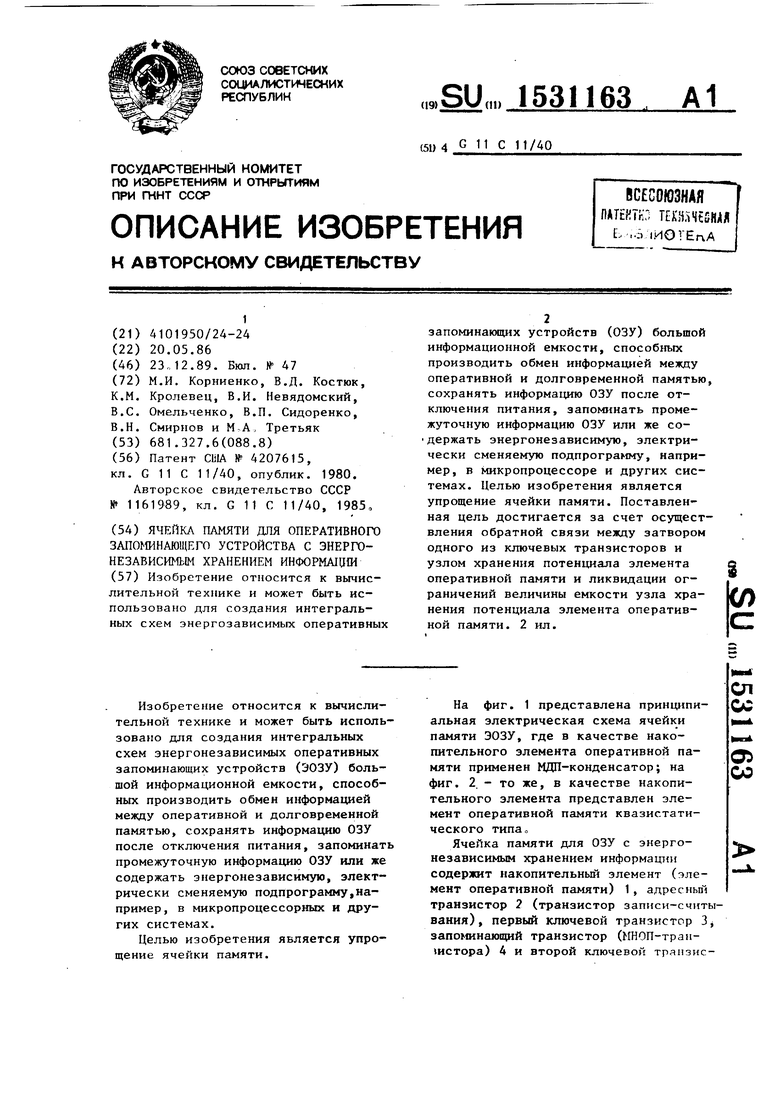

На фиг. 1 представлена принципиальная электрическая схема ячейки памяти ЭОЗУ, где в качестве накопительного элемента оперативной памяти применен МДП-конденсатор; на фиг. 2. - то же, в качестве накопительного элемента представлен элемент оперативной памяти квазистатического типа

Ячейка памяти для ОЗУ с энергонезависимым хранением информации содержит накопительный элемент (элемент оперативной памяти) 1, адресньш транзистор 2 (транзистор записи-считывания), первый ключевой транзистор 3 запо шнающий транзистор (МИОП-тран- шстора) 4 и второй ключевой трапзнсСЛ

ОС

О) со

тор 5. При этом вход транзистора 2 по подключен к числовой шине 6, а выход соединен с узлом 7 хранения потенциала элемента 1 оперативной памяти.

Вход первого ключевого транзистора 3 подключен в общем случае к первой разрядной шине 8, а затвор - к узлу 7 хранения потенциала элемента 1 опера- тивной памяти, к которому также подключен выход и затвор второго ключевого транзистора 5, причем затвор может быть подключен к второй разрядной пшне 9, имеющей емкостную связь с уз- лом 7 хранения потенциала элемента 1 оперативной памяти. Затвор транзистор 2 подключен к словарной шине 10.

Предлагаемая ячейка может )аботать в качестве ячейки памяти ОЗУ без ка- ких бы то ли было ограничений, присущих энергонезависимой памяти, поскольку элементы энергонезависимого хранения информации вынесены за пределы узлов оперативной обработки данных И не влияют на вьтолнение последними своих исходных функций. Кроме того,, ячейка способна переносить информацию из элемента 1 оперативной памяти в МНОП-транзистор 4. Для этого возбуждают напряжение 20-25 В затвор МНОП- транзистора 4 и обнуляют разрядную шину 8. Если элемент 1 оперативной памяти хранит логическую 1, т.е. потенциал, примерно, равнш 5 В, то транзистор 3 открыт, а транзистор 5 закрыт (для определенности рассматривают схему подключения затвора транзистора 5 к узлу хранения потенциала, вьтолненную на п-канальных транзисторах с пороговым напряжением 0,5 В), тогда область канала МНОП-транзистора приобретет потенциал шины 8, т.е. О В результате, поскольку все затворное напряжение транзистора 4 падает на его подзатворном диэлектрике, МНОП транзистор 4 приобретает второе по отношению к исходному логическое состояние с высоким уровнем порогового напряжения, например 8 В. Если элемент 1 оперативной памяти хранит логический О, т.е. близкий к нулю потенциал, то ключевые транзисторы 3 и 5 закрыты, и практически все напряжение, приложенное к затвору МНОП- транзистора 4, падает в подложке на области пространственного заряда, и МНОП-транзистор 4 сохраняет свое исходное логическое состояние с низ

5

5

0

0

5

0

5

0

5

КИМ, например 0,5 В, уровнем порогового напряжения„

Ячейка осуществляет обратный перевод информации из энергонезависимой памяти в оперативную, т.е. производить обратную запись. Для этого вначале через адресный транзистор 2 заряжают узел 7 хранения потенциала до уровня, соответствукнцего хранению логической 1 (5 Б), и устанавливают на затворе МРЮП-транзистора 4 напряжение, величина которого находится внутри его межпороговой зоны, т.е. тоже л 5 В, а зарядную шину 8 обнуляют. При этом, если МНОП-транзистор 4 находится в первом логическом состоянии (с исходным пороговым напряжением 0,5 В), то он, как и ключевые транзисторы 3 и 5, закрыт и узел 7 хранения потенциала разряжается, т.е. в элемент 1 оперативной памяти записывается логический О.Если МНОП-транзистор 4 находится во втором логическом состоянии, то элемент 1 оперативной памяти сохраняет свою логическую 1..

Следовательно, при обратной записи информация, записанная ранее в МНОП-транзисторе 4, не инвертируется.

Дополнительные удобства в работе накопителя энерго11езависимого ОСУ можно nnnVii ib, если разрядную шину 8 использовать для запрета перезаписи информации из элемента 1 оперативной памяти в элемент энергонезависимой памяти и обратно в ячейках памяти невыбранных строк или столбцов матрицы.

Предлагаемая ячейка также способна производить стирание долговременной информации. Для этого на системе затвор-подложка МНОП-транзистора создают разность потенциалов обратной полярности по отношению к записи. Ячейка может работать в качестве ячейки памяти электрически репрограм- мируемого ПЗУ (РПЗУ). При этом РПЗУ приобретает важное преимущество ло сравнению с классическим РПЗУ: время его программирования уменьшается во столько раз, какова информационная емкость РПЗУ. Например, для емкости 16Кбит X 1, запись проводят быстрее в 1,6 «Ю раз.

Это становится возможным благодаря тому, что вдесь все МНОП-транзисторы накопителя могут программироваться параллельно одним импульсом, переписывая при этом информацию ОЗУ, Однако считывать информацию с ячеек памяти такого РПЗУ можно только предварительно переписав ее в ОЗУ.

В предлагаемой ячейке можно увеличить емкость энергонезависимой памяти путем параллельного включения нескольких МНОП-транзисторов. Можно вместо конденсатора 1 использовать другие конструкции элементов оперативной памяти, в том числе обеспечи- ватцие для потребителя статический принцип работы ЭОЗУ. Таким образом, ячейка памяти для ОЗУ пригодна дпя построения накопителя, способного выполнять целый ряд фундаментальных функций: работать в составе ОЗУ или РПЗУ, осуществлять быстрый обмен информацией между опертивной и долговременной памятью, сохранять информации ОЗУ после отключения питания и т.д. Применяемый при этом способ управления ячейкой памяти не предъявляет никаких специальных требований к величине емкости узла хранения потенци ала элемента оперативной памяти,что по позволяет уменьшить размеры ячейки в интегральном исполнении, снизить при прочих равных условиях напряжение программирования энергонезависимой памяти и в ряде случаев сделать процесс программирования долговременной памяти независимым от операций регенерации оперативной информации. Повышению плотности информации способствует также снижение общего числа шин на ячейку,

Формула изобретения

Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации, содержащая элемент оперативной памяти, адресный и запоминакядий транзисторы и два ключевых транзистора, исток первого из которых соединен с истоком запоминающего транзистора, а исток подключен к первой разрядной шине, сток запоминающего транзистора соединен с первым выводом элемента оперативной памяти и стоком адресного транзистора, исток которого является входом-выходом ячейки, а сток соединен с входом-выходом элемента оперативной памяти, затвор адресного транзистора подключен к словарной шине, затвор запоминающего транзистора является входом управления записью ячейки памяти, отличающаяся тем, что, с целью упрощения ячейки памяти, затвор первого ключевого транзистора соединен со

стоком второго ключевого транзистора , затвор которого подключен или к затвору первого ключевого транзистора, или к второй разрядной шнне, второй вывод элемента оперативной памяти подключен к второй разрядной

шине.

I

; i

IH

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1308063C |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания | 1989 |

|

SU1697118A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания интегральных схем энергонезависимых оперативных запоминающих устройств (ОЗУ) большой информационной емкости, способных производить обмен информацией между оперативной и долговременной памятью, сохранять информацию ОЗУ после отключения питания, запоминать промежуточную информацию ОЗУ или же содержать энергонезависимую, электрически сменяемую подпрограмму, например, в микропроцессоре и других системах. Целью изобретения является упрощение ячейки памяти. Поставленная цель достигается за счет осуществления обратной связи между затвором одного из ключевых транзисторов и узлом хранения потенциала элемента оперативной памяти и ликвидации ограничений величины емкости узла хранения потенциала элемента оперативной памяти. 2 ил.

i

h

I ;

Фиг. 2

| Патент ClilA № 4207615, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-23—Публикация

1986-05-20—Подача