Изобретение относится к вычислительной технике и может быть использовано для создания интегральных схем статических оперативных запоминающих устройств с произвольной Bbt

боркой, построенных на ЩП-приборах

Целью изобретения является увеличение быстродействия ячейки памяти.

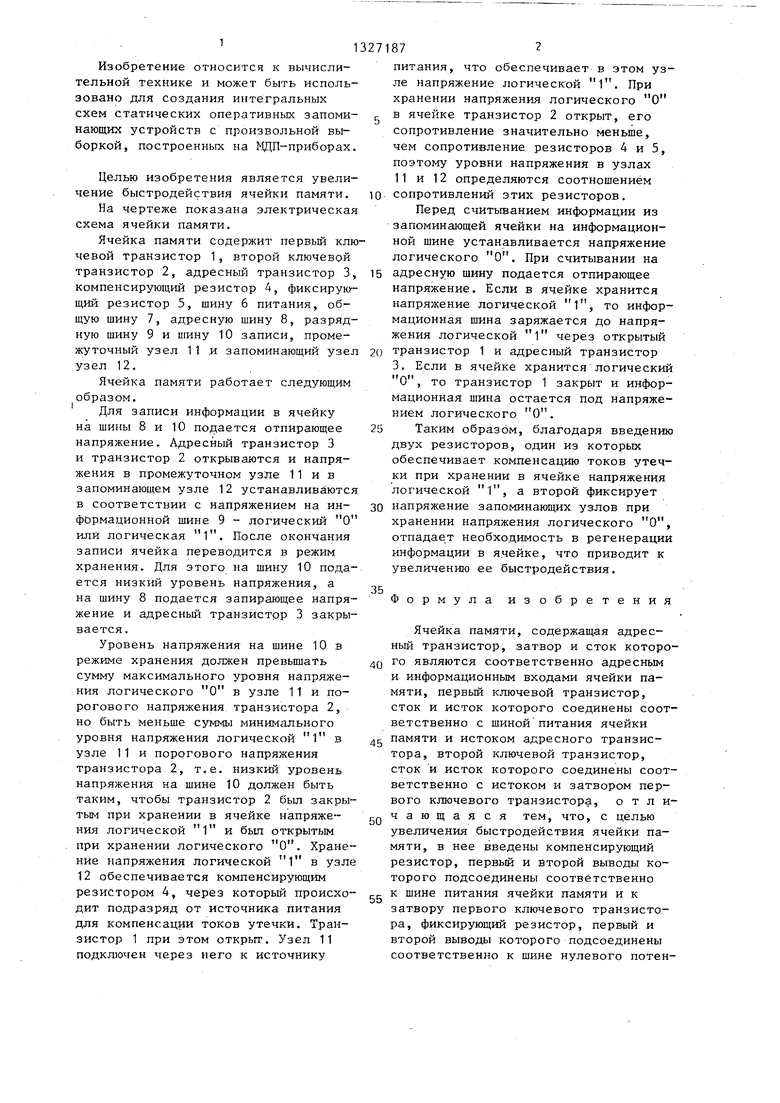

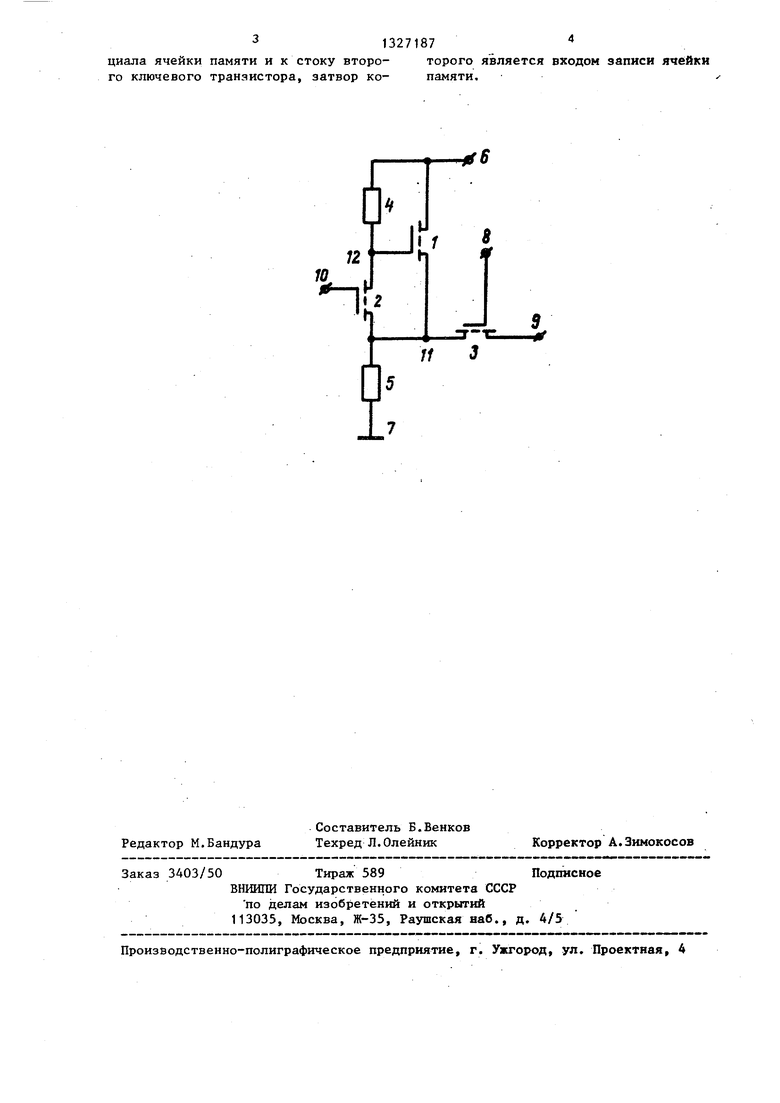

На чертеже показана электрическая схема ячейки памяти.

Ячейка памяти содержит первый ключевой транзистор 1, второй ключевой транзистор 2, адресный транзистор 3, компенсирующий резистор 4, фиксирующий резистор 5, шину 6 питания, общую шину 7, адресную шину 8, разрядную шину 9 и шину 10 записи, промежуточный узел 11 .и запоминающий узел узел 12.

Ячейка памяти работает следующим образом.

Для записи информации в ячейку на шины 8 и 10 подается отпирающее напряжение. Адресный транзистор 3 и транзистор 2 открываются и напряжения в промежуточном узле 11 и в запоминающем узле 12 устанавливаются в соответствии с напряжением на информационной шине 9 - логический О или логическая 1. После окончания записи ячейка переводится в режим хранения. Для этого на шину 10 подается низкий уровень напряжения, а на шину 8 подается запирающее напряжение и адресный транзистор 3 закрывается .

Уровень напряжения на шине 10 в режиме хранения должен превътать сумму максимального уровня напряжения логического О в узле 11 и порогового напряжения транзистора 2, но быть меньше суммы минимального уровня напряжения логической 1 в узле 11 и порогового напряжения транзистора 2, т.е. низкий уровень напряжения на шине 10 должен быть таким, чтобы транзистор 2 был закрытым при хранении в ячейке напряжения логической 1 и был открытым при хранении логического О. Хранение напряжения логической 1 в узле 12 обеспечивается компенсирующим резистором 4, через который происходит подразряд от источника питания для компенсации токов утечки. Транзистор 1 при этом открыт. Узел 11 подклю ген через него к источнику

питания, что обеспечивает в этом узи О

ле напряжение логической 1. При

хранении напряжения логического

в ячейке транзистор 2 открыт, его сопротивление значительно меньше, чем сопротивление резисторов 4 и 5, поэтому уровни напряжения в узлах 11 и 12 определяются соотношением

сопротивлений этих резисторов.

Перед считьгоанием информации из запоминающей ячейки на информационной шине устанавливается напряжение логического О. При считывании на

адресную шину подается отпирающее напряжение. Если в ячейке хранится напряжение логической 1, то информационная шина заряжается до напряжения логической 1 через открытый

транзистор 1 и адресный транзистор 3. Если в ячейке хранится логический О, TO транзистор 1 закрыт и информационная шина остается под напряжением логического О.

Таким образом, благодаря введению двух резисторов, один из которых обеспечивает компенсацию токов утечки при хранении в ячейке напряжения логической 1, а второй фиксирует

напряжение запоминающих узлов при хранении напряжения логического О, отпадае,т необходимость в регенерации информации в ячейке, что приводит к увеличению ее быстродействия.

Формула изобретения

Ячейка памяти, содержащая адресный транзистор, затвор и сток которого являются соответственно адресным и информационным входами ячейки памяти, первый ключевой транзистор, сток и исток которого соединены соответственно с шиной питания ячейки памяти и истоком адресного транзистора, второй ключевой транзистор, сток и исток которого соединены соответственно с истоком и затвором первого ключевого транзистора, отличающаяся тем, что, с целью увеличения быстродействия ячейки памяти, в нее введены компенсирующий резистор, первый и второй выводы которого подсоединены соответственно к шине питания ячейки памяти и к затвору первого ключевого транзистора, фиксирующий резистор, первый и второй выводы которого подсоединены соответственно к шине нулевого потен

31327187

циала ячейки памяти и к стоку второ- торого является входом записи ячейки го ключевого транзистора, затвор ко- памяти.

72 - h

Ч

ор М.Бандура 3403/50

Составитель Б.Венков Техред Л. Олейник

Тираж 589 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корр Подпи

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

h

i

I

11 J

Корректор А.Зимокосов Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания интегральных схем статических запоминающих устройств с произвольной выборкой на МДП-транзисторах, Целью изобретения является увеличение быстродействия ячейки памяти. Поставленная цель достигается тем, что в ячейку памяти введены компенсирующий резистор, первый и второй выводы которого подсоединены соответственно к шине питания и к затвору первого ключевого транзистора,фиксирующий резистор, первый и второй выводы которого подсоединены соответственно к общей шине и к стоку второго ключевого . транзистора, затвор которого соединяется с шиной записи. 1 ил. С/) С

| Патент США № 4030083, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-30—Публикация

1982-06-08—Подача