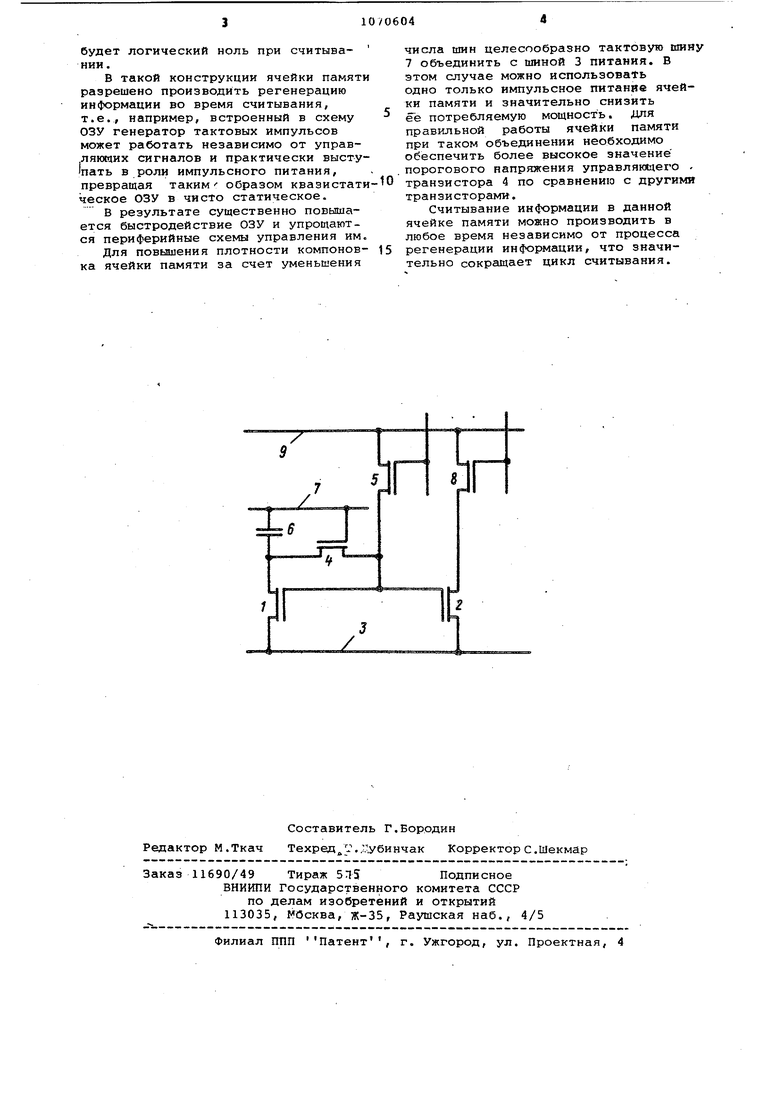

Изббретение относится к вычислительной технике и может быть использовано для создания полупроводникрг вых операционных запоминающих устройств статического типа, обладающих повышенной информационной емкостью, Известна конструкция ячейки памяти квазистатического пгипа, построенная на основе МДП структур. Ячейка обладает меньшим количеством элементов по сравнению с классической триг герной, конструкцией, поэтому на ее основе может быть получена более высокая информационная емкость ОЗУ в интегральном исполнении fl. Однако требование периодической регенерации в них информации, котора осуществляется одним внешним импульсом во всех ячейках накопителя ОЗУ одновременно, хотя и в меньшей степе ни, чем в динамических схемах, но ведет к потере части полезного време ни работы ОЗУ. Наиболее . близкой по технической сущности и схемному решению к предла гаемой является ячейка памяти, содер жащая ключевой, запоминающий и управ ляющий транзисторы, конденсатор. Регенерация информации осуществляетс синхронизацией тактового импульса с импульсом считывания 2, Недостатком указанной ячейки явля .ется невысокое быстродействие, связанное с тем, что цикл считывания в такой ячейке увеличивается на длину тактового импульса.. Цель изобретения - повышение бысородействия ячейки памяти. Поставленная цель достигается тем, что ячейка памяти, содержащая первый ключевой транзистор, затвор и исток которого являются соответственно первым и вторым входами ячейки запоминагадий транзистор, сток которо го подключен к шине питания, управля транзистор, исток которого соединен с затвором запоминающего тран зистора, конденсатор, одна обкладка которого соединена с затвором управ ляющего транзистора и подключена к тактовой шине, другая обкладка конденсатора соединена со стоком управляю1дего транзистора и истоком запомн нающего транзистора, дополнительно содержит второй ключевой транзистор и усилительный транзистор, затвор которого, соединен с затвором запоминагацего транзистора, его сток соединен с шиной -питания, а исток соеди нен со,стоком второго ключевого тран зистора, исток и затвор которого являются соответственно третьим и четвертым BxoflaNm ячейки, сток перво го ключевого транзистора соединен с истоком или стоком управляющего ;транзистора. Согласно второму варианту ячейка амяти,содержащая первый ключевой транзистор, затвор и исток которого являются соответственно первым и вторым входами ячейки,запоминающий транзистор, сток которого подключен к тактовой шине, управляющий транзистор, исток которого соединен.с затвором запоминающего транзистора, конденсатор, одна обкладка которого соединена с затвором управляющего транзистора и подключен к тактовой шине, другая обкладка конденсатора соединена со стоком управляющего транзистора и истоком запоминающего транзистора, дополнительно содержит второй ключевой транзистор и усилительный транзистор, затвор которого соединен с затвором запоминающего транзистора, его сток соединен с тактовой шиной, а исток соединен со .стоком второго ключевого транзистора, исток и затвор которого являются соответственно третьим и четверТЕЛм входами ячейки, сток первого .ключевого транзистора соединен с истоком или.стоком управляющего транзистора. На чертеже представлена принципиальная электрическая схема ячейки по первому варианту Ячейка памяти содержит запоминающий 1 транзистор, сток которого соединен со стоком усилительного 2 транзистора., и является шиной 3 питания, ячейки, затвор запоминающего 1 транзистора соединен с затвором усилительного 2 транзистора, истоком управляющего 4 транзистора и стоком первого 5 ключевого транзистора, одна рбкладка конденсатора 6 соединена с затвором управляющего 4 транзистора, сток которого соединен с другой обкладкой конденсатора б и истоком запоминающего 1 транзистора, затвор управляквдегб 4 транзистора соединен с тактовой 7 шиной, исток усилительного 2 транзистора соединен со стоком второго 8 ключевого транзистора, истоки первого 5 и второго 8 ключевых транзисторов соединены с разрядной 9 шиной, затворы первого 5 :и второго 8 ключевых транзисторов являются адресными входами ячейки. Ячейка работает следутацим образом. Запись информации в ячейку осуществляют через транзистор 5. Считывание информации производят через транзисторы 2 и 8. Если в ячейке хранится логическая единица, то транзистор 2 будет открыт и цепь считывания также будет открыта. Напряженле питания с шины 3 через транзисторы 2 и 8 поступает на разрядную шину 9. Если в ячейке хранится логический ноль, то транзистор 2 будет закрыт и на разрядной шине 9. будет логический ноль при считывав такой конструкции ячейки памят разрешено производить регенерацию информации во время считывания, т.е., например, встроенный в схему ОЗУ генератор тактовых импульсов может работать независимо от управяющих сигналов и практически высту пать в роли импульсного питания, превращая таким образом квазистат ческое ОЗУ в чисто статическое. В результате существенно повышается быстродействие ОЗУ и упрощаются периферийные схемы управления им Для повышения плотности компоновка ячейки памяти за счет уменьшения числа шин целесообразно тактовую шину 7 объединить с шиной 3 питания. В этом случае можно использовать одно только импульсное питанве ячейки памяти и значительно снизить ее потребляемую мощность. Для правильной работы ячейки памяти при таком объединении необходимо обеспечить более высокое значение порогового напряжения управляющего . транзистора 4 по сравнению с другими транзисторами. Считывание информации в дайной ячейке памяти можно производить в любое время независимо от процесса регенерации информации, что значительно сокращает цикл считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

1. Ячейка памяти, содержащая первый ключевой транзистор,затвор и исток которого являются соответственно первым и вторым входами ячейки, запоминающий транзистор, сток которого подключен к шине питания, управляющий транзистор, исток которого соединен с затвором запоминающего транзистора, конденсатор, одна обкладка которого соединена с затвором управляющего транзистора и подг ключена к тактовой шине, другая обкладка конденсатора соединена со стоком управлянвдего транзистора и истоком запоминающего транзистора,о тличающаяся тем, что, с целью повышения быстродействия ячейки, она содержит второй ключевой транзистор и усилительный транзистор, затвор- которого соединен с затвором запоминающего транзистора, его сток .соединен с шиной питания, а исток соединен со стоком второго ключевого транзистора, исток и затвор которого являются соответственно третьим и четвертым входами ячейки, сток первого ключевого транзистора соединён с истоком или стоком управляющего транзистора. 2. Ячейка памяти, содержащая первый ключевой транзистор, затвор и исток которого являются соответственно первым и вторым входом ячейки, запоминанхций транзистор, сток которого подключен к тактовой шине, управляющий транзитор, исток которого соединен с затвором запоминающего транзистора,конденсатор, одна обкладка которого соединена с затвором управляк цего транзистора и подключе на к тактовой шине, другая обкладка л конденсатора соединена со стоком управляющего транзистора и истоком с: запоминающего транзистора, отличающаяся тем, что, с целью повышения быстродействия ячейки, она содержит второй ключевой транзистор и усилительный транзистор, затвор которого соединен с затвором запоминаннцего транзистора, его сток соедиN нен с тактовой шиной, а исток соедио о нен со стоком второго ключевого транзистора, исток и затвор которого являются соответственно третьим и четвертым входами ячейки, сток пер4 вого ключевого транзистора соединен t истоком или стоком управляющего Ьранзистрра. .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент CWA № 3878404, кл.а 11 С 11/40, опублик | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

Авторы

Даты

1984-01-30—Публикация

1982-03-29—Подача