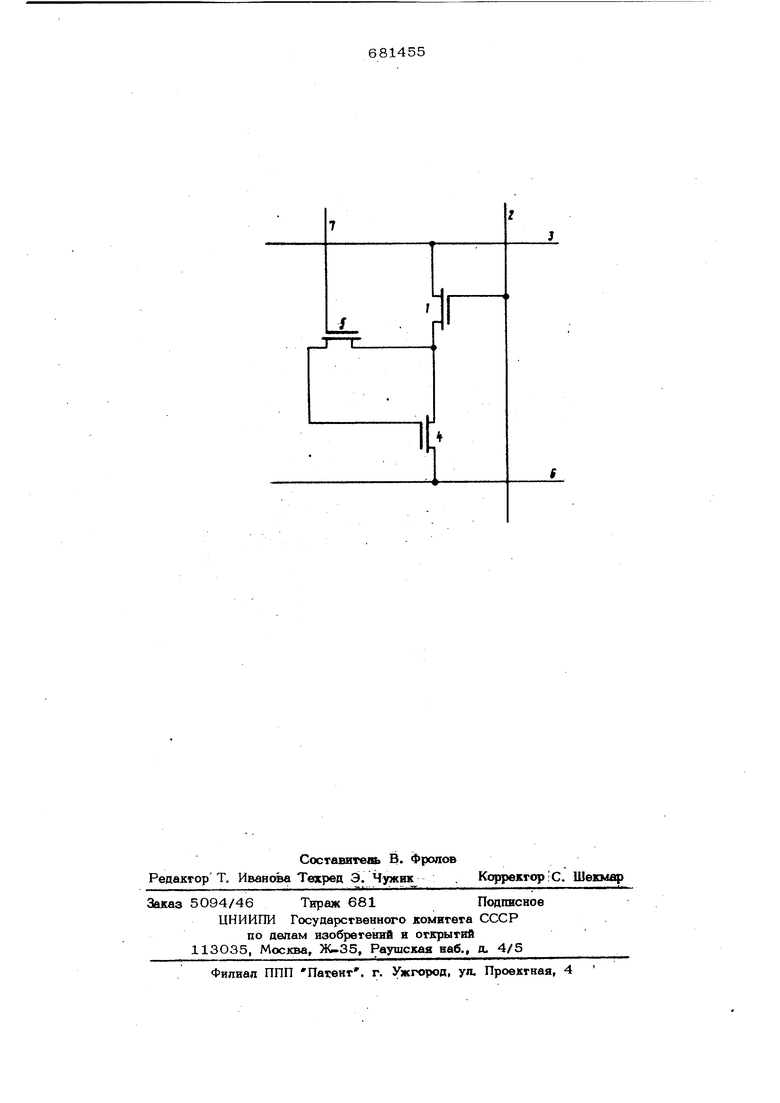

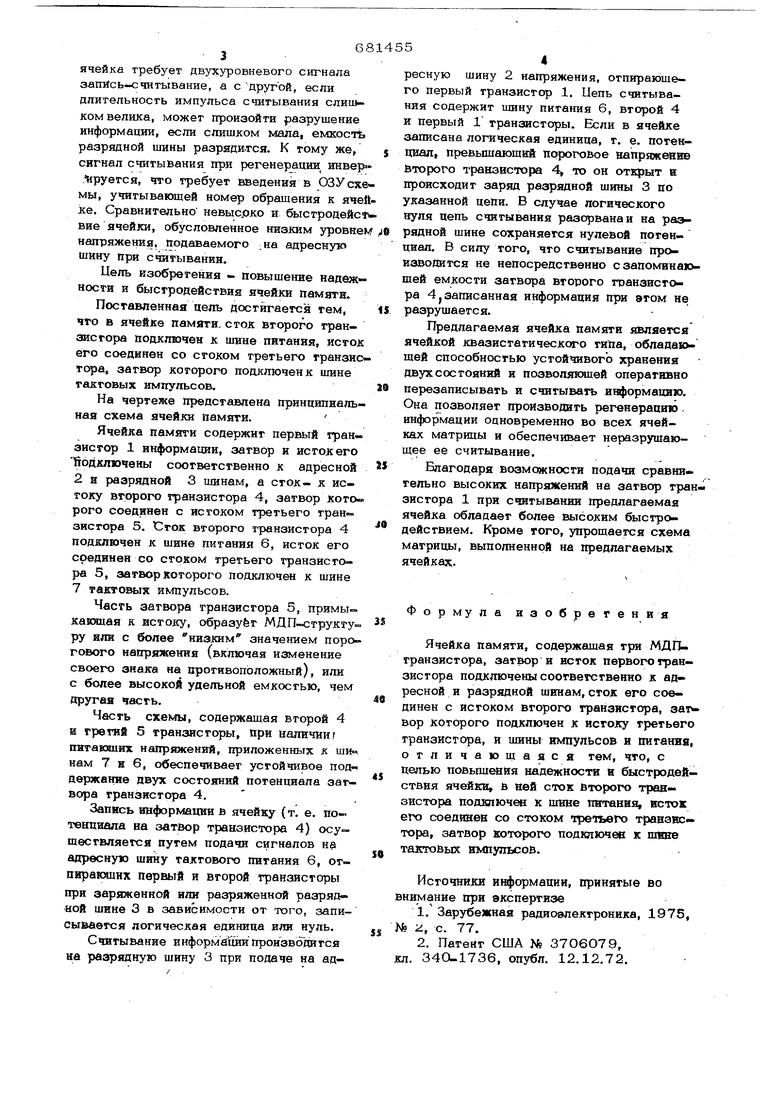

Изобретенне относится к вычвспитвпьBoft технике, & частности к запоминающим устройствам. Известны ячейки памяти, построенные на основе МДП.;труктур, с двумя шинами Выборки, например одвотранаисторная ячейка памяти, содержащая ключевой МДП транзистор с присоединенной к его истоку емкостью 1|. Малое количество элементов и минимальное число шин позволяв ют достигнуть Высокую плотность ячеек на кристалле. Однако в этом устройстве считываввв информации производится непосредсгвенно с запоминающей емкости, без усиления CHt нала в самой ячейке, что влечет за собой необходимость Ьолучения нсялинаяа этой емкости, соизмеримого с емкостью ра рядной шины магрииы. Причем, чем боль ше матрица, тем болыией долягаа быть ата емкость, и при прочих равных условиях тем больше размер ячейки и меньше ее быстродействие. Кроме того, однотранзисторная ячейка требует сложной организации обрамления , матрицы, связанной с усилением считываемого потенциала и разрушением информации при считывании. Наиболее близким по технической сушности к предлагаемой является ячейка памяти, содержащая три МДГигранзистора, затвор и исток первого транзистора подключены соответственно к адресной и разрядисй шинам, сток его соединен с истоком второго транзистора, затвор которого подключен к истоку третьего транзистора и шины тактовых импульсов и питания 2. Кроме обшего для всех ячеек памяти динамического типа и матриц на кх основе недостатка, связанного с необходимостью периодического последовательного опроса и регенерации записанной в них информации, когда ОЗУ работает только само на себя, указанная ячейка имеет еше ряд иедостсцков. Величины напряжений и временные интервалы при считывании у нее критичны: с одной стЬроны, такая ячейка требует двухуровневого сигнала запись-считывание, а с другой, если длительность импульса считывания слишком велика, может произойти разрушение информации, если слишком мала, емкость разрядной шины разряди-тся. К тому же, сигнал считывания при регенерации инвер ируется, что требует введения в ОЗУ сх мы, учитывающей номер обращения к яче ке. Сравнительно невыс эко и быстродейс вне ячейки, обусловленное низким уровне напряжения, подаваемого -на адресную шину при считывании. Цель изобретения повышение надежности и быстродействия ячейки памяти. Поставленная цель достигается тем, что в ячейке памяти, сток второго транзистора подключен к шине питания, исток его соединен со стоком третьего транзис гора, затвор которого подключен к шине тактовых импульсов. На чертеже представлена принципиаль ная схема ячейки памяти. Ячейка памяти содержит первый транзистор 1 информации, затвор и исток его йодключены соответственно к адресной 2 н разрядной 3 шинам, а сток- к истоку второго транзистора 4, затвор кото рого соединен с истоком третьего транзистора 5. Сток второго транзистора 4 подключен к шине питания 6, исток его соединен со стоком третьего транзистора 5, затвор которого подключен к шине 7 тактовых импульсов. Часть затвора транзистора 5, примы какицая к истоку, образует МДП-струкгу ру или с более низким значением поро гового напряжения (включая изменение своего знака на противоположный), или с более высокой удельной емкостью, чем другая часть. Часть схемы, содержащая второй 4 н третий 5 транзисторы, при наличииf пнтаюших напряжений, приложенных к шич нам 7 н 6, обеспечивает устойчивое под. держание двух состояний потенциала затвора транзистора 4. Запись информации в ячейку (т. е. по-, тенциала ва затвор транзистора 4) осу- шествляется путем подачи сигналов н адресную шину тактового питания 6, отпиракмцих первый и второй транзисторы при заряженной или разряженной разрядной шине 3 в зависимости от того, записывается логическая единица или нуль. Считывание информйцик производится на разрядную шину 3 при подаче на адресную шину 2 напряжения, отпирающео первый транзистор 1. Цепь считывания содержит шину питания 6, второй 4 и первый 1 транзисторы. Если в ячейке записана логическая единица, т. е. потенциал, превышаюший пороговое иапряженив Второго транзистора 4, то он открыт и происходит заряд разрядной шины 3 по казанной цепи. В случае логического нуля цепь считывания разорвана и на ра рядной шине сохраняется нулевой потенциал. В силу того, что считывание производится не непосредственно с запоминающей емкости затвора второго транзистора 4 J записанная информация при этом не разрушается. Предлагаемая ячейка памяти является ячейкой квазистатического типа, обпаяачощей способностью устойчивого хранения двух состояний и позволякяцей оперативно перезаписывать и считывать информацию. Chaa позволяет производить регенерацию информации одновременно во всех ячейках матрицы и обеспечивает неразрушающее ее считывание. Благодаря возможности подачи сравнительно высоких напряжений на затвор тран зистора 1 при считывания предлагаемая ячейка обладает более высоким быстродействием. Кроме того, упрощается схема матрицы, выполненной на предлагаемых ячейках. Фор му ла изобретен и я Ячейка памяти, содержащая три МДГи транзистора, затвор и исток первого транзистора подключены соответственно к адресной и разрядной шинам, сток его соединен с истоком второго транзистора, затвор которого подключен к истоку третьего транзистора, и шины импульсов и питания, отличающаяся тем, что, с целью повьпиевия надежности и быстродействия ячейки, в ней сток Второго транзистора подключен к пгане питания, исток его соединен со стоком третьего транэшзтора, затвор которого подключен к шнве тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1.Зарубежная радиоэлектроника, 1975, № ii с. 77. 2.Патент США № 37О6О7Э, кл. 34О-1736, опубл. 12.12.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Квазистатическая ячейка памяти | 1976 |

|

SU631988A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

Авторы

Даты

1979-08-25—Публикация

1976-06-03—Подача