.jJOPO соединен с третьим информационным й-ходом записи начальных условий устрбйства, второя информационный вход результата которого соединен с SToptia разрядным выходом четвертого регистра, вход блока управления соедийен с входом запуска устройства.

( . .

5. Преобразователь по п,1, от л и ч а ю щ и и с я тем, что блок анализа содержит элемент сравнения, триггер, первый, второй, третий и четвертый элементы И, причем информационный вход элемента сравнения соединен с первым входом блока анализа, второй вход которого соединен с первыми информационными вхьдами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами триггера, прямой и инверсный выходы которого соединены с первыми информационными входами соответственно, третьего и четвертого элементов И, вторые информационные входы которых соединены с третьим входом блоха анализа, первый и второй выходы которого соединены с выходами соответственно третьего и четвертог зйементов И третий выход блока аналйэа соединен с прямым выходом триггера.

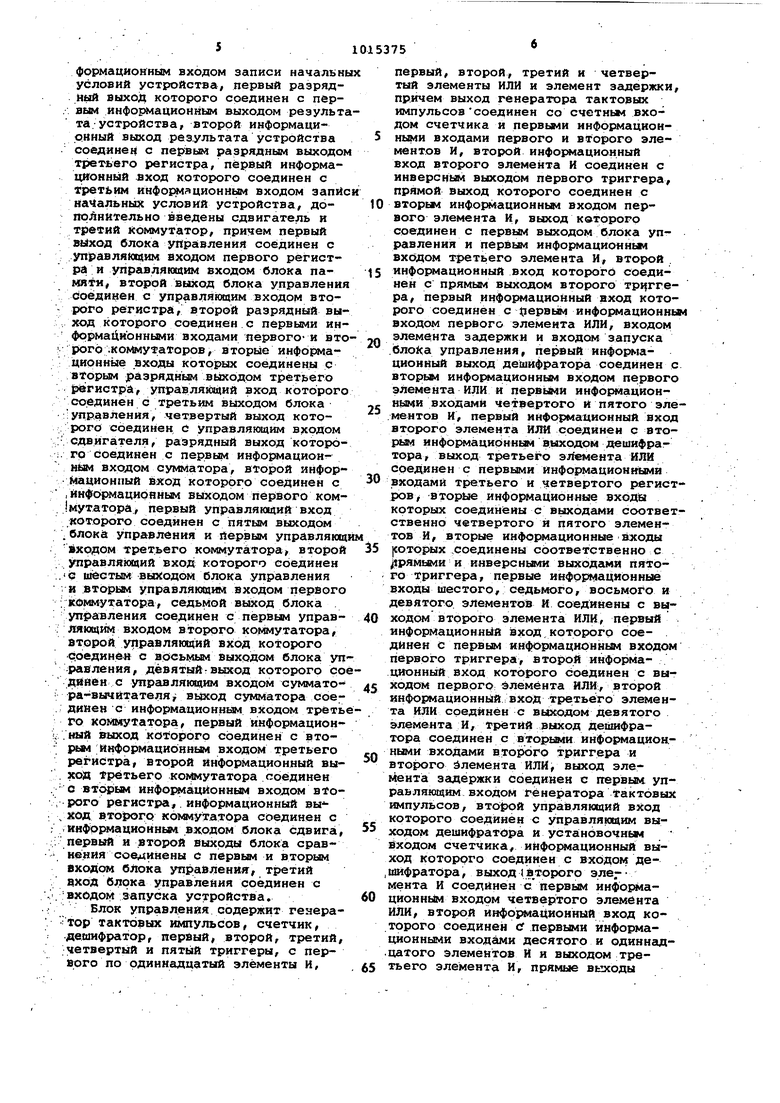

3. Преобразователь по п.1, о тл и ч а ю щи йен тем, что блок управле ния содержитгенератор тактовых импульсов, счетчик, дешифратор, первый и второй триггеры, первый, второй и третий элементы И, первый, втйрой и третий элементы ИЛИ и элемент задержки, причем выход генератора тактовых импульсов соединен со счетнвм входом счетчика и первьали информационными входами первого и второго элементов И, выход счетчика соединен с управляющим входом дешифратора, первый информационный эыход которого соединен с первым ияформационннм входом первого элемента ИЛИ, Выход которого соединен о первьм информационным входом ntepврго триггера, прямой и инверсный выходы которого соединены с вторыМи информационными.входами соответственно первого и второю элементов И, второй информационный-вход триггера соединен с вторым информационным выходом дешифратора и первым информационным входом второгю .элемеита ИЛИ, второй информационй)3й вхрд -которого соединен с третьим информационным выходом дешифратора, управляющий выход которого

.соединен с установочными входами счетчика и генератора тактовых Импульсов, вход запуска которого соединён с выходом элемента задержки,

вхрд которого соединен с входом

блока управления, втором информа {ионным входом первого элемента ИЛИ и первым информациониьм входом втброго триггера, второй информационный вход которого соединен с третьим выходом дешифратора, прямой выход второго триггера соединен с первьм информацис нным входом .третьего элеГ4ента И, выход которого соединен с nepBfcSM информационным входом третьего элемента ИЛИ, второй информационный вход которого соединен с выходом второго элемента И, выход второго элемента ИЛИ соединен с первым выходом блока управления, второй выход которого соединен с прямым выходом первого триггера, выход .первого элемента И соединен с вторым информационным входом третьего элемента И и третьим выходом блока управления, четвертый выход которого соединен с выходом третьего элемента ИЛИ, выход третьего элемента И соединен с пятым выходом блока управления, шестой выход которого соединен с выходом третьего элемента ИЛ

4. Цифровой функциональный преобразователь, содержащий сумматорвычитатель, сумматор, первый, второй и третий регистры, блок памяти, первый и второй коммутаторы, блок сраврения и блок управления, причем первый разрядный выход первого регистра соединен с первьвл информационным входом сумматора-вычитателя, выход которого соединен с первым информационаьм входом первого регистра/ йторой информационный вход которого соединен с первым информационным входом записи Начальных условий устройства, информационный выход блока памяти соединен с вторым информационным входом сумматора-вычитателя. Информационный вход блока сравнения соединен с втОрш разрядном выходом первого регистра, информационный вход второго регистра соединен с вторым информационным входом записи Начальных условий устрОйства первый разрядный выход которого соединен с первым информационным выходом результата устройства, второй информационный выход результата устройства соединен с первым разрядным выходом третьего регисра, первый информационный вход которого соединен с третьим информационным входом записи начальных условий устройства, отличающ И и с я тем, что, с целью расширения функциональных возможностей устройства путем увеличения количества одновременно вычисляеюлх функций, содержит сдвигатель и Tjjeтий коммутатор, причем первый выход блока управления соединен с управляющим входом первого регистра и управляквдим входом блока памяти, второй выход блока управления соединен с управляющим входом второго регистра второй разрядный которого соединен с первыми информационньзми входами первого и

второго коммутаторов, вторые информа.циЬнныз входы которых соединены с вторьм раэрядньву выходом третье-. го регистра, управля1Ш|ий вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с упрайляющим входом сдвигателя, разрядный, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с информационным выходом первого ком,мутатора п:ервый управляющий вход которого соединен с пятым выходом .блока управления и первым управля- i мщим входом третьего коммутатора, BTOpofI управляющий вход которого соединён -С шестым выхо:дом блока управления и в управ ляхядим входом первого коммутатора, седьмой выход блока управления средй«ен с первым

управлянадим входом второго коммутатора/ второй управляадий вход кот торого соединен с восьмым выходом

блока управления, девятый выход которого соединен с управляющим входом сумматора-вычитатеяя выход сумматора соединёй с информационным входом третьего; коквлутатора, первый Информационный вых:одкс торого .дивен с вторым информационным входс 4 третьего регистра, второй информ ционный выход третьего коммутатора соединен с вторым информационHbw входом Btoporo регистра, инфор-. мацлонный выход второго коммутатора соединен с информационным входом блокэ сдвига первый и второй выходц блока сравнения соединены с п ервым. и вторь входом блокауправления, третий iBxoa блока управления соединен с йходом запуска устройства.

5, ПрербразОвате ль по п« 4 о т л и 4 а ю щ и и с я тем, что блок , управления содержит генератор тактовых таотульсов, счетчик. Дешифратор, первый/ втойойу третий, четвертый и пятый триггеры, С первого по одинмаддатый элементы И, первый, второй, третий и четвертыйэлементы ИЛИ и элемент задержки, причем выход гейергн-рра тактовых импульсов соединен ео счетйыл входом счетчика и перв|фш информационными входами перврго и вторрго элеме«тов И, второй информациоиный вход второго э.лемента И соединен с Инверсным выходом первого триггера, прямой выход которого соединен с вторым информационным входом первого элемента И, вы ход которого соединен с первьм выходом блока управления и первым информационным входом третьего элемента И, второй -инфррмационный вход которого соединен с прямым выходом второго триггера, первый инфррмационный вход которого соединен с первым информационным входом перврго элемента ИЛИ, входом элемента задержки и вхрдрм запуска блока управ- ; ления, первый информационный выход дешифратора соединен с вторым информационным входом первого элемента ИЛИ и первыми информационными входами .четвертого и пятого элементов И, первый информационный вход второго элемента ИЛИ соединен с вторым информационным выходом дешифратора, .

выход третьего элемента ИЛИ соединен с первыми информационньми входами третьего и четвертого регистров, . вторые информационные входы которых соединены с выходами соответствен-, но четвертого и пятого элементов И, . вторые инфЪряиационные входы крТорых соединены соответственно с пря- : . мыми и инверсными выходами пятого триггера, первые.информацирнные входы шестого, седьмого, восьмого . и девятого элементов И соединены с выходом второго элемента ИЛИ, .пер вый информационный вход которого. : соединен с первым инфорМацйРнным входом первого триггера, второй ий-; формационный вход которого соединен с выходом первого элемента ИЛИ, второй информационный вход, третьего элемента ИЛИ соединен с выходрм девятого элемента И, третий выход дешифратора соединен с вторыми ин- формационньми входами второго триг- гера и второго элемента ИЛИ, выход . элемента задержки соединён с первым управляющим входом генератора тактовых импульсов, второй управляющий . вход которого соединен с управляйщим выходом дешифратора и установоч- : ньм входом счетчика, информационный выход которого соединен с входом . дешифратора, выход второго элемен- : та И Соединен с первьм информацион- ным входом четвертого элемента ИЛИ, второй информационный вход котор.рго соеДине{ с первьми информационньми входами десятого и одиннадцатрго элементов И и выходом третьего элемента И, прямые ВЫХ.ОДЫ третьего и четвёртого триггеровсоединены с вторыми информационными входами десятогр и одиннадцатого элементов И, выходы которых .соединены соответственно с вторым и третьим выходами блока управле.ния, четвертый выход которого соединен с выходом четвертого элемента ИЛИ, пятый и шесто.й выходы блока управления соединены с вторыми информационньми входами соответственно десятого и одиннадцатого элементов И, седьмой выход блока управления соединен с выходом шестого элемента И, второй информацйониый вход которого соединен с прямьм выходом пятого триггера, восьмой выход блока управления соединен с выходом седьмого элемента И, второй информадионный вход которого соединен с инверсным выходом пятого

триггера, прямой выход которого соединен с девятым выходом блока управления, вторые информационные входы восьмого и девятого элементов И соединены соответственно с первым и вторым входами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для преобразования координат вектора в трехмерном пространстве | 1986 |

|

SU1403062A1 |

: 1. -Цифровой функциональный пре. образователь, содержащий сумматорвьнитатель, первый сумматор,-первый, второй «третий регистры, первый и второй элементы И, блок памяти и блок управления, причем первый разрядный выход первого регистра соёдиме1 с первым информационным входсм сумматрра-вычитатёля, выход которого соединен с информационным входс м первого регистра, второй инфо 1ацирнный вход которого соединен -С первым информационным входом записи начальных условий устройства ,,информационный выход блока памяти соединен

1

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной реализации операции вычисления показательной функции в специализированных вычислительных устройствах.

Известно устройство для вычисления функции у

содержащее счетчик, счетчик-регистр, схемы запрета и схему сборки Cll

Недостатком этого устройства является то, что оно предназначено только для вычисления функции с положительным аргументом,

Известно устройство для вычисления экспоненциальной функции, содержащее сумматоры, регистры, блок памяти и блок управления 2,

Недостатком этого устройства является невозможность одновременно вычислять две функции (положительного и отрицательного аргумента) и необходимость повторять все итерации, что увеличивает в два раза время вычисления.

Наиболее близким по технической сущности и достигаемому результату предлагаемому является устройство для вычисления экспоненциальной фун ций, содержащее два одноразрядных сумматора-вычитателя, три регистра, блок односторонней памяти, два элемйнта И, блок определения знака и блок анализа сходимости (блок сравнения) , блок сброса, блок повторе-, ния итераций и блок управления С33«

Недостатком этого устройства является то, что оно предназначено только для вычисления экспоненциальной функции положительного аргумента, т,е, ограничено число вычисляемьи функций. Кроме того, это устройство для ряда значений аргументов не обладает высоким быстродействием, так как в нем необходимо повторять по два раза ите7 рации с номерами 3,5,7 и т,д,

.Цель изобретения - расширение функциональных возможностей устройства за счет увеличения количества одновременно вычисляемых функций путем одновременного вычисления показательной функции (например, экспнеиты) как положительного, так и отрицательного аргумента.

Поставленная цель достигается тем, что по первому варианту в устройство, содержащее сумматор-вычитатель, первый сутиматор, первый, второй и третий регистры, первый и второй элементы И, блок памяти и блок управления, причем первый разрядный выход первого регистра соединен с первым информационным входом сумматора-вычитателя, выход которого соединен с информационньни вхоДом первого регистра, второй информационный

вход которого соединен с первым ин-.

формациЬнньм входом записи начальных условий устройства, информационный выход блока памяти соединен с вторым информационным входом сумматора-вычитателя, первый разрядный выход второго регистра соединен с первым информационным входом сумматора, выход которого соединен с первьм информационным входом второго регистра, второй информационный вход которого соединен с вторым информационным входом записи начальных условий устройства, первый информационный выход результата которого соединен с вторым разрядным выходом второго регистра,.параллельный выход которого соединен с информационным входом третьего регистра, дополнительно введены второй сумматор, четвертый и пятый регистры и блок анализа, причем первый разрядный выход четвертого регистра соединен с первым информационным входом второго сумматора, выход которого соединен с первь1м информационным входом четвертого регистра, параллельный выход которого соединен с информационным входом пятого регистра, разрядный выход которого соединен с первым информациейным входом второго сумматора, разрядный выход третьего регистра соединён с первым информаци-

онным входом второго элемента И,

выход которого соединен с вторым информационным входом первого сумматора, второй информационный вход второго элемента И соединен с первым

выходом блока анализа, второй выход которого соединен с вторым информационным входом первого элемента И второй разрядный выход первого регистра соединен с первым входом блока анализа, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен с третьим входом блока анализа третий быход которого соединен с управлякздим входом сумматора-вычитателя, третий выход блока управления средииен с установочными входами блока памяти и первого регистра, четвертый выход блока управления соединен с установочным входом третьего регистра, пя.тыйвыход блока управления соединен с установочными входами второго и четвертого р гистров , шестой выход блока управле нйя.соединен с устандвочным входом iчетвёртого.регистра, второй инфор мационный вхрд которого соединен с третьим.информационным входом записи начальных условий устройства, второй информационный выход результата которого соединен с вторым раз рядным внкодом четвертого регистра, вход блока управления соединен с вх дом запуска устройства. Блок анализа содержит элемент сравнения, триггер, первый, второй третий и четвертый элементы И, причем информационный вход элемента ср нения соединен с первым входом блока анализа, второй вход которого соединен с первыми информационными 1зходами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами триггера прямой и инверсный вьКоды которого соединены с первыми информационными входами соответственно третьего и.четвертого эле-. . ментов И, вторые информационные входы которых соединены с третьим вхоДом блока анализа, первый и второй выходы которого соединены о выходами соответственно третьего и чётв.ертого элементов И, третий выход блока анализа соединен с пряMfcJM выходом триггера. Блок управления устройства содержит генератор тактовых импульсов счётчик, дешифратор, первый и второй триггеры, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ .и элемент задер ки, причем выход генератора тактовы импульсов соединен со счетным входом счетчика и первыми информацирнньвии вхрдами первого и второго элементов И, выход счетчика Соединен с упра1вляющим входом дешифратора, первый информационный выход которого соединен с первым информационньах входом первого элемента ИЛИ выход которого соединен с первым информационным входом первого триггера, прямой и инверсный выходы которого соединены с вторыми информационными входами соответственно первого и второго элементов И/ второй информационный вход триггера соединен с BTOpfcJM информационньм выходом дешифратора и первым информационным входом второго элемента ИЛИ, второй информационный вход которого . соединен с третьим информационным выходом дешифратора, управляющий выход которого соединен с установочными входами счетчика и генератора тактовых импульсов, вход запуска которого соединен с выходом элемента задержки, вход которого соединен с входом блока управления, вторым информационным входом первого элемента ИЛИ и перВЕэМ информационным входом второго триггера, в±ррой информационный вхрд которого соединен с третьим выходом дешифратора, прямой выход второго триггера соединен с первым информационным входом третьего элемента И, выход которого соединен с первым информационным входом третьего элемента ИЛИ, второй информационный вход котррого соединен е выходом второго элемента И, выход второго элемента ИЛИ соединен с первым выходом блока управления, второй вь1ход которого соединен с прямым выходом первого триггера/ выход первого элемента И соединен с вторым информационным входом третьего элемента И и третьим выходом блока управления, четвёртый выход которого соединен с выходом третьего элемента ИЛИ, выход -третьего элемента И соединен с пятым выходом блока управления, шестой выход которого соединен с выхоДом трег хьего элемента ИЛИ.. Поставленная цель достигается тем, что (по втРрому варианту) в устройство, содержащее сумматор- .вычитатель, сумматор, первый, рой и третий регистры, блок.памяти, первый и второй коммутаторы, блок сравнения и блок управления, причем первый разрядный выход первого регистра соединен с первым информационньм входом сумматора-вычитателя, выхрд которого соединен с первым информационным входом первого регистра, второй информационный вход которого соединен с первым информационным входом записи начальных условий устройства, информационный выход блока памяти соединен с . вторым Информационным входом сум- . матора-вычитателя, информационный вход блока сравнения соединён с вторым разрядным выходом первого регистра, информационный вход второго регистра соединен с вторым информациониым входом записи начальных условий устройства, первый разрядный выход которого соединен с пераым информационным выходом результата, устройства, второй информационный выход результата устройства 5 соединен с первым разрядным выходом третьего регистра, первый информационный вход которого соединен с третьим информ |ционным входом записи начальных условий устройства, до- 10 прЛнИ ельно введены сдвигатель и третий коммутатор, причем первый BbtxoA блока управления соединен с управляющим входом первого регистра и управляющим входом блока па- 15 мсяти, второй выход блока управления Соединен с управляющим входом второго регистра, второй разрядный выход которого соединен с первыми информайионными входами первого- и вто- ng рого .коммутаторов, вторые информационные входы которых соединены с вторым (эазрядным выходом третьего 1рв1гистра, управлягадий вход которого соединен с третьим вьлходом блока js управления, четвертый выход которого соединен с управляющим входом сдвигателя, разрядный выход которогр соединен с первьп информацион входом сумматора, второй инфор- мационпый вход которого соедннен с г /информационным выходом первого ком мутатора, первый управляющий вход которого соединен с пятым выходом блока управления и йервым управляющим одом третьего коммутатора, второй 35 управлякадий вход которого соединен С шестым выходом блока управления

и вторьвл управляющим входом первого kONQ yTaTopa, седьмой вьосод блока уп авления соединен с первым управ- 40 Яяющим входом второго коммутатора, второй управляющий вход которого соединён с восьмым выходом блока управ/юния, девятый-выход которого соединен с улргшляющим входом сумматора-вычйтатедя выход сумматора соединен с информационным входом третьего коммутатора, первый информацион.ный выход которого соединен с вторым информационным входом третьего ... регистра, второй информационный выхая третьего коммутатора соединен о вторым информационным входсм втoрого регистра, . информационный ВЫ ход BToiporo кo wyтaтopa соединен с .информационным входом блока сдвига, 55 первый и второй выходы блока сравнения соединены с первьм и вторым ахоДом блока управления, третий вход блока управления соединен с ВХОДОМ запуска устройства. 60

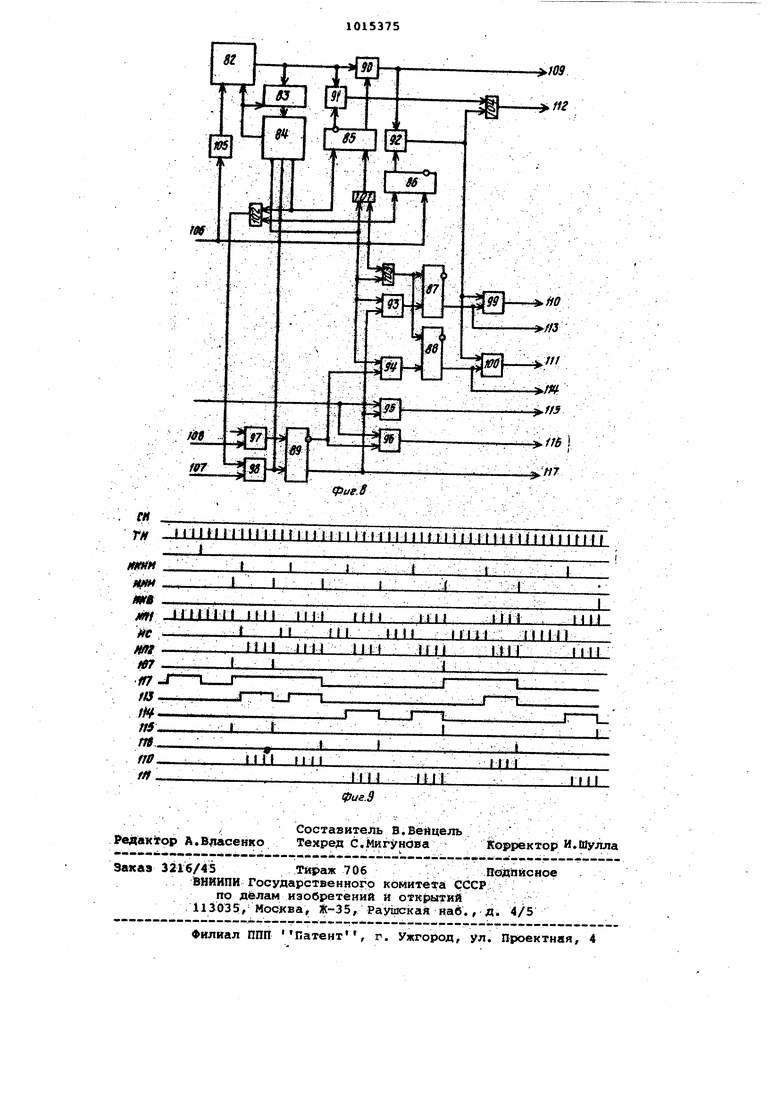

Блок управления содержит генера:тор тактовых импульсов, счетчик, дешифратор, первый, второй, третий, четвертый и пятый триггеры, с первого по одиннадцатый элементы И, . 5

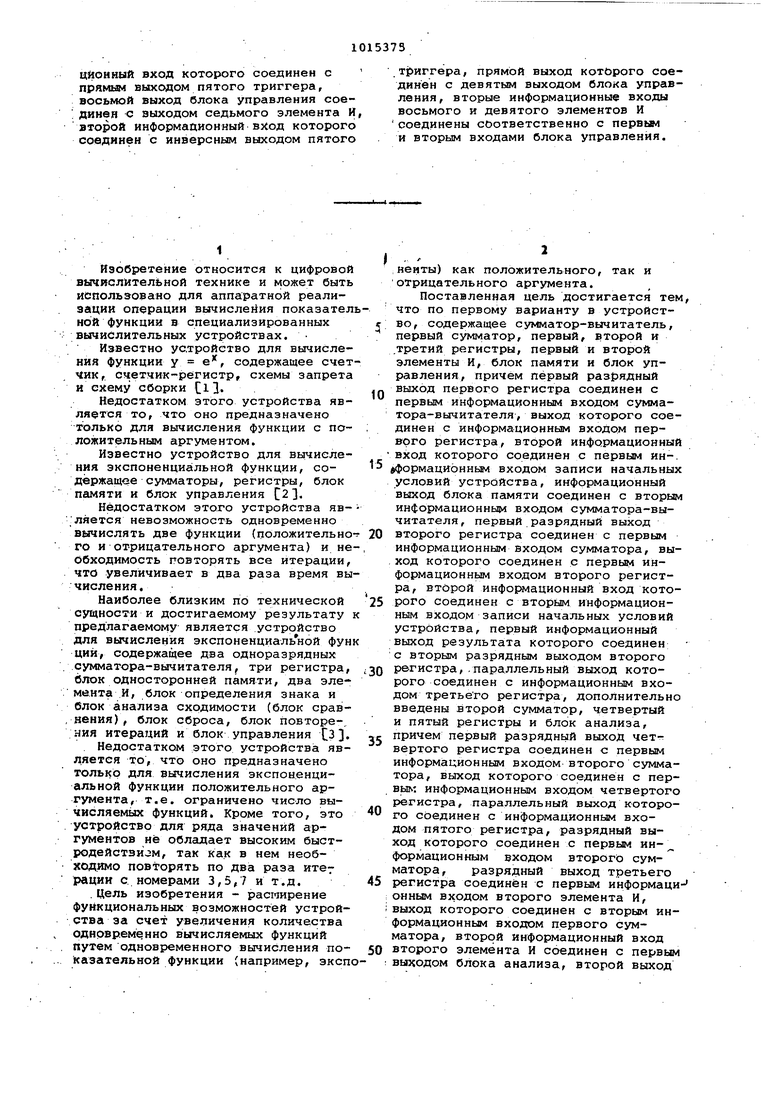

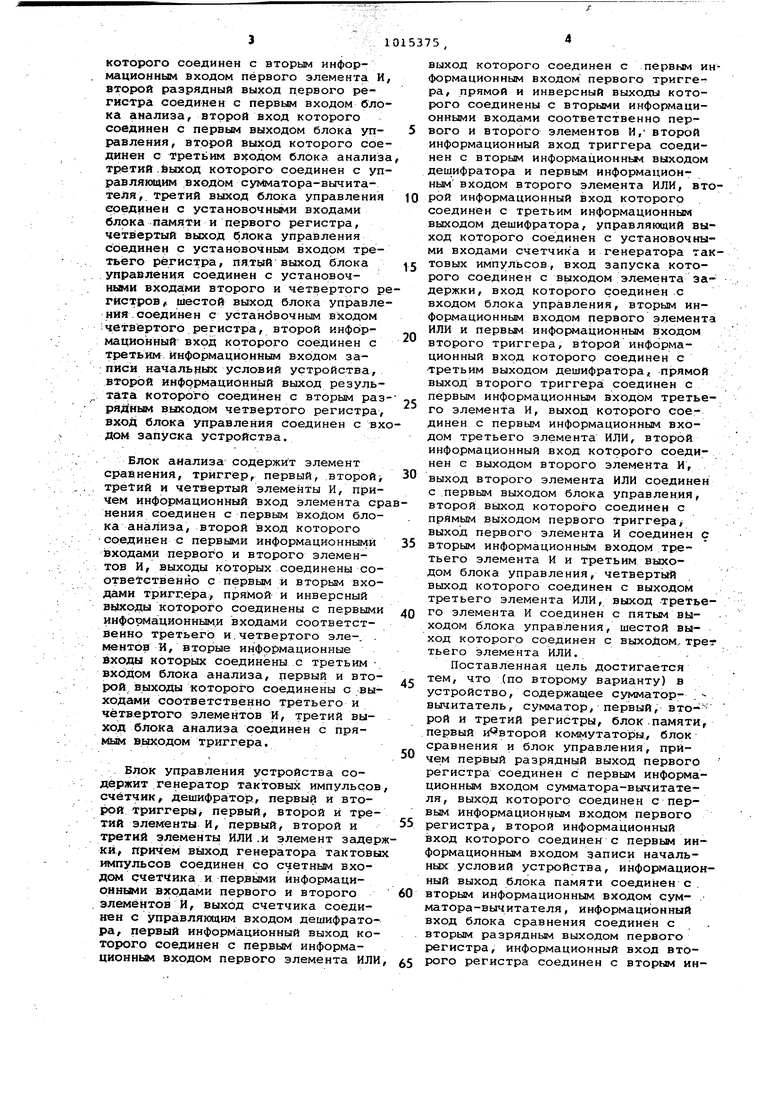

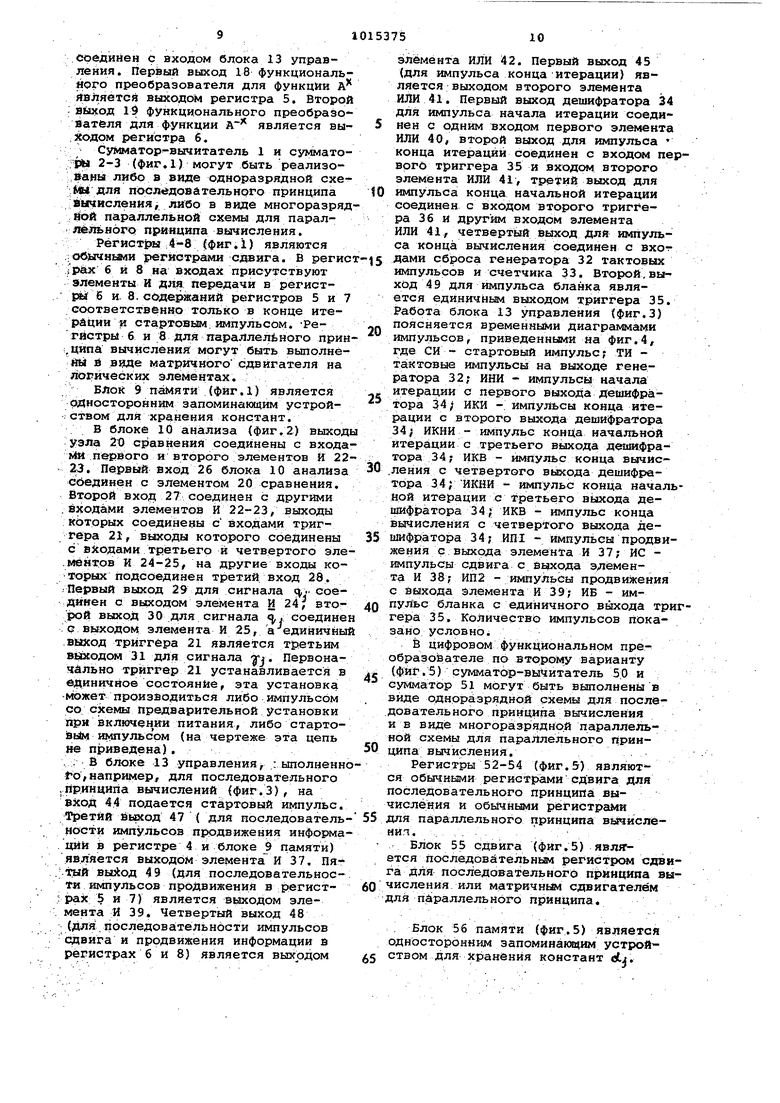

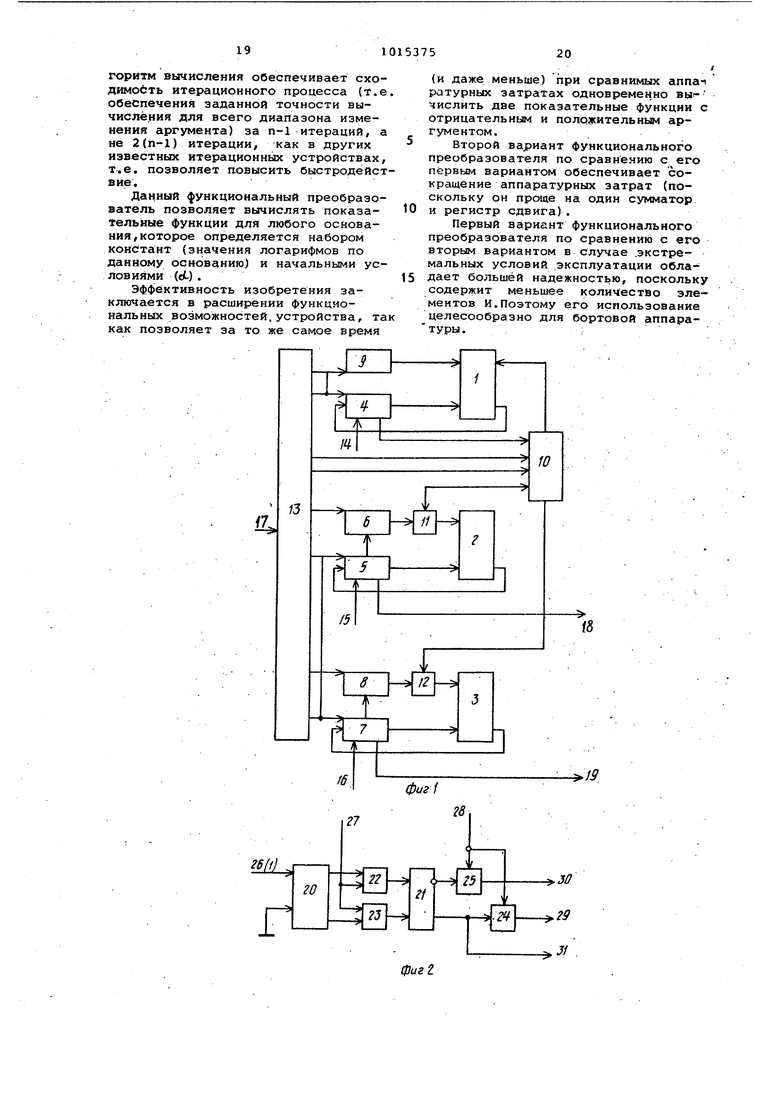

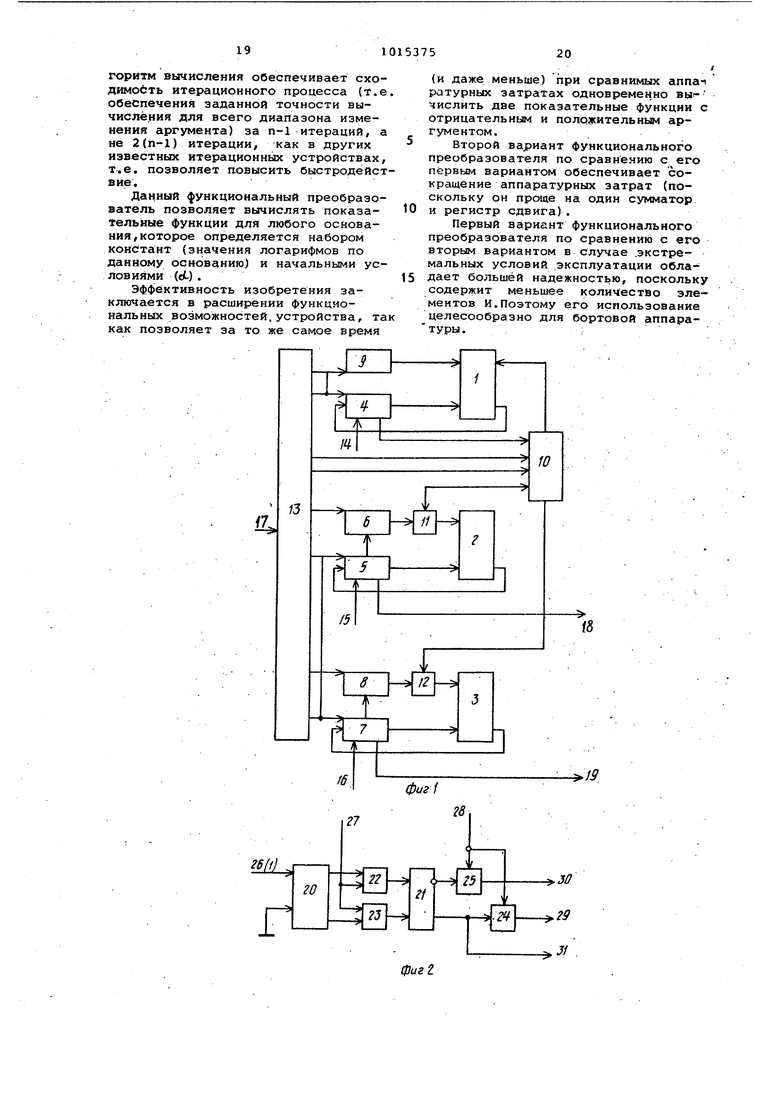

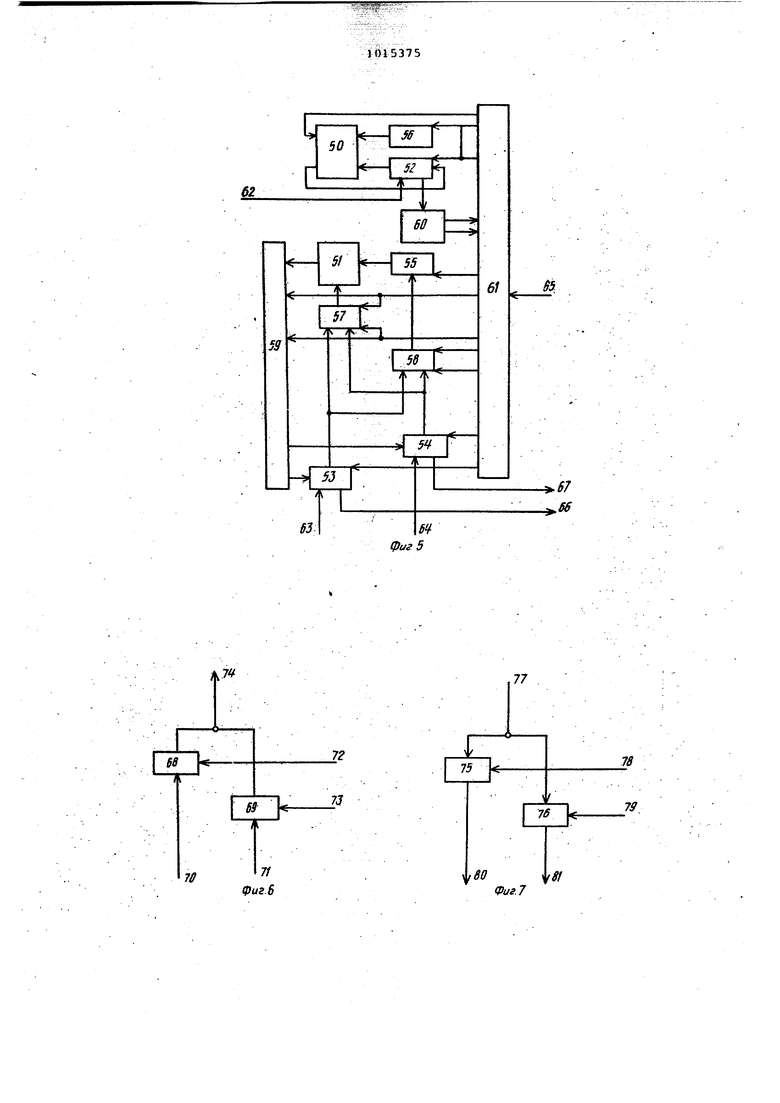

первый, второй, третнй и четвертый элементы ИЛИ и элемент задержки, причем выход генератора тактовых импульсовсоединен со счетньм входом счетчика и первьми информационньоли входами первого и второго элементов И, второй ннфО1Я4ационный вход второго элемента И соедннен с инверсным выходом первого триггера, прямой выход которого соедннен с вторым информационнь входом первого элемента И, выход которого соединен с первым выходом блока управления и первым информационные входом третьего элемента И, второй . информационный вход которого соединен с прямым выходом второго Tpifrreра, первый информационный вход которого соединён с первым информационнь входом первого элемента ИЛИ, входом элемента задержки н входом запуска . управления, первый информационный выход дешифратора соединен с вторьм инфо 4ационным входом первого элемента ИЛИ и первьй«4И информационными входами четвертого И пятого элементов И, первый информационный вход второго элемента ИДШ соединен с вторым информационньм выходом дешифратора, выход третьего эт емента ИЛИ соединен с первыми информационшями входами третьего и четвертого рёгистров BToptte информационные входа которых соединены с выходами соответственно четвертого и пятого элементов И, в торые информационные Входы соторых соединены соответственно с фямыми и инверс ньлуш в ыходами п ятого триггера, первые информационные входы шестого, седьмого, восьмого и девятого элементов И соединены с выходом второго элемента ИЛИ, первый информационнь й вход которого соединен с первым информационным входом первого триггера, второй информационный вход которого соединен с выходом первого элемента ИЛИ, второй информационней вход третьего элемента ИЛИ соед11нён с ВЫХОДОМ девятого элемента И, Третий выход дешифратора соединен с вторьми информационными входами второго триггера и второго Элемента ИЛИ, выход эле1 ента задержки Соединен с первьш управляющим входом генератора Тактовых импульсов, второй упр аВляющий вход которого соединен с управляющим выходом дешифратора и устанОвочньм Входом счетчика, информационный выход которого соединен с входом де,шифратора, выход )в торого эле-мента И соединен с первым информационным входрм четвертого элемента ИЛИ, второй информационный вход которого соединен С первыми информационными входами десятого и одиннад.цатого элементов И и выходом третьего элемента И, прямые выходы третьего и четвертого триггеров сое динены с вторыми информационными входами десятого и одиннадцатого элементов И, выходы которых соединены соответственно с вторым и третьим выходами блока управления, чет вертый выход которого соединен с вы ходом четвертого элемента ИЛИ, пяты и шестой выходы блока управления со динены с вторь1ми информационными входами .соответственно десятого и одиннадцатого элементов И, седьмой выход блока управления соединен с выходом шестого элементами, второй информационный вход которого соединён с прямым выходом пятого триггера, восьмой выход блока управления соединен с выходом седьмого элемента И, второй информационный вход которого соединён с инверсным выходом пятого триггера, прямой выход которого соединен с девятым выходом блока управления, вторые информационные входы восьмого и девятого элементов И соединены соответственн с первым и вторьм входами блока управления. ; Такое конструктивное решение (дв варианта) позволяет одновременно вы числять две показательные функции с положительным и отрицательным зна чением одного аргумента и повысить быстродействие за счет исключения повторения итераций. Сумматоры и сумматоры-вычиТатели блок анализа и блоки определения знака псевдочастного и анализа сходимости являются эквивалентны- мй в предлагаемом функциональном преобразователе и известном устройстве. Блок сброса прототипа введен ,в блок управления функционального преобразователя. На фиг.1 представлена структурна схема первого варианта преобразователя; на фиг.2 - структурная схема блока анализа; на фиг.З - структурная схема блока управления; на фиг временные диаграммы, иллк стрирующие работу блока управления. На фиг.5 приведена структурная схема второго варианта цифрового функционального преобразователя; на фиг.б - структурная схема первог или второго коммутаторов; на фиг.7 структурная схема третьего коммутатора; на фиг.8 - структурная схема блока управления; на фиг.9 временные диаграняны, иллюстрирующие работу блока управления. Цифровой функциональный преобразователь по первому варианту {фиг.1 содержит сумматор-вычитатель 1, первый и второй сумматоры 2 и 3, с первого по пятый регистры 4-8, блок памяти, блок 10 анализа, первый и второй элементы И 11 и 12 и блок 13 управления, первый, второй и третий входы устройства14-16, вход 17 запуска устройства, первый и второй . выходы 18 и 19 устройства.. Блок 10 анализа (фиг.2) содержит элемент 20 сравнения, двух кодов (код содержания регистра 4 и код нуля), триггер 21, с первого по четвертый элементы И , первый, второй и третий входы 26-128 блока, с первого по третий выходы 29-31 блока. Блок 13 управления для :последовательного принципа вычислений (фиг.З) содержит генератор 32 тактовых импульсов, счетчик 33, дешифратор 34, первый и второй триггеры 35 и 36, с первого по третий элементы И 37-39, с первого по третий элементы ИЛИ 40-42, элемент 43 задержки, вход 44 запуска блока с первого по пятый выходы 45-49 блока управления, шестой выход 49а блока управления. Цифровой функциональный преобразователь по второму варианту (фиг, 5) содержит сумматор-вычитатель 50, сумматор 51, с первого по третий, регистры 52-54, сдвигатель 55, блок 56 памяти, с первого пЪ третий коммутаторы 57-59, блок 60 сравнения, блок 61 управления, с первого по третий входы 62-64 устройства, вход запуска 65, первый и . второй информационные выходы 66 и В устройства. Коммутаторы 57 и 58 (фиг.б) содержат первый и второй элементы И 68 и 69, первый и второй информационные входы 70 и 71, первый и второй управляющие входы 72 и 73, Выход 74 коммутатора.. Коммутатор 59 (фиг.7) содержит , . первый и второй элементы И 75 и 76, информационный вход 77, первый и второй управляющие входы 78 и 79, первый и второй выходы 80 и 81 ком- мутатора. Блок 61 управления (фиг.8) для последовательного принципа вычисления содержит генератор 82 тактовых импульсов, счетчик 83, дешифратор 84, с первогв по пятый триггеры 85-89, с первого по одиннадцатый элементы И 90-100, с первого по четвертый элементы ИЛИ 101-104, элемент 105 задержки, вход 106 запуска блока, первый и второй входы 107 и 108 блока, первый-девятый выходы 109-117 блока. Первый вход 14 цифрового функционального преобразователя (фиг.1) для аргумента X соединен с входом регистра 4. Второй вход 15 для начальной установки единицы в регистр 5 соединен с входом последнего. Третий вход 16 для начальной установки коэффициента 1/К в регистр 7 соединен с его входом. Четвертый вход 17 для стартового импульса

средйнен с входом блока 13 управления. Первый выход 18 функциональяого преобразователя для функции А Аапяется выходом регистра 5, второй

вйход 19 функционального преобразователя для функции является вы,Ходом регистра 6.

Сумматор-вычитатель 1 и сумматоiasa 2-3 (фиг. 1) могут быть реализо аны либо в виде одноразрядной схеjilbl для последовательного принципа йымисленйя, либо в виде многоразряд ой параллельной схемы для параллельного принципа вычисления. Регистры ;4-8 (фиг.) являются

СХ ычнЕЛли регистрами сдвига. В регист

рйх б и 8 на входах присутствуют элементы И для йередачи в рёгистрвГ 6 и. 8. содержаний регистров 5 и 7 соответственно только в конце итерации и стартовым,импульсом. -Регистры б и 8 для параллельного принципа вычисления могут быть выполнёйы и ввде матричного сдвигателя на лорйческих элементах.

БЛОК 9 пау|яти{фиг. 1) является односторонним запоминакнцим устройством для хранения констант.

В блоке 10 анализа (фиг.2) вькоды узла 20 сравнения соединены с входак й первого и второго элементов И 2223. Первый вход 26 блока 10 анализа сбединен с элементом 20 сравнения. Второй вход 27 соединен с другшли входами элементов И 22-23, выходы которых соединены с входами триггера 21, вьисоды которого соединены с вводами третьего и четвертого элементов И 24-25, на другие входы которых подсоединен третий вход 28. Первый выход 29 для сигнала q,.. соединен с выходом элемента И 24, второй выход 30 для сигнала ,: соединен з выходом элемента И 25, а единичный вЕгход триггера 21 является третьим вьосодом 31 для сигнала г. Первоначйльно триггер 21 устанавливается в единичное состояние, эта установка

кюжет произйодиться либо импульсом Со схемы предварительной установки при вкЛючен ии питания, либо старто1ВЫм импульсом (на чертеже эта цепь не приведена).

. . И блоке 13 управления, гыполненно , например, для последовательного

Лриндипа вычислений (фиг.3), на

вход 44 подается ст 1ртовый импульс. Третий йыход 47 ( для последовательности импульсов продвижения информации в регистре 4 и блоке $ памяти) является выходом элемента И 37. Пя. тый вав4од 4 9 (для последов а те ль нос ти импульсов продвижения в регистpax 5 и 7) является выходом элемента И 39. Четвертый выход 48 (для.последовательнбсти импульсов сдвига и продвижения информации и регистрах б и 8) является выходом

элемента ИЛИ 42. Первый Выход 45 (для импульса конца итерации) является выходом второго элемента ИЛИ 41. Первый выход дешифратора 34 для импульса начала итерации соединей с одним входом первого элемента ИЛИ 40, второй выход для импульса конца итераций соединен с входс 4 первого триггера 35 и входсии второго элемента ИЛИ 41, третий выход для

импульса конца начальной итерации соединен с входом второго триггера 36 и другнм входом элемента ИЛИ 41, четвертый выход ДЛИ импульса конца вычисления соединен с вхот Яами сброса генератора 32 тактовых импульсов и счетчика 33. Второй.выход 49 для импульса бланка является единичным выходом триггера 35. Работа блока 13 управления (фиг.З) поясняется временнь 1И диаграммами

импульсов, приведенными на фиг.4, где СИ - стартовый импульс; ТИ тактовые импульсы на выходе генератора 32; ИНН - импульсы начала итерации с первого выхода дешнфратора 34; ИКИ - импульсы конца итерации с второго выхода дешифратора 34/ ИКНИ - импульс конца начальной Итерации с третьего выхода деашфратора 34; ИКВ - имйульс конца вычис.ления с четвертого выхода дешифратора 34; Й1ШИ - импульс конца начальной итерация с третьего выхода дешифратора 34; ИКВ - импульс конца вычисления с четвертого выхода дешифратора 34; ИП1 - импульсы продвижения с выхода элемента И 37; ИС импулзьсы сдвига, с вьиода з лёмента И 38; ИП2 - импульсы продвижения с выхода элемента И 39; ИБ - импульс бланка с единичного выхода триггера 35. Количество импульсов показано условно.

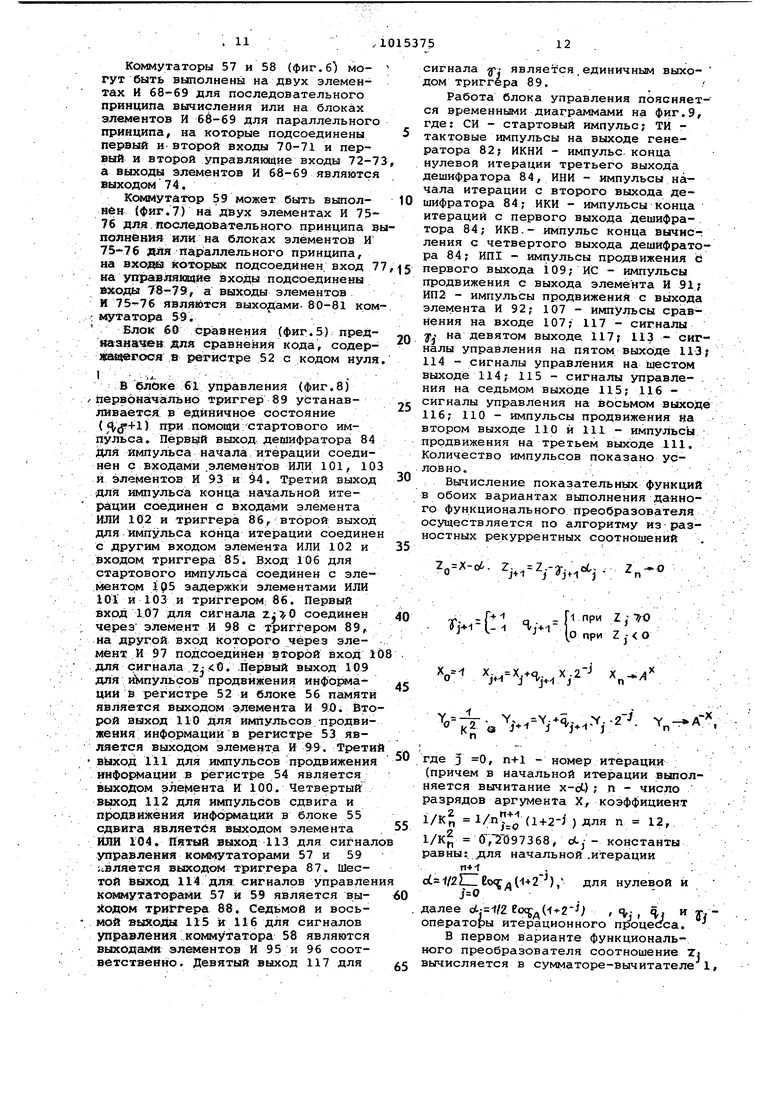

В цифровом функциональном преобразователе по второму варианту

(фиг.5) сумматор-вычитатель 5:0 и сумматор 51 могут быть выполнены в виде одноразрядной схемы для последовательного вычисления ив виде многоразрядной параллельной схемы для параллельного принципа вычисления.

Регистры 52-54 (фиг.5) являются обычными регистрамисдвига Для последовательного принципа вычисления и обычйьми регистрами

для параллельного принципа вьгаислеЙИЛ. ..,.,.. . .

Блок 55 сдвига (фиг.5) явл5Гется последовйтельным регистром сдвига для последовательногсэ принципа вычисления или матричньйл сдвигателём для параллельного принципа.

Блок 56 памяти (фиг.5) является односторонним запоминакяцим устройством для хранения констант «tj.

Коммутаторы 57 и 58 (фиг.б) могут быть выполнены на двух элементах И 68-69 для последовательного принципа вычисления или на блоках элементов И 68-69 для параллельного принципа, на которые подсоединены 5 первый и второй входы 70-71 и первый и второй управлянадие входы 72-73, а выходы элементов и 68-69 являются выходом 74.

Кс 4Мутйтор 59 может быть выпол- 10 вен (фиг.7) на двух элементах И 7576 дяя.последовательного принципа выпоянёвйя или на блоках элементов И 75-76 дйя Параллельного принципа/ на Bxoj которызс подсоединен вход 77,5 на управляющие входы подсоединены еходЫ 78-79, а выходы элементов И являютегя выходами- 80-81 коммутатора 59.

Блок 60 сравнения (фиг.5) пред- . наэна ев для сравнения кода, содер«ае ерооя 8 регистре 52 с кодом ауля.

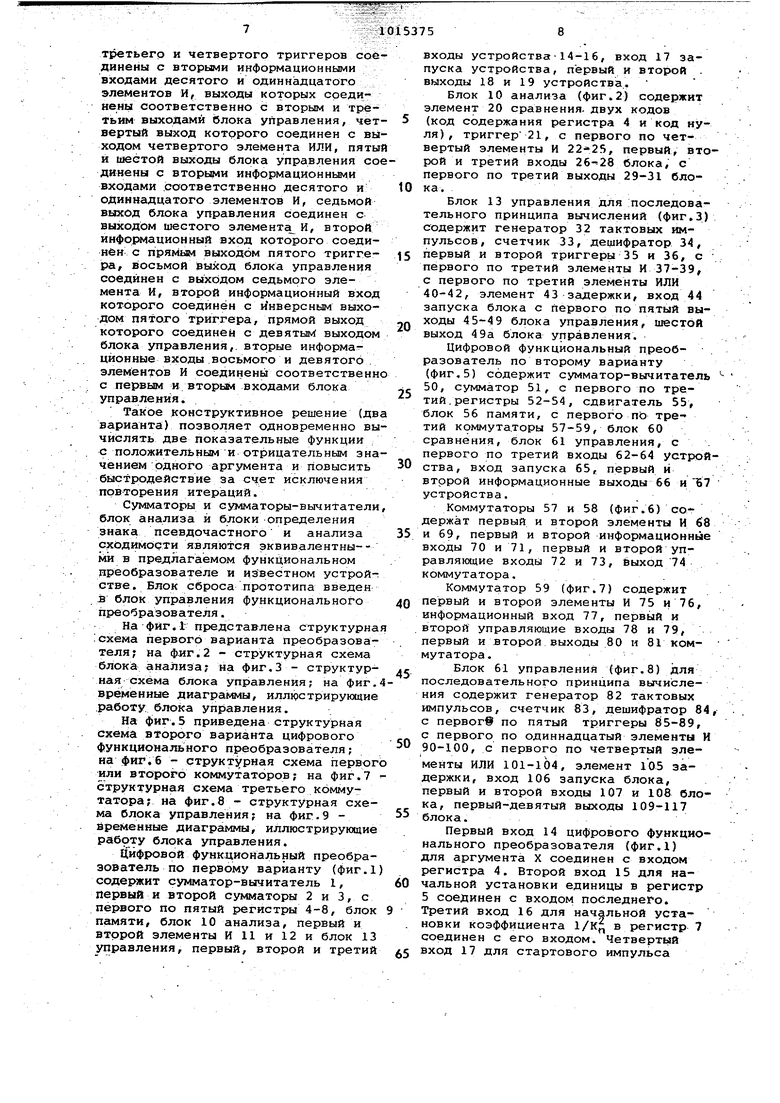

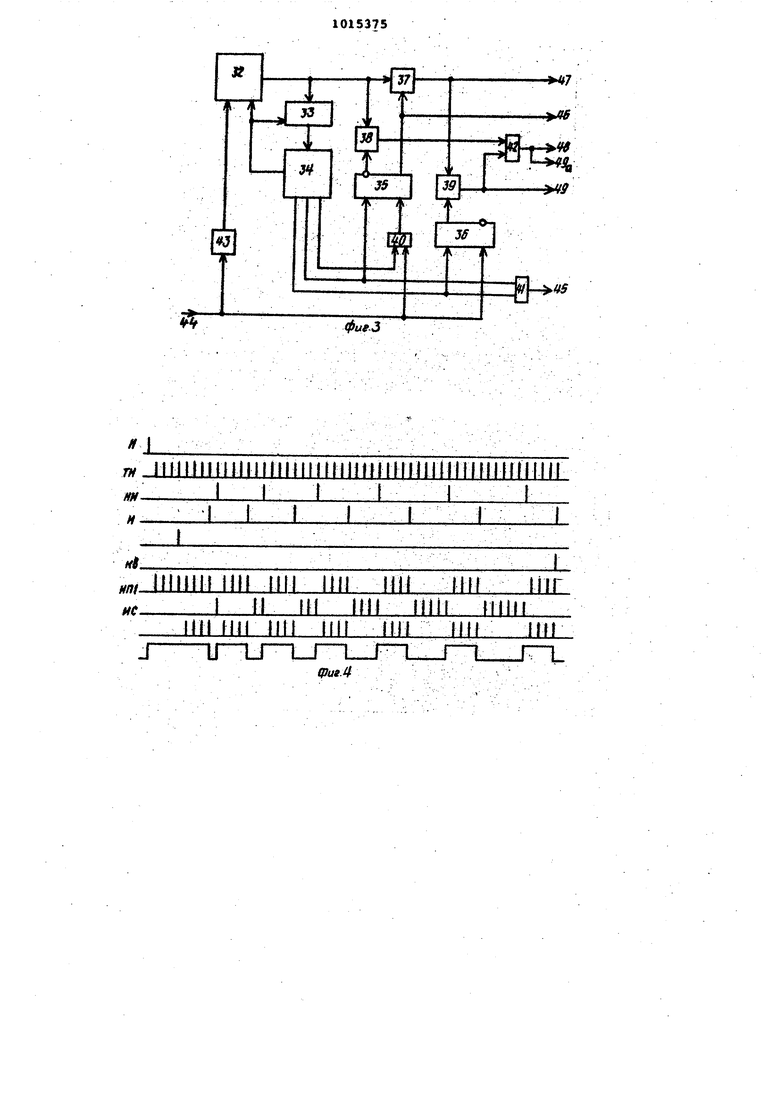

I - -. :, : ::. - . . в блоке 61 управления (фиг.8) первоначально Фриггер 89 устанав- ливается в единичное состояние { (+1) при .помощи:Стартового импулйса. Первый выход дешифратора 84 Для импульса начала,итераций соединен с входами .элемен-тов ИЛИ 101, 103 и элементов И 93 и 94. Третий выход 30 для шушульоа конца начальной итерации соединен с вхоДа ми элемента ИЛИ 102 и триггера 86, второй выход для импульса конца итераций соединен с другим входом элемента ИЛИ 102 и 35 входом триггера 85. Вход 106 для стартового импульса соединен с элементом 195 задержки элементами ИЛИ 101 и 103 и триггером, 86. Первый вход 107 для сигнала соединен 40 через; элемент И 98 с триггером 89, на ДРУГОЙ вход которого через элемент И 97 подсоединён второй вход 108 , для сигнала 2j t). Первый выход 109 для пульсов продвижения информа- АС ции в регистре 52 и блоке 56 памяти Является Выходом элемента И 90. Второй выход НО Для импульсов продвижения информации в регистре 53 является выходом элемента И . Третий

шхоа 111 для импульсов продвижения информации в регист эе 54 является выходом элемента И 100. Четвертый еыхрд 112 для импульсов сдвига и пцюдвижения информации в блоке 55 сдвига является выходом элемента 55 ИЛИ 104. Пятый выход 113 для сигналов управления ко 1утаторами 57 и 59 ;;вляется выходом триггера 87. Шестой выход 114 для сигналов управления коютутаторами 57 и 59 является вы- 60 Яодом триггера 88, Седьмой и восьмой выходы: 115 и 116 для сигналов управления коммутатора 58 являются выходами элементов и 95 и 96 соответственно- девятый выход 117 для 5

сигнала - является.единичным выходом триггера 89.

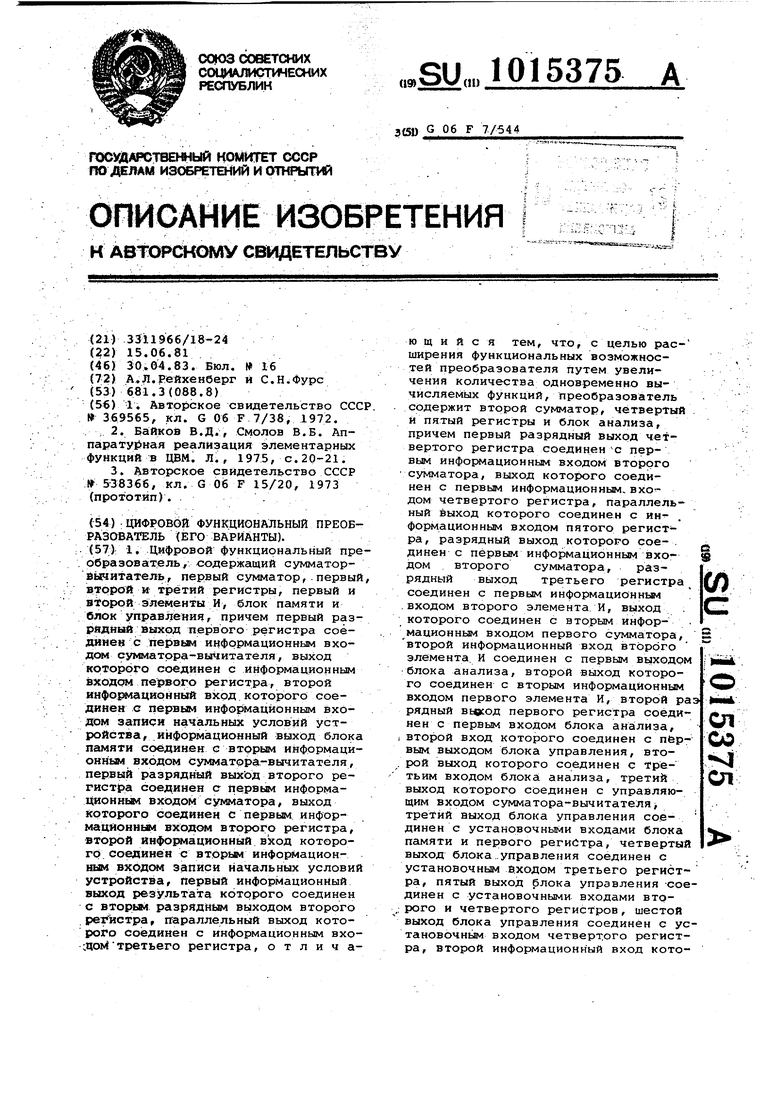

Работа блока управления поясняется временными диаграммами на фиг.9, где: СИ - стартовый импульс; ТИ тактовые импульсы на выходе генератора 82; ИКНИ - импульс конца нулевой итерации третьего выхода дешифратора 84, ИНИ - импульсы начала итерации с второго выхода дешифратора 84; ИКИ - импульсы конца итераций с первого выхода дешифра- . тора 84; ИКВ.- импульс конца вычисления с четвертого выхода дешифратора 84; ИП1 - импульсы продвижения С первого выхода i09; ИС - импульсы продвижения с выхода элемента И 91; ИП2 - импульсы продвижения с выхода элемента И 92; 107 - импульсы сравнения на входе 107; 117 - сигналы У на девятом выходе 117; 113 - сигналы управления на пятом выходе 11-3 114 - сигналы управления на шестом выходе 114; 115 - сигналы управле- . ния на седьмом выходе 5; 116 сигналы управления на восьмом выходе 116; НО - импульсы продвижения на втором выходе 110 и 111 - импульсы продвижения на третьем выходе 111. Количество импульсов показано условно.

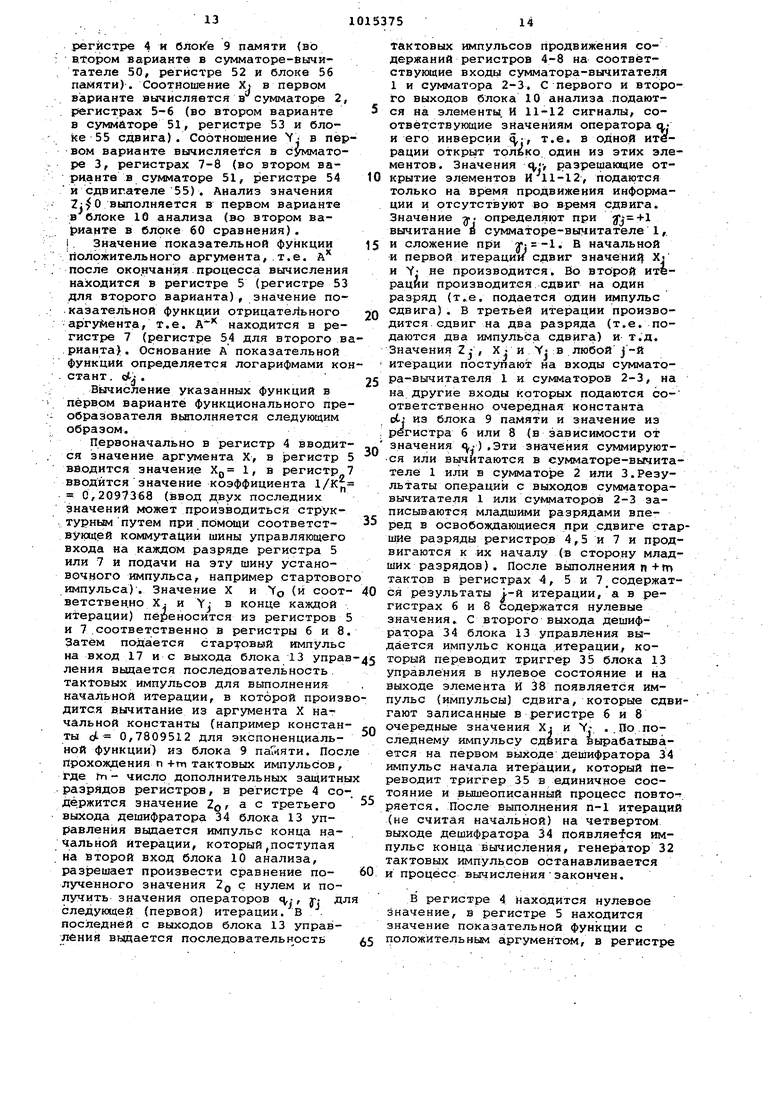

Вычисление показательных функций в обоих вариантах выполнения данного функционального преобразователя осуществляется по алгоритму из разностных рекуррентных соотношений

..

IjTrO

/ /+1|о

при о при Z

0

X..,, X,+q.. .Х-2 X. Л.+а. Х-:

JH j j+ у

V-T V V -2-- .

где 3 0, n+1 - номер итерации (причем в начальной итерации выполняется вычитание x-oL) ; п - число разрядов аргумента X, коэффициент

1/К (l+2-J ) для п 12,

1/К б ,Т097368, oi-j - константы равны: для начальной .итерации

п41,.:

ct 1/2EZEtxf «1-1+2)/ для нулевой и

далее ( / Srj , Hj Ji

операторы итерационного процесса. В первом варианте функционального преобразователя соотношение 7 вычисляется в сумматоре-вычитателе 1 регистре 4 и 9 памяти {во втором варианте в сумматоре-вычитателе 50, регистре 52 и блоке 56 памяти). Соотношение Xi в первом варианте вычисляется в сумматоре 2, регистрах 5-6 (во втором варианте в сумматоре 51, регистре 53 и блоке 55 сдвига). Соотношение V- в пер вом варианте вьлчисляется в сумматоре 3, регистрах 7-8 (во втором варианте в сумматоре 51, регистре 54 и сдвигателе 55). Анализ значения выполняется в первом варианте в блоке 10 анализа (во втором варианте в блоке 60 сравнения). Значение показательной функции положительного аргумента,,т.е. А после окончания процесса вычисления находится в регистре 5 (регистре 53 для второго варианта) , значение покаэательной функции отрицате/1ьного аргумента, т.е. А находится в регистре 7 (регистре 54 для второго в рианта). Основание А показательной функции определяется логарифмами ко стант, otj . Вычисление указанных функций в первом варианте функционального пре образователя вшюлняется следующим образом. Первоначально в регистр 4 вводит ся значение аргумента Х в регистр вводится значение Хд 1, в регистр вводится значение коэффициента 1/К 0,2097368 (ввод двух последних значений может производиться струк, турным путем при помсяци соответствующей коммутации шины управляющего входа на каждом разряде регистра 5 или 7 и подачи на эту шину установочного импульса, например стартово импульса). Значение X и YO (и соот ветствен.но X. и YJ в конце каждой итерации) переносится из регистров и 7 .соответственно в регистры б и 8 Затем подается стартовый импульс на вход 17 и с выхода блока 13 упра ления выдается последовательность, тактовых импульсов для выполнения начальной итерации, в которой произ дится вычитание из аргумента X начальной константы (например констан ты d 0,7809512 для экспоненциальной функции) из блока 9 паГкяти. Пос прохождения п +т тактовых импульсов, где т- число дополнительных защитн разрядов регистров, в регистре 4 со держится значение 2, а с третьего выхода дешифратора 34 блока 13 управления выдается импульс конца начальной итерации, который,поступая на второй вход блока 10 анализа, разрешает произвести сравнение полученного значения 2д с нулем и получить значения операторов t,:, jp. д следующей (первой) итерации. В . последней с выходов блока 13 управ;ления выдается последовательность тактовых импульсов продвижения содержаний регистров 4-8 на соотвётствукндие входы сумматора-вычитателя 1 и сумматора 2-3. С первого и второго выходов блока 10 анализа подаются на элементы. И 11-12 сигналы, соответствующие значениям оператора q,; и его инверсии , т.е. в одной итерации открыт только один из этих элементов. Значения «, разрешающие открытие элементов И 11-12, подаются только на время продвижения информации и отсутст вуют во время сдвига. Значение . определяют при вычитание в сумматоре-вычитателе 1, и сложение при у. -1. В начальной и первой итерации сдвиг значени ХГ и YJ не производится. Во второй итерации производится сдвиг на один разряд (т.е. подается один импульс сдвига). В третьей итерации производится, сдвиг на два разряда (т.е. подаются два импульса сдвига) и т.д. Значения Z . , X и YJ :В . любой j-й итерации поступают На входы сумматора-вычитателя 1 и сумматоров 2-3, на на другие входы которых подаются соответственно очередная константа ot; из блока 9 памяти и значение из регистра 6 или 8 в зависимости от значения .-) .Эти значения суммируются или вычитаются в еумматоре-вычитателе 1 или в сумматоре 2 или 3.Результаты операций с выходов сумматоравычитателя 1 или сумматоров 2-3 записываются младшими разрядами вперед в освобождающиеся при сдвиге старшие разряды регистров 4,5 и 7 и продвигаются к их началу (в сторону младших разрядов). После выполнения п +fn тактов в регистрах 4, 5 и 7 содержатся результаты 1.-Й итерации,а в регистрах 6 и 8 содержатся нулевые значения. С второго выхода дешифратора 34 блока 13 управления выдается импульс конца .итерации, который переводит ipurrefp 35 блока 13 управления в нулевое состояние и на выходе элемента И 36 появляется импульс (импульсы) сдвига, которые сдвигают записанные в регистре б и 8 очередные значения Xi и - ..До.последнему импульсу сдвига вырабатывается на первом выходе дешифратора 34 импульс начала итерации, который переводит триггер 35 в единичное состояние и внвиеописанный процесс повтор ряется. После выполнения п-1 итераций (не считая начальной) на четвертом выходе дешифратора 34 появляе ся импульс конца ВЕлчисления, генератор 32 тактовых импульсов Останавливается и процесс вычисления-закончен. В регистре 4 находится нулевое значение, в регистре 5 находится значение показательной функции с положительном аргументом, в регистре

15 7 находится значение показательной функции с отрицательным аргументом. Вычисление указанных функций во втором функционального преобразователя осуществляется следующим образом. Первоначально в, регистр 52 заносится значение аргумента X, в регистр 53 - значение единицы, а в регистр 54,- значение 1/К, подаетс стартовый импульс и с выхода блока управления выдается последовательность тактовых импульсов для выполн ния начальной итерации, в которой производится вычитание начальной константа ,7809512 из аргумента После выполнения тактов в регистре записано значение ZQ, по которому в блоке 61 управления определяются операторы С}, и у. для следующей |ры С}, и у. для следующей t) итераций. При , (первой)- Xj с выхода регистра 53 и значение через коммутаторы 57-58 (нд которые подаются сигналы разрешения с выходоэ бглока 61 управления) записы., ваются в сумматор 51 и блок 55 сдв га. . -. . -. - ,С выходов блока 61 управле-ния выдается последовательность тактовых импульсов, в сумматоре вычитателе 50 производится вычитание, очередной константы ctj . из блока 56 памяти из предыдущего значения сЬдержания .регистра 52 . а в сукилатбре 51 производится сложение содержания Xj из регистра 53 и содержания из блока 55 сдвига (в первойИтерации сдвиг не производится, т.е. Xfl-2°). Результ ты операции с выхода сумматора-вычи ателя 50 записываютс младшими р з| явами вперед в освобождающиеся при сдвиге старшие, разряды регистр 52 и продвигаются к его началу (в сторсшу младших разрядов). Результ ты операции с выхода сумматора 51 через коммутатор 59 (tfa который по дается .разрешающий сигнал с выхода блока 61 управления) записываются младшими разрядами вперед в осводозедавдиеся при сдвиге старшие раз ряды регистра 53 и продвигаются к его началу (в сторону младших разрядов) . В конце итера.ции в регистре 52 находится новое значение Zj,, в регистре 53 - новое значение Xu-j , в регистре 54 - старое

16

1015375 значение .-ц.- , .а в блоке 55 сдвига находится нулевое значение. Затем по импульсу конца итерации определ.яются новые значения операторов q,.; и /j-f-t- Например, при Tj+1 Vjt- О Р этом содержание V- регистра 54 через ком-мутаторы .57-58 (на которые подаются сигналы разрешения с выходов блока 61 управления записываются в сумматор 51 и блок 55 сдвига. С выхо да блока 61 управления на управляющий вход блока 55 сдвига выдается последовательность тактовых иипуль-. сов сдвига (в начальной и первой итерациях импульсы сдвига не выдаются, во второй итерации выдается один импульс сдвига, в третьей итерации выдается два. импульса сдвига и т.д.). Вьоиеописанный процесс повторяется, за исключением когда результаты операции с .выхода сумматора 51 записываются младшими разрядами вперед через коммутатор 59 (на который подается Сигнал ра13решения с выхода блока 61 управления) в освобождающиеся при сдвиге старшие разряды регистра 54 и продвигаются к его началу. В этом случае значение в -регистре 53 остается без изменения., а в .регистрах 52 и 54 содержатся новые значения i + t соответственно. После выполнения (n+l) итераций (не считая начальной) в регистре 52 находится нулевое значение, в ре- : .. гистре 53 находится значение показательной функции положительного. .; аргумента, а в регистре 54 находится значение показательной функции отрицательного аргумента. Процесс вычисления закончен и блок 61 управления прекргидает выдачу тактовых импульсов. Работа двух вариантов данного функционального преобразователя проверена путем моделирования на ЦВМ общего назначения. Аргумент X изменяется на одну единицу младшего двенадцатого двоичного разряда в пределах ,6. В таблице приведен один из при- . меров вычисления показательн.ых. функций прн основании е (т.е. экспоненциальных функций) для значения. аргумента X 0,86.

Моделирование подтвердило рабо 45 тоспособность, высокое быстродейст: вне с э.аданиой точностью вычисления двух функций. Иэ приведенного в таблице примера видно,, что погреишость вычисления значительно меньше единишь,,. двенадца рго младшего двоичного разряда..

; Погрешность вычЕис Ленин показ ате ль ных функций (например е и е-) в Данном, функциональном преобразователе определяется длиной разрядной сетки лргумвяул и прн выполнении п-Ы итераций и при испольэованиигаеЗ€ м{ Г дополнительных защитных разрядов АЛЯ кокшенсации погрешности усечения чисел при юс сдвиге, всегда -60 меньше ёциницы последнего млгшшего разряда п, что подтверждается результатами моделирования.

Максимальное вр1емя вычисления одновременно двух указанных функций в 5

Продолжение таблицы

обоих Вариантах данного функционального преобразователя для параллель ного принципа работы (при применении параллепьнш: cyi«iMaTopoB и матричных сдвигателей) равно в двоичных тактах

Т « 2(и+1),

а Для последовател1 ного принципа работы (при применения одноразрядных сумматоров и регистров сдвига) радно в Д1войчных тактах

(,

По быстродействию оба вариёГнта функционального преобразователя рдинакоды/ Tiik как благодаря особенности йредложёйнбго алгоритма вычисления в каждой итерации для Xj и Y/ Вьтолняется только одинсдвиг и одно сложение, а для другого операнда пропускаются. Реализованный в данном | ункциональном преобразователе алгоритм вычисления обеспечивает сходимобть итерационного процесса (т.е обеспечения заданной точности вычисления для всего диапазона изменения аргумента) за п-1 итераций, а не 2 {п-1) итерации, как в других известных итерационных устройствах, т.е. позволяет повысить быстродейстВИ(Э.

Данный (функциональный преобразователь позволяет вычислять показательные функции для любого основания, которое определяется набором констант (значения логарифмов по данному основанию) и начальными условиями (rf-) .

Эффективность изобретения заключается в расширении функциональных возможностей,устройства, та как позволяет за то же самое время

(и даже меньше) при сравнимых anna-i ратурных затратах одновременно вычислить две показательные функции с отрицательным и положительным аргументом.

Второй вариант функционального преобразователя по сравнению с его первым вариантом обеспечивает сокращение аппаратурных затрат (поскольку он проще на один сумматор

0 и регистр сдвига).

Первый вариант функционального преобразователя по сравнению с его вторым вариантом в случае .экстремальных условий эксплуатации обладает большей надежностью, поскольку содержит меньшее количество элементов И.Поэтому его использование целесообразно для бортовой аппаратуры.:

itinnHtiiiiMMiirriiiHiitiHiHiiiiifHiirrr 1 I I 11 1

I I I

IIIIHIf till 1111 111 1Ш liir

1 II 11 nil liiii mm

ни ни IIH HI iUi

45

фи9-3

i

1

(Ml

1ГН

.

Ж7

72

73

11

70 фиг. 6

77

78

75 k

73

Фиг. 7

(fitff.S fit - тм Hf1111ни 111и 1 11 ifum : ;. i . -. i iMiUM Jtll im fJiJ ini t It f I i ни ttn l JMJ t J иiitt

}09

т

т - . 11111 in гшtUrt11 гм t - -/ . :ч.- .- ; itii ни i ; ft mi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , 2 | |||

| Байков В.Д., Смолов В.Б | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Л;, 1975, с.20-21 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРОПАШНИК С УПРАВЛЯЕМЫМ ДЫШЛОМ | 1933 |

|

SU38366A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1983-04-30—Публикация

1981-06-15—Подача