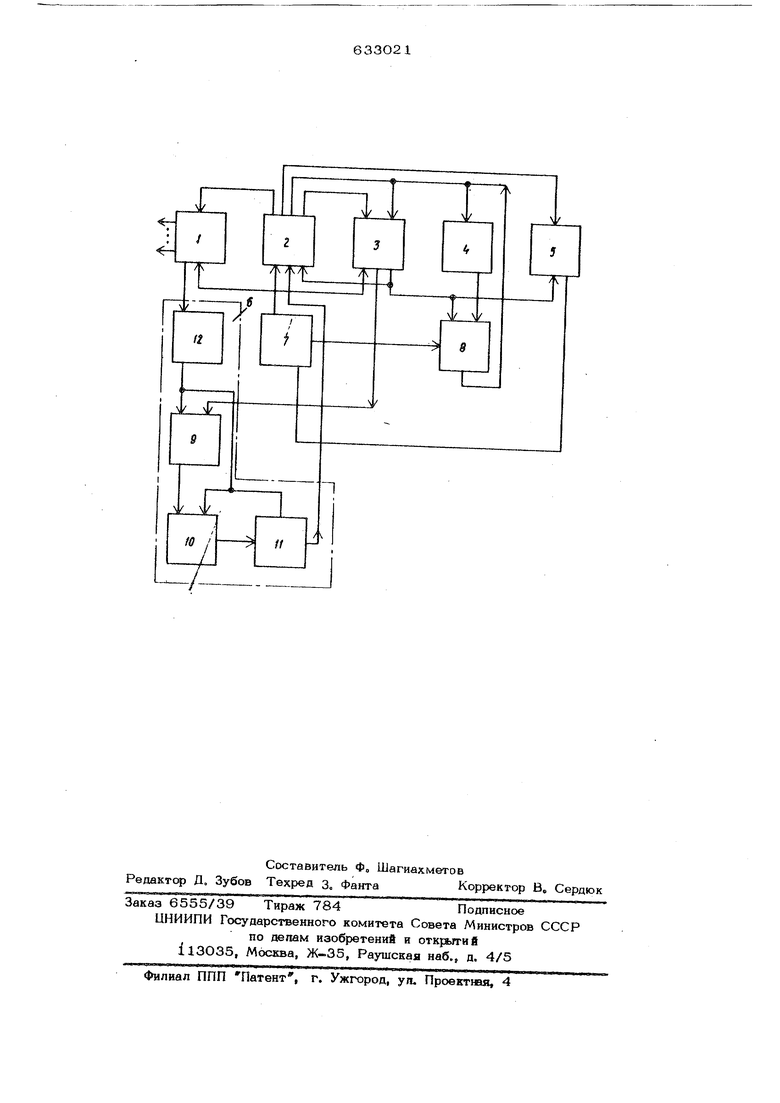

Изобретение относится к области вы- чиспитепьной техники, в частности, к про цессорам цифровых вычислитепьных машин и может быть использовано для ускорения вычислительного -процесса при решении задач требующих анапиза и подсчета идеитичных символов. Известен микропрограммный процессор содержащий арифметико-логический блок5 запоминающий блок, блок контроля, блок синхронизации, блок дешифрации микрокоманд, блок управления диагностикой, узел контроля четкости, блок запоминания микрокоманд, регистр микрокоманд, дешифраторы горизонтальных и вертикальных шин, переключатель режимов, горизонтальные и вертикальные вентили блокировки, блок изменения длительности импульсов, триггеры переключения выборки, инверсии контроля и инверсии выборки ij. Недостатком известного процессора закшочается в сложности его построения и в необходимости значительных затрат оборудования. Наиболее близким к изобретению по технической сущности и достигаемому результату является микропрограммный процессор Г2, содержащий арифметико-логический блок, первый выход к угорого соединен с первыми входами блока защиты памяти, блока хранения служебной информации и блока управления памятью, блок синхронизации, блок микропрограммного управления, первый вход которого соединен с первым выходом блока управления служебной информации, блок памяти, выход которого соединен со вторым входом блока управления памятью, причем первый вход арифметико-логического блока и вход блока памяти соединены с выходами блока управления памятью, блока защиты памяти я со аторым выходом блока хранения служебной информации, третий и четвертый ш 1ходы которого соединены со вторыми входами соответственно арифметико-логического блока и блока зашиты памяти, вторые входы блока микропрограммного управления и блока фанения служебной информации, третий вход J63 арифметико-логического блока соединены с первым выходом блока синхронизации, второй и третий выходы которого соединены с третьими входами соответственно блока управпения памятью и блока защиты памяти, а группа выходов блока микропрограммного управления является группой выходов процессора, В известном процессоре анализ и подсчет требуемых символов осуществляется с помощью последовательности операций, включающих операцию выделения текущего символа, анализа выделенного символа, занесения единицы в счетчик символов при условии, что текущий символ оказалн ся искомым, /операции сдвига последовательности мащинных слов с целью анализа очередного символа и проверку на окончание цикла анализа и подсчета символов. Осуществление указанной последовател ности операций усложняет программирова ние и увеличивает время вычислений ввиду, циклического повторения ряда одно типных операций, что приводит к снижению быстрюдействия процессора. Цель изобретения - повышение быст эо действия. Поставленная цель достигается тем, что прсщессор содержит блок анализа и подсчета символов данных, выполненный в виде узла формирования управляющих сигналов, схемы сравнения, элемента И и счетчика, причем выход узла формировани управляющих сигналов соединен с первыми входами схемы сравнения, элемента И и счетчика, выход схемы сравнения со динен со Вторым входом элемента И, выход которого соединен со вторым вхо дом счетчика, а вход узла формирования управлякнцих сигналов, второй вход схемы сравнения и выход счетчика соединены соответственно с выходом блока микропрограммного управления, со вторым выхсн дом арифметико-логического блока и с третьим входом блока кранения спужебной информации. Структурная схема npraieccopa приведена на чертеже. Проиесрор содержит блок микропрограм мнсяро управления 1, блсж хранения служебной иыформадии 2, арифметико-логичес кий блок 3, блок 4 памяти, блок защиты памяти 5, блок 6 анализа и подсчета сил волов данных, блок синхронизации 7, блок 8 управления памятью, а блок анализа и подсчета символов содержит схем сравнения 9, элемент И 1О, счвтчик 11 4 зел формирования управляющих сигналов 12. Работает процессор следукяцим образом. Связанный с блоком микропрограммного управления 1 узел 12 формирует все сигналы, необходимые для выполнения операции анализа и подсчета символов. Команда подсчета символов выполнена на базе команды сдвига и при выполнении использует все управляющие сигналы, вырабатываемые командой сдвига. При выполнении команды подсчета символов, анализируемая информация находится в арифметикологическом блоке 3, а код искомого символа засылается в схему сравнения 9, Анализ символа осуществляется путем сравнения кода анализируемого символа с кодом искомого символа (эталона). В случае совпадения кодов символов через эпемент И 10 в счетчик 11 заносится единица. Затем в арифметико-логическом блоке 3 вьшолняется операция сдвига последова тельности мащинных слов на количество разрядов, определяемое принятым методом кодирования символа (для двоичного кода на 1 разряд, для восьмиричногона 3 разряда и т.п.), вновь производится сравнение кодов, занесения в случае равенства кодов единицы в счетчик 11 и т.д. Этот процесс продолжается до тех пор, пока не будут проверены все симво лы, что задается информацией в команде подсчета символов. В результате в счетчике 11 находится константа, определяемая количеством символов требуемого типа в проверяемой последовательности машинных слов. Затем эта константа пересылается в блок 2 и далее используется по назначению. Использование изобретения существенно сокращает длительность вычислений, что приводит к более эффективному использованию дорогостоящей вычислительной техники. Покажем это. Примем время выполнения стандартной команды равным t . Для анализа и подсчета требуемых символов требуется 5-6 операций. С учетом цикла повторения на анализ последовательности символов длиной П будет затрачено (5-6) единиц времени. В изобретении на весь анализ затрачивается две операции и время анализа составляет 2tj AtH, гдеЛЬ-вреМя выполнения одного элементарного сдвига. Конкретно, при работе, например, со словами двойной длины (двоичная инфор5мания) и П4. С учетом того, что Л-t Я получим j:y-6)tit и . (S-6)tn 64 X, 100-12 дЬ h 3t Таким образом, изобретение позвопяе повысить быстродействие процессора лри решении задач анализа и подсчета симво лов примерно в 10О раз. Формула изобретени Микропрограммный процессор, содержащий арифметико-логический блок, пер- вый выход которого соединен с первым входами блока защиты памяти, блока хранения стгужебной информации и блока управления памятью,блок синхронизации, блок микропрограмного управления, первый вход которого соединен с первым вы ходом блока хранения служебной информации, блок памяти выход которого соед нен со вторым входом блока управления памятью, причем первый вход арифметика логического блока и вход блока памяти соединены с выходами блока управления памятью, блока защиты памяти и со вторым выходом блока хранения служебной информации, третий и четвертый выходы которого соединены со вторыми входами соответственно арифметико-логического блока и блежа защиты памяти, вторые входы блока микропрограмного управ/юния и блока хранения служебной информации, третий вход арифметико-логичес16кого блока соединены с первым выходом блока синхронизации, второй и третиЛ выходы которого соединены с третьими входами соответственно блока управления пам5ггью и блока защиты памяти, а группа выходов блока микропрограммного управления является группой выходов процессора, отличающийся тем что, с целью повышения быстродействия, он содержит блок анализа и подсчета символов данных, выполненный в виде узла формирования управляющих сигналов, схемы сравнения, элемента И и счетчика, причем выход узла формирования управляхяцих сигналов соединен с первыми входами схемы сравнения, элемента И и счетчика, выход схемы сравнения соединен со вторым входом элемента И, вьнход которого соединен со вторым входом счетчика, а вход узла формирования управляющих сигналов, втсфой вход схемы сравнения и выход счетчика соединены соответственно с выходом блока микропрограммного управления, со вторым выходом арифметико-логического блока и с третьим входом блока хранения служебной информации. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР NO 4740О8, кл. Q Об 9/12, G 06 f 11/00, 1972. 2,Процессор ЭВМ ,Под общей редакцией А. М. Ларионова, М., Статистика, 1975, с. 4, рис, 1.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Вычислительная машина со структурной интерпретацией входного языка | 1971 |

|

SU513567A2 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Авторы

Даты

1978-11-15—Публикация

1976-07-08—Подача