1

Изопретеиис относится к области вычислительной техники и может использоваться п цифровых вычислительных машинах и устройствах, построе} ных на основе больших интегральных схем.

Известен цифровой функциональный преобразователь 1, содержащий счетчик, блок ностояниой иамяти. дешифратор, логические элементы И и ИЛИ. Это устройство иозволяет ири восироизведении совмещать процессы поразрядного ввода кода аргумента и иоразрядного формирования кода значения воспроизводимой функции.

Однако на входе и Bbixozie такого устройства информация представлена различными кодами, что не позволяет использовать очередные разряды кода воспроизводимой функции в качестве очередных разрядов аргумента в других устройствах, воспроизводяHiHx другие функциональные зависимости.

Наиболее близким по техннческой сущ-, ности и достигаемому эффекту к настоящему изоб;ч.тению яв.1яется уепроИство 2, содержащее реверсивный счетчик, первый вход которого соединен с управляющим входом устройства, а выходы через дешифратор соединены со входами блока коммутации, первая и вторая группа выходов которого еоединена соответственно через первый и второй элементы ИЛИ с первыми входами первого и второго эле.ментов И, вторые входы которых соединены со вторым управляющим входом устройства, а выходы - с первым и вторым вы.ходо.м устрой етва.

Недостатком указанного устройства является низкое быстродействие.

Целью настоящего изобретения является увеличение быстродействия устройства.

Указанная цель достигается тем, что в устройство введены третий и четвертый элементы И, первые входы которых соедиьены с третьим. унраЕияющим входом устройства, вторые входы которых соединены соответственно с нервьим и вторым входом аргумента, а выходы соответственно соединены со вторым и третьим вхо.:1ом реверсиBHort) счетчика, npii iTOM выход четвертого элемента И соединен с доно.1ните,1)Ны.м входом деннфрато1)а.

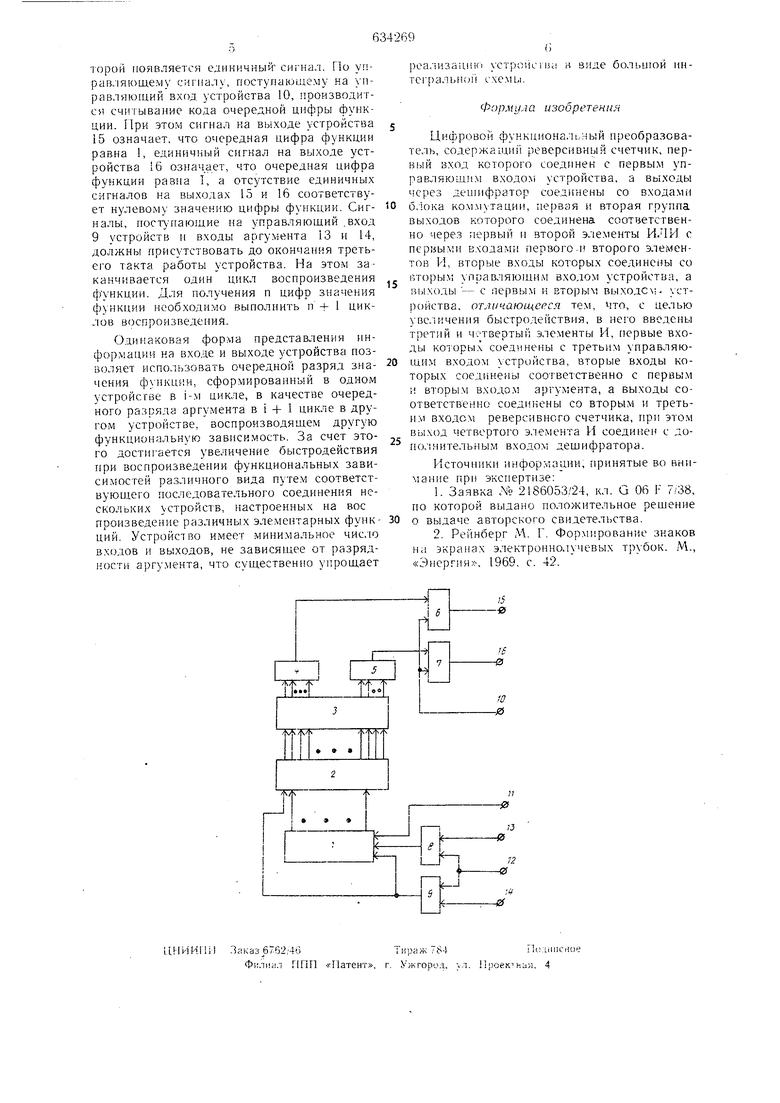

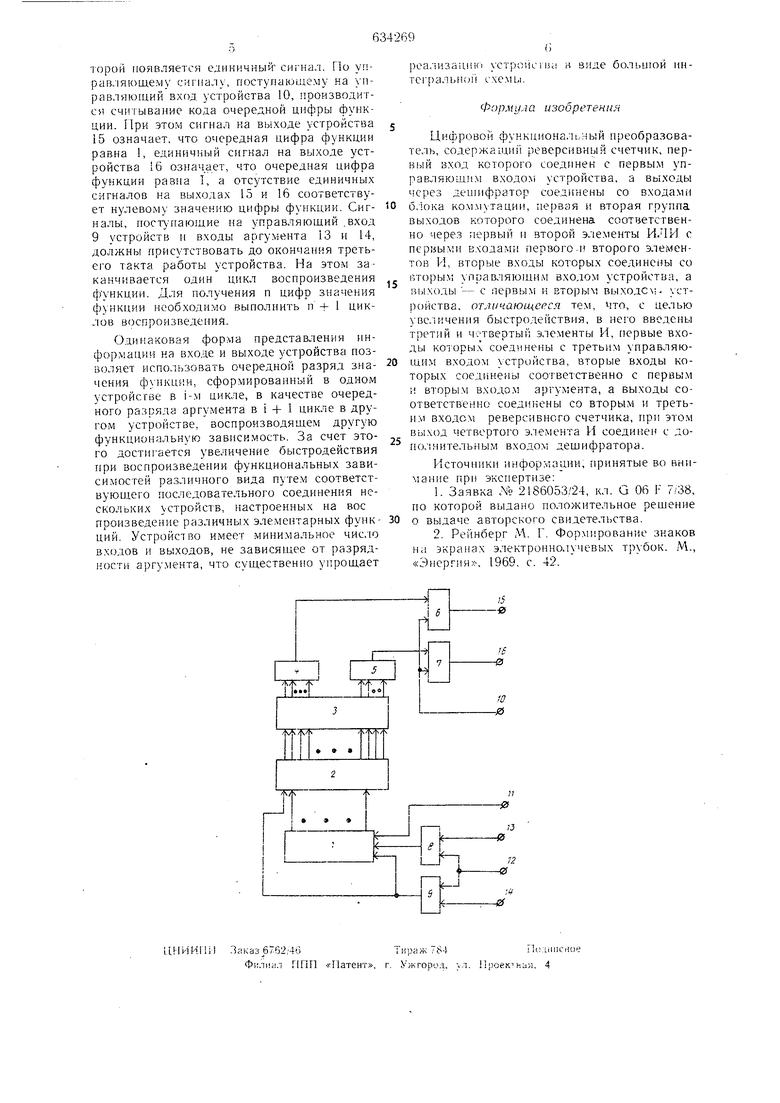

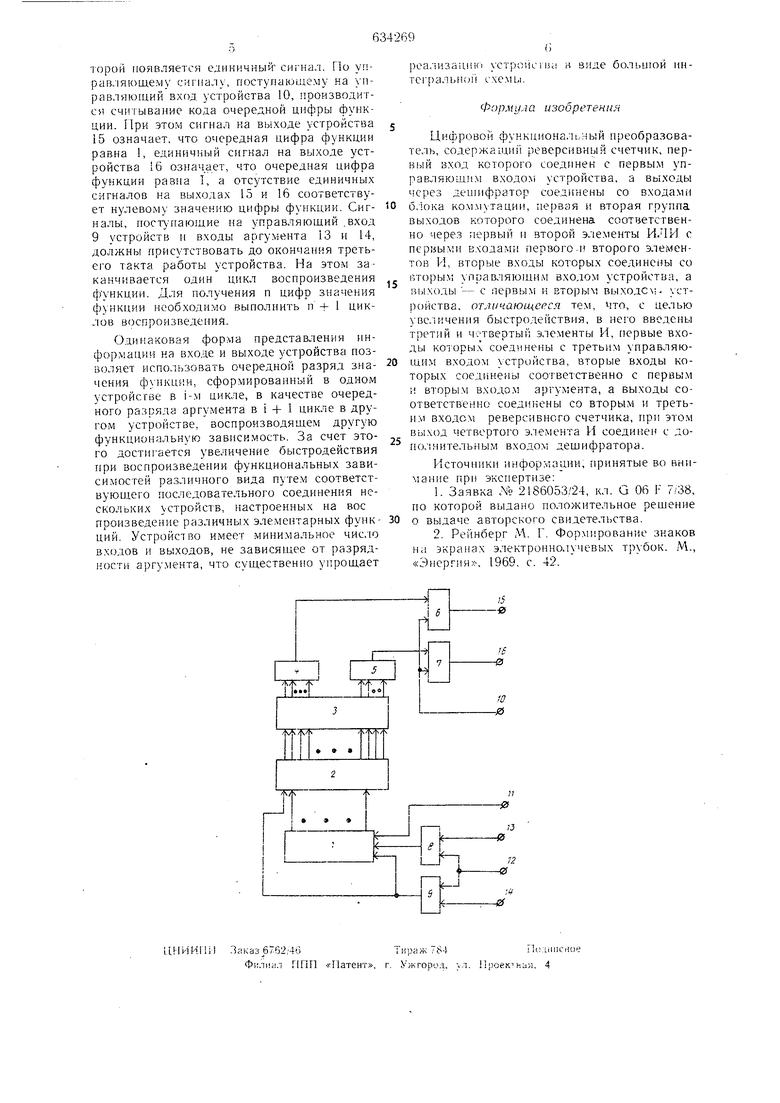

Цифровой функциональный преобразовате.1ь, структурная схема которого представлена на чертеже, содержит реверсивный счетчик 1, дешифратор 2, блок коммутации 3 и элементы ИЛИ 4 и 5, элементы И 6Ч-9. управляющие входы устройства 0-12, входы аргумента 3 и 14, выходы устройства 15 и 16.

Реверсивный счетчик 1 имеет п + 2 двоичных разрядов, где п - разрядность аргумента. Дешифратор 2 имеет п + 3 входов и 2 2 выходов. Блок коммутации 3, эле.менты ИЛИ 4 и 5, а также элементы И 12 и 3 в совокупности выполняют функцию постоянной запоминаюш,ей .матрицы. Необходимая информация записывается в запоминающую матрицу на стадии изготовления устройства и сводится к подключению выходов дещифратора 2 ко в.ходам элементов ИЛИ 4 и 5 с помош.ью блока коммутации 3. Исходными данными для записи информации является таблица значений Ук(Х|,) аргумента и функции, где k у 0,1,...,. Далее вводят обозначения Ха - код аргумента, содержащий только i старших разрядов, которые при рассмотрении их как целого i-разрядного числа представляют величину о. Напри.чер, код 1011 АА обозначается через Xi 1, где А - еще не поступившие разряды аргу.мента. Производятся следующие вычисления.

Ir-i

1. Каждому значению Х,

ставится в соответствие целое число

rV i - О

к I Ч 1 l и,,...,/.1)

где В - целая часть числа В, g - показатель веса младшего разряда кода функции.

2.Определяют значения

j. 2Yr(k 0,1,....2- 1)

3.Каждому значению Хч ставят в соответствие целое число, определяе.мое по рекуррентным формулам

/ Л чЛ-1 ,, .Ai. г max(/,,-,, Y;.K , Угк,-:) .l..-ьY.. Н--

причем у-, О {; п-1,п-2,...,2; k 0,1,...,2- -))

4.Определяют значения ,/rj ,lj цифр функции, которые соответствуют коду, численно равному j на входах дешифратора 2. Для этого используют формулы:

,

i) U 1) /Ь%к Y,,(i 3,4n;

k 0,1,...,2 -1)

„..W-O .

- 2 (1 - 3,4n;

,«2П2., K(k 0,1,...,2-1)

Ьсли /Ij 1, TO j-й выход дешифратора подключают ко входу элемента ИЛИ 5, если /jj -- , то j-й выход дешифратора подключают ко входу элемента ИЛИ 6, если /( О, то j-й выход дещифратора не подключают ни к одному из элементов ИЛИ 5,6.

Устройство предназначено для воспроизведения ,.абсолютная величина максимального элементарного приращения Л 2 vY -Yvimax которых не превышает единицу в области определения. К таким фупкция.м относятся, например, Y sinX. Y-c:osX, Y arectgX, Y --- ЕпХ (), () и др.

Устройст13о работает следуюи им образом.

В исходном состоянии в млад1.ие.м раз|эяде реверсивного счетчика 1 записана 1, а в остальных разрядах - О, в каждом i-м цикле воспроизведения на входы аргумента 13 и 14 поступает одна очередная цифра аргумента, начиная со старших разрядов. Аргумент представлен в симметричной избыточной двоичной системе счисления с цифрами {1,,0,1}. Цифра 1 представляется единичным сигналом на шине аргумента 13, цифра - на тине аргумента 14, а цифре О соответствует отсутствие сигналов на входах аргумента 13 и 14. На управляюш.ие входы устройства 10, 11 и 12 в каждом цикле последовательно во времени поступают управляющие сигналы. В нервом такте каждого i-ro

цикла по управ.ляющему сигналу, пост пающему на управляющий вход 11, производится сдвиг инфор.мации, записанной в реверсивном счетчике 1. При этом в реверсивном счетчике 1 фор.мируется код, i + i-й разряд которого равен I, а значения остальных м.аадших разрядов определяются значениями цифр аргумента, поступающих на входы аргумента 13 и 14 в i-1 предыдущих циклах (первым разрядо.м в реверсивном счетчике 1 считается .младший разряди.

По управляющему сигналу, поступающему на управляющий вход устройства 12, осуществляется прием кода очередной цифры аргумента. Если цифра аргумента равна 1, то срабатывает элемент И 8 и сигнал с выхода элемента И 6 осуществляет прибавление 1 к содержимому реверсивного счетчика 1. Если цифра аргумента равна I, то срабатывает элемент И 9 и из содержимого регзерсивного счетчика 1 вычитается 1. При нулевом значении цифры аргумента реверсивный счетчик не из леняет своего состояпия. Код с выходов реверсивного счетчика I li сигнал с выхода элемента И 9 поступают на входы дешифратора 2 и определяют номер выходной шииы дешифратора 2, на ко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для формирования сигналов датчика дистанционных синхронных передач | 1984 |

|

SU1223243A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU877529A1 |

| Функциональный преобразователь | 1980 |

|

SU957218A1 |

| Аналого-цифровой квадратор | 1983 |

|

SU1120374A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

Авторы

Даты

1978-11-25—Публикация

1976-03-03—Подача