(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1983 |

|

SU1140118A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для вычисления квадратного корня | 1976 |

|

SU642706A1 |

| Вычислительное устройство | 1983 |

|

SU1170448A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для вычисления интегра-лОВ | 1976 |

|

SU840901A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для решения р-мерных задачМАТЕМАТичЕСКОй физиКи | 1979 |

|

SU824216A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

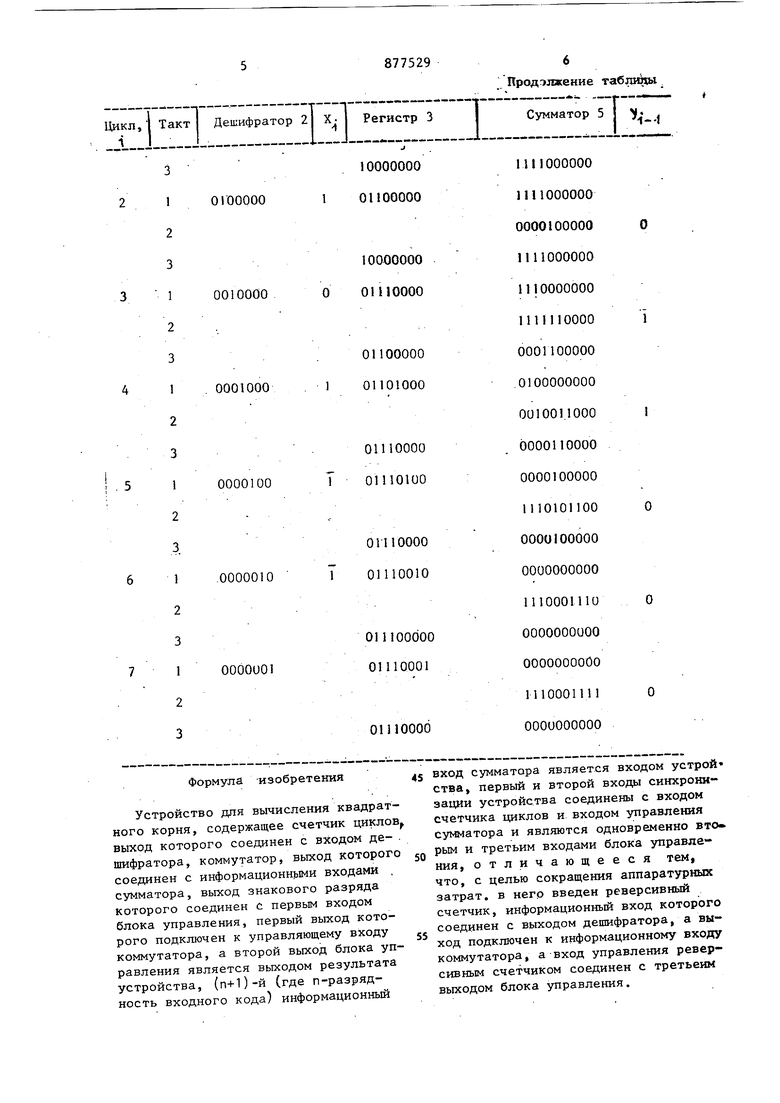

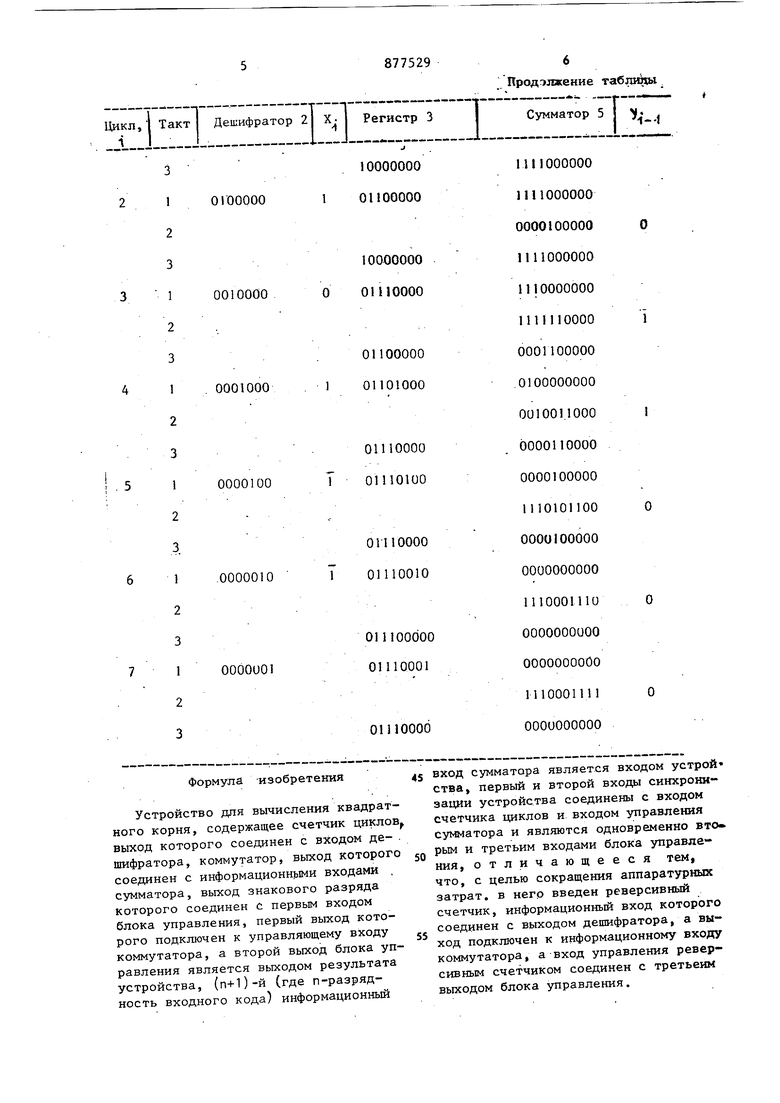

Изобретение относится к автоматик и вычислительной технике и может быт применено в устройствах для извлечения квадратного корня из числа, пред ставленного последовательным кодом. Известно устройство для вычислени квадратного корня, содержащее сумматоры, регистры, коммутаторы, счетчики l. Однако известное устройство обладает низким быстродействием для случая, когда операнд поступает в устро ство поразрядно. Наиболее близким к предлагаемому является/устройство для вычисления квадратного корня, содержащее счетчик циклов, депшфратор, коммутатор, сумматор 2, Недостатком известного устройства являются значительные аппаратурные затраты. Цель изобретения - сокращение аппаратурных затрат на реализацию устройства, Поставленная цель достигается тем, что в устройство для вычисления квадратного корня, содержащее счетчик цик лов, выход которого соединен с входом дешифратора, коммутатор, выход которого соединен с информационными входами сумматора, выход знакового разряда которого соединен с первым входом блока управления, первый выход которого подключен к управляющему входу коммутатора, а второй выход блока управления является выходом результата устройства, (п-«-1)-й (где п - разрядность входного кода) информационный вход сумматора является входом устройства, первый и второй входы синхронизации устройства соединены с входом счетчика циклов и входом управления сумматора и являются одновременно вторым и третьим входами блока управления, введен реверсивньй счетчик, информационный вход которого соединен с выходом дешифратора а выход подключен к информационному входу коммутатора, а вход управления реверсивньм счетчиком соединен с третьим выходом блока управления. Блок управления содержит элемент ИЛИ, два элемента И и триггер, при чем первый и второй входы элемента ИЛИ являются соответственно вторьм и третьим входами блока управления, а выход подключен к первым входам первого и второго элементов И, выходы которых подключены.к третьему. выходу блока управления, второй прямой и второй инверсный входы соответственно первого и второго элементов И, а также информационный вход триггера подключены к первому входу блока управления, соединенного с его первым выходом, тактируюнщй вход три гера подключен к первому входу элемента ИЛИ и является вторым входом блока управления. На фиг. 1 представлена блок-схема устройства для вычисления квадратног корня;,на фиг, 2 - схема блока управ ления. Устройство содержит счетчик 1 цик лов, дешифратор 2, реверсивный счетчик 3, коммутатор 4, сумматор 5, бло 6 управления, вход 7 устройства, выход 8 результата устройства, входы 9 синхронизации устройства, элемент ИЛИ 10, элементы И П и 12, триггер 13. Устройство работает следующим обраэом, В исходном состоянии в сумматоре 5 и счетчике 3 записаны нули, а в счетчике 1 циклов записана единица. В первом такте каждого i-го цикла вычисления (i l,2...,.n+li цифра опе ранда, имеющая вес 2 и принимающая значения из множества 1, О, ij приб ляется в (п+1)-й разряд сумматора 5. Затем в (п+2-)-й разряд счетчика 3 с выхода дешифратора 2 прибавляется единица, если в знаковом разряде сум матора 5 записан ноль, или вычитаетс единица, если в знаковом разряде сум матора 5 записана единица.

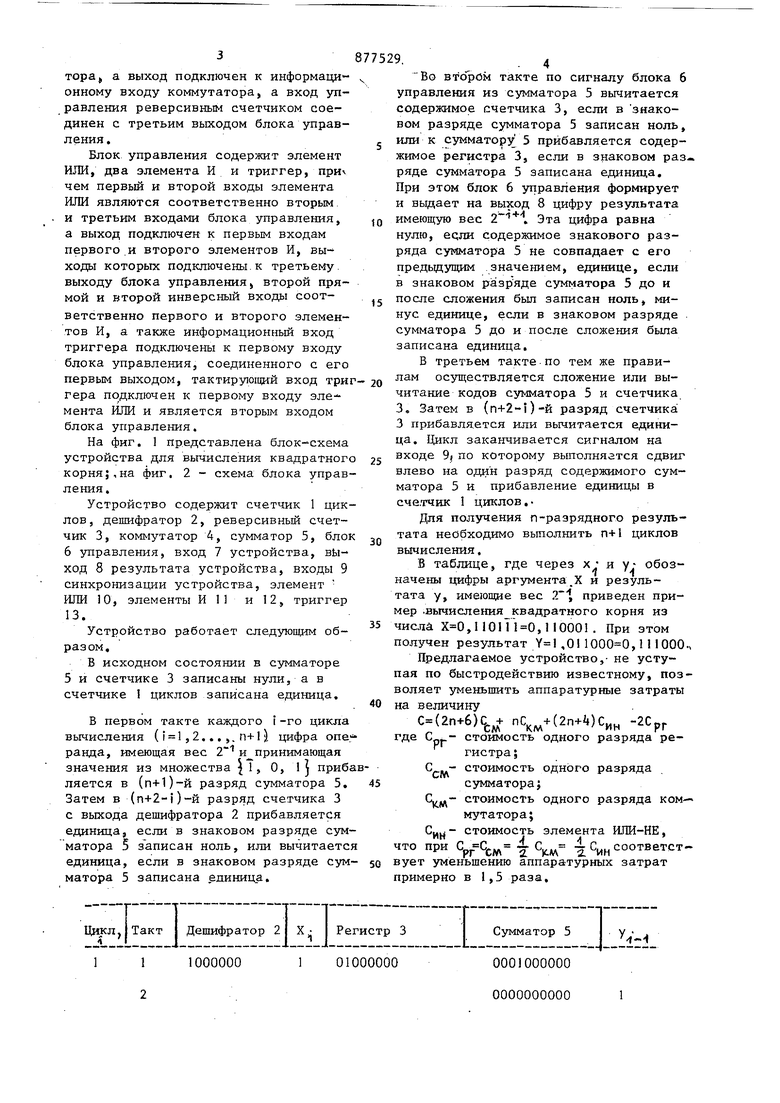

0000000000 9.4 Во втором такте по сигналу блока 6 управления из сумматора 5 вычитается содержимое счетчика 3, если в знаковом разряде сумматора 5 записан ноль, или к сумматору 5 прибавляется содержимое регистра 3, если в знаковом разряде сумматора 5 записана е,циница. При этом блок 6 управления формирует и вьщает на выход 8 цифру результата имеющую вес . Эта цифра равна нулю, ецли содержимое знакового разряда cyieJMaTOpa 5 не совпадает с его предьщущим значением, единице, если в знаковом разряде сумматора 5 до и после сложения бьш записан ноль, минус единице, если в знаковом разряде . сумматора 5 до и после сложения была записана единица. В третьем такте.по тем же правилам осуществляется сложение или вычитание кодов сумматора 5 и счетчика 3, Затем в (п+2-1)-й разряд счетчика: 3 прибавляется или вычитается единица. Цикл заканчивается сигналом на входе 9j по которому выполнягтся сдвиг влево lia один разряд содержимого сумматора 5 и прибавление единицы в сче.тчик 1 циклов. Для получения п-разрядного результата необходимо выполнить п+1 циклов вычисления. В таблице, где через х и у- обозначены цифры аргумента Х и результата у, имеющие вес 2 приведен пример .вычисления квадратного корня из числа ,110111 0,11000. При этом получен результат ,01 ,111000. Предлагаемое устройство,- не уступая по быстродействию известному, позволяет уменьшить аппаратурные затраты на величину С() (2п+)С, -2Срг где ,- стоимость одного разряда регистра ; стоимость одного разряда сумматора С„цд- стоимость одного разряда ком- мутатора; ИЙ стоимость элемента ИЛИ-НЕ, что при . i- Cj, -i соответствует уменьшению аппаратурных затрат примерно в 1,5 раза.

Формула изобретения

Устройство для вычисления квадратного корня, содержащее счетчик циклов,, выход которого соединен с входом де- . шифратора, коммутатор, выход которого соединен с информационньми входами . сумматора, выход знакового разряда которого соединен с первым входом блока управления, первый выход которого подключен к управляющему входу коммутатора, а второй выход блока управления является выходом результата устройства, (п+1)-й (где п-разрядность входного кода) информационный

Продолжение таблгаол ,

5 вход Сумматира n,.-. ,

ства, первый и второй входы синхронизации устройства соединены с входом счетчика циклов и входом управления сумматора и являются одновременно вто J. рым и третьим входами блока управления, отличающееся тем, что, с целью сокращения аппаратурных затрат, в негр введен реверсивный счетчик, информационный вход которого соединен с выходом дешифратора, а выход подключен к информационному входу коммутатора, а вход управления реверсивным счетчиком соединен с третьеим выходом блока управления.

Авторы

Даты

1981-10-30—Публикация

1979-11-14—Подача