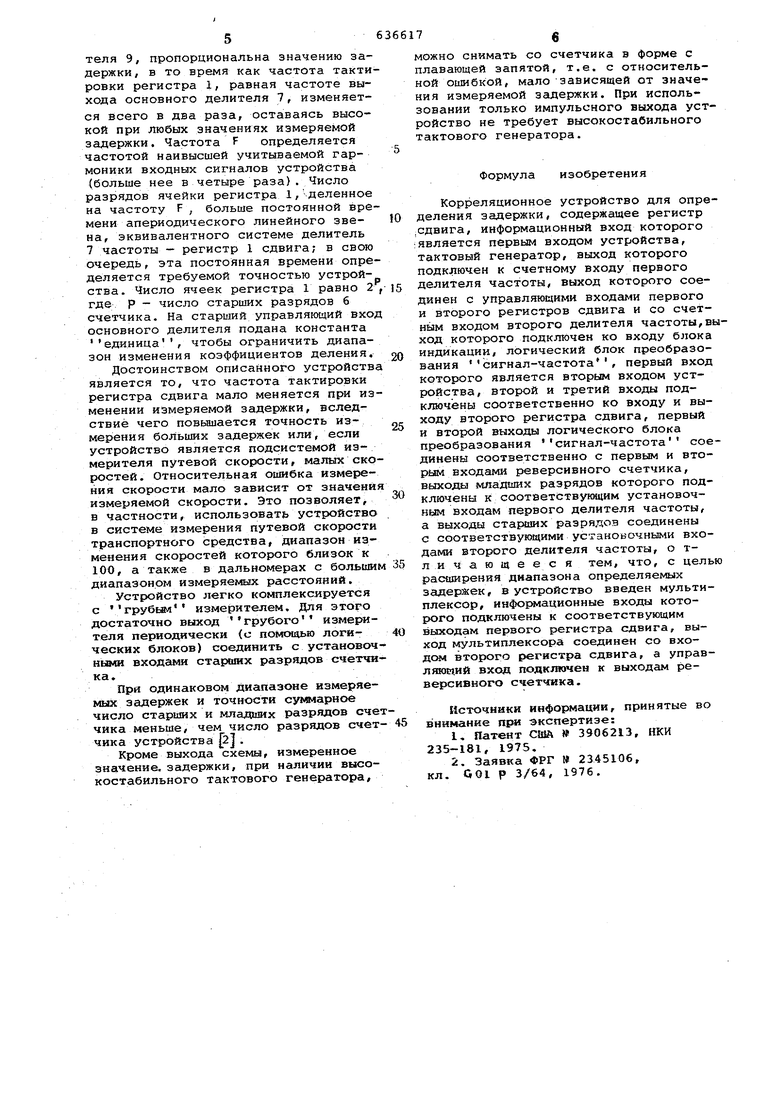

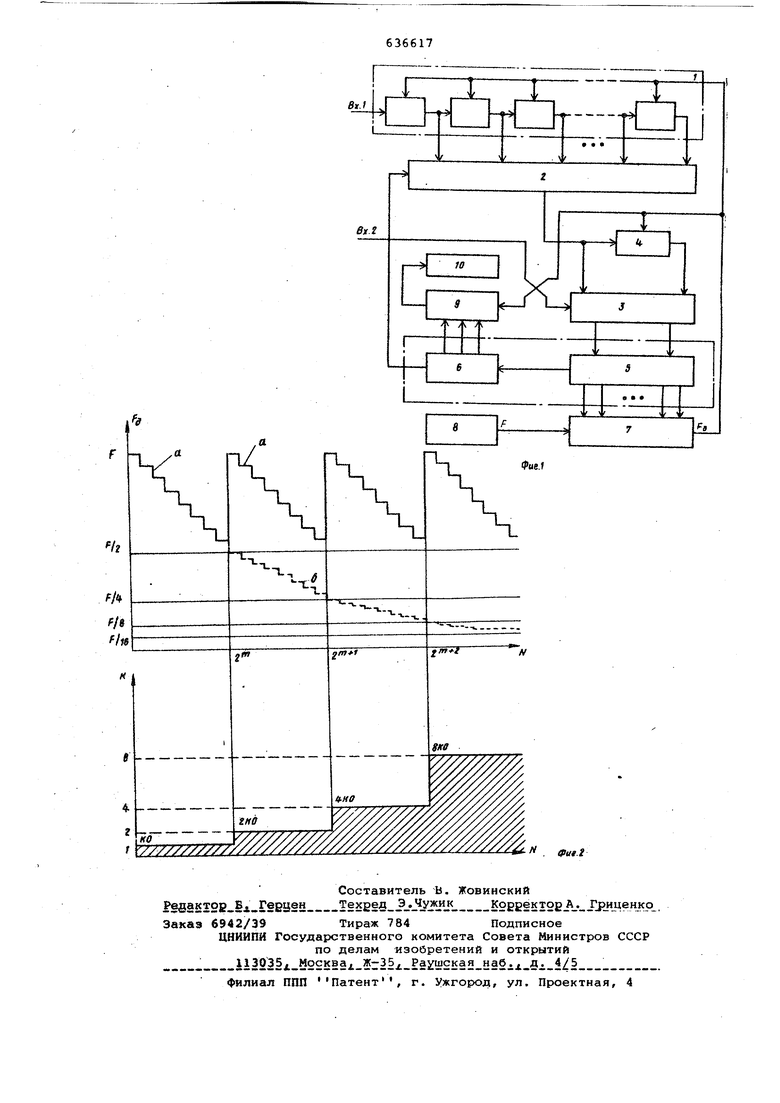

ходы младаиих разрядов которого подклю чены к соответствующим установочным входам первого делителя частоты, а вы ходы старших разрядов соединены с. соо ветствующими установочными входами вт рого делителя частоты.. Недостатком этих устройств, выполненных с использованием регистров сдвига, является малый диапазон измеряемых задержек, так как при больши задержках частота сдвига в регистрах получается малой, что отрицательно сказывается на форме корреляционной функции и делает систему менее точной. В то же время схемы без регистров сдвига теряют свое значение/ так как имеют значительно большие габариты, меньшую надежность и вьасокую стоимость по сравнению со схемами, содержащими регистры сдвига на современных приборах с зарядовой связью или динамические сдвиговые регистры средней интеграции, изготовленные по МОП или близкой технологии (до 256 разрядов на одну микросхему). Целью настоящего изобретения является расширение диапазона определяемых задержек. Указанная цель достигается тем, что в устройство введен мультиплексор, информационные входы которого подключены к соответствующим выходам первого регистра сдвига, вьаход мульти плексора соединен со входом второго регистра сдвига, а управляющий вход подключен к выходам реверсивного сче чика. На фиг. 1 показана функциональная схема устройства; на фиг. 2 - диаграмма, поясняющая процесс задержки опорного сигнала, на которой введены следующие обозначения F - частота на выходе генератора 8, а - изменени частоты на выходе делителя 7; f - и менение частоты на выходе делителя 9 К - число разрядов регистра сдвига, включенных последовательно; КО - чис ло разрядов ячейки регистра 1 ; N суммарное состояние счетчика 11 w - число младших разрядов группы 5 счет чика 11. Первый вход устройства (цепь опор ного сигнала) соединен со входом ре гистра 1 сдвига, выход каждой ячейки регистра сдвига, кроме последней, соединен со входом следующей ячейки, выход каждой ячейки соединен также со входом мультиплексора 2, причем N, 2N., где Ыц. - число разрядов между входом регистра 1 и выходом ячейки с номером К; N, - число ра рядов между входом регистра и выходом предыдущей ячейки; выход мультиплексора 2 соединен со входом логиче кого блока 3 преобразования сигнал частота и второго регистра 4 сдвига, выход которого соединен с другим входом логического блока 3; третий вход логического блока 3 соединен со вторым входом устройства; выходы логического блока 3 соединены со счетными входами реверсивного счетчика 11, выход последнего разряда из группы 5 младших разрядов соединены со счетными входами группы б старших разрядов реверсивного счетчика; выходы группы 5 младших разрядов счетчика соединены с управляющими входами делителя 7 частоты; вход делителя 7 соединен с выходом тактового генератора 8, а выход с управляющими входами регистров 1 и 4 сдвига и со входом второго делителя 9 частоты выход последнего соединен со входом блока 10 индикации значения задержки. Установочные входы Делителя 9 соединены с выходами старших разрядов 6 счетчика 11, которые соединены также с управляющими входами мультиплексора 2. На входы регистра 1 с ячейками и логического блока 3 подаются соответственно опорный и исходный сигналы. При этом на выходах логического блока 3 формируются сигналы, частоты которых пропорциональны значениям взаимнокорреляционной функции опорного и исходного сигналов в двух точках, соответствукигщх двум мало отличающимся значениям задержки опорного сигнала. Разность частот этих сигналов определяет направление движения к точке мaкcимsмa корреляционной функции и равна нулю,когда задержка опорного сигнала соответствует этому максимуму и, следовательно, временному сдвигу исходного и опорного сигналов. При рассогласовании состояние счетчика 11 меняется, вызывая изменение частоты на выходе делителя 7. ЕСЛИ все младшие разряды 5 счетчиков 11 оказываются заполненньми, что соответствует делению частоты генератора 8 пополам, то следующий импульс с логического блока 3 сбрасывает млгщшие разряды счетчика 11 и изменяет на единицу состояние старших разрядов 6. Это, в свою очередь, приводит к тому, что: -коэффициент деления делителя 7 становится равным единице; -коэффициент деления делителя 9 увеличивается в два раза; -с помощью мультиплек9Ора 2 включается следующая ячейка регистра 1 сдвига, и число включенных разрядов увеличивается таким образом в два раза. Если продолжается движение к экстремуму в том же направлении (слева направо), то процесс повторяется. Если движение происходит в обратном направлении (справа налево), то последовательность событий соответственно изменяется. Из диаграммы (фиг.2) видно, что частота на выходе устройства,совпадающим с выходом вспомогательного делителя 9, пропорциональна значению задержки, в то время как частота такти ровки регистра 1, равная частоте выхода основного делителя 7, изменяется всего в два раза, оставаясь высокой при любых значениях измеряемой задержки. Частота F определяется частотой наивысшей учитываемой гарМОНИКИ входных сигналов устройства (больше нее в четыре раза). Число разрядов ячейки регистра 1,деленное на частоту F , больше постоянной вре мени апериодического линейного звена, эквивалентного системе делитель 7 частоты - регистр 1 сдвига; в свою очередь, эта постоянная времени опре деляется требуемой точностью устройства. Число ячеек регистра 1 равно 2 где р - число старших разрядов б счетчика. На старший управляющий вхо основного делителя подана константа единица, чтобы ограничить диапазон изменения коэффициентов деления. Достоинством описанного устройств является то, что частота тактировки регистра сдвига мало меняется при из менении и;змеряемой задержки, вследствие чего повышается точность измерения больших задержек или, если устройство является подсистемой измерителя путевой скорости, малых ско ростей, относительная ошибка измерения скорости мало зависит от значени измеряемой скорости. Это позволяет, в частности, использовать устройство в системе измерения путевой скорости транспортного средства, диапазон изменения скоростей которого близок к 100, а также в дальномерах с больим диапазоном измеряемых расстояний. Устройство легко комплексируется грубым измерителем. Для этого грубого измеридостаточно выход теля периодически (с помощью логических блоков) соединить с установоч ными входами старших разрядов счетчи ка. При одинаковом диапазоне измеряемых задержек и точности суммарное число старишх и младших разрядов сче чика меньше, чем число разрядов счет чика устройства (2 . Кроме выхода схемы, измеренное значение, задержки, при наличии высокостабильного тактового генератора. можно снимать со счетчика в форме с плавающей запятой, т.е, с относительной ошибкой, малоЗависящей от значения измеряемой задержки. При использовании только импульсного выхода устройство не требует высокостабильного тактового генератора. Формула изобретения Корреляционное устройство для определения задержки, содержащее регистр .сдвига, информационный вход которого :является первым входом устройства, тактовый генератор, выход которого подключен к счетному входу первого делителя частоты, выход которого соединен с управляющими входами первого и второго регистров сдвига и со счетным входом второго делителя частоты,выход которого подключен ко входу блока индикации, логический блок преобразования сигнал-частота , первый вход которого является вторым входом устройства, второй и третий входы подкгаочены соответственно ко входу и выходу второго регистра сдвига, первый и второй выходаа логического блока преобразования сигнал-частота соединены соответственно с первым и вторым входами реверсивного счетчика, выходы младших разрядов которого подключены к соответствующим установочным входам первого делителя частоты, а выходы старших разрядов соединены с соответствующими установочными входами второго делителя частоты, о тл и чающееся тем, что, с целью расширения диапазона определяемых задержек, в устройство введен мультиплексор, информационные входы которого подключены к соответствующим выходам первого регистра сдвига, выход мультиплексора соединен со входом второго регистра сдвига, а управЛЯЮН1ИЙ вход подключен к выходам реверсивного счетчика. источники информации, принятые во внимание при экспертизе: 1,Патент США 3906213, НКИ 235-181, 1975, 2.Заявка ФРГ № 2345106, кл. 001 р 3/64, 1976,

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| Корреляционное устройство для определения времени задержки | 1980 |

|

SU883914A1 |

| Корреляционное устройство для определения задержки | 1982 |

|

SU1051545A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

Авторы

Даты

1978-12-05—Публикация

1976-11-29—Подача