ной кривой имеет колебательный характер, т.е. имеет несколько экстремумов. Для определения времени задержки необходимо отыскание максимального экстремума корреляционной функции

Недостаток данного устройства возмохсность определения времени задержки по неосновному экстремуму, соответственно, невысокая точность измерения, если на исследуемом участке имеется несколько выбросов корреля- ционной функции .

Цель изобретения - повышение точности определения времени задержки.

Поставленная цель достигается тем, что в корреляционное устройство для измерения задержки, содержащее первый регистр сдвига, информационный вход которого является первым входом устройства, а выходы первого регистра сдвига подключены к соответствующим информационным входам первого мультиплексора, тактовый генератор, выход которого подключен ксчетному входу делителя частоты, выход которого соединен с управляющими входами первого и второго регистров сдвига и с тактовым входом первого блока индикации, преобразователь напряжение-частота, первый вход которого является вторым входом устройства, второй вход подключен к выходу мультиплексора и входу второго регистра сдвига, третий вход преобразователя напряжение-частота соединен с выходом второго регистра сдвига, управляющий вход мультиплексора соединен с выходом реверCHBtJoro счетиика, первый и второй выходы преобразователя напряжениечастота соединены соответственно с первым и вторым входами реверсивного счетчика, выходы старших разрядов которого подключены к соответствующи информационнымвходам блока индикации , а выходы младших разрядов соединены с управляющими входами делителя частоты, введены третий и четверть- й регистры сдвига, второй мультиплексор, второй преобразователь напряжение-частоТч, второй реверсивный счетчик, второй делитель частоты, второй блок индикации, компаратор, два интегратора, два элемента И, бло сравнения, входы которого подключены соответственно к выходам первого и второго реверсивных счетчиков, выход блока сравнения соединен с первыми входами первого и второго элементов И, выход первого элемента И подключе к входу сложения первого реверсивного счетчика, выход второго элемента И - к входу вычитания второго реверсивного счетчика, вторые вхо.цы элементов И подключены соответственно к первому и второму выходам компаратора, входы которого соединены соответственно с выходами первого и второго интеграторов, вход первого

интегратора соединен со вторым выходо первого преобразователя напряжениечастота, вход второго интегратора подключен к первому выходу второго преобразователя напряжение-частота, первый вход которого соединен со вторым входом устройства, вход третьегорегистра сдвига подключен к первому входу устройства, выходы третьего регистра соединены с соответствуккаими информационными входами второго мультиплексора, управляющий вход второго мультиплексора подключен к выходу второго реверсивного счетчика, выходы 1-1ладших разрядов которого подключены к установочным входам второго делителя частоты, информационный вход которого подключен к выходу тактового генератора, а выход - подключен к тактовому входу второго блока индикации и к управляющим входамтретьего и четвертого регистров сдвига, выход второго мультиплексора соединен со входом четвертого регистра сдвига и со вторым входом второго преобразователя напряжение-частота, третий вход которого подключен к выходу четвертого регистра сдвига, первый и второй выходы преобразователя напряжение-частота подключены соответственно к управляющим входам реверсивного счетчика.

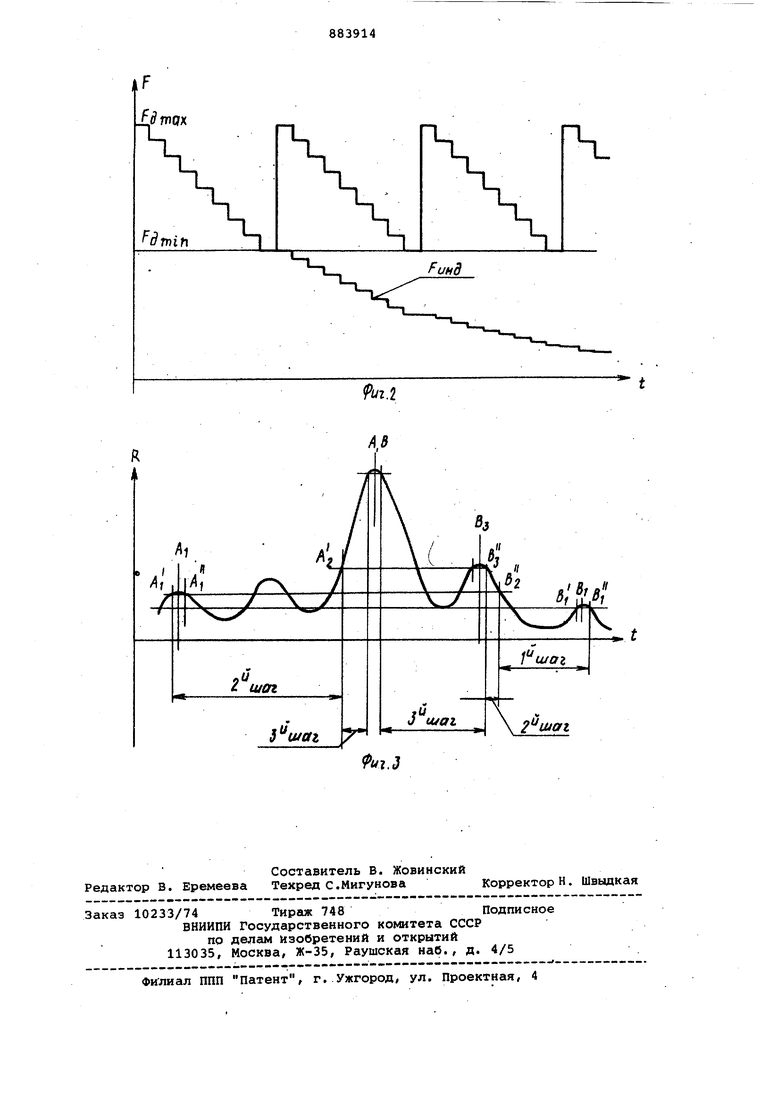

На фиг. 1 - схема предлагаемого устройства на фиг. 2 - зависимость тактовой частоты Fg ичастоты индикации от значения задержки; на фиг. 3 - форма корреляционной кривой R(t) и последовательность работы устройства при движении к максимальному экстремуму.

Устройство содержит первый и второй канал 1 и 2 определения экстремума корреляционной функции, первый и третий регистры 3 сдвига, мультиплексоры 4, преобразователи 5 напряжение-частота, второй и четвертый регистры б сдвига, реверсивные счетчики 7, младшие разряды 8 счетчиков, старшие разряды 9 счетчиков, делители 10 частоты, тактовый генератор 11) блок 12 индикации блок 13 сравнения, элементы И 14 и 15, интеграторы 16 и 17, компаратор 18.

В предлагаемом устройстве первый вход соединен с первым входом канала 1 определения экстремума и первым входом канала 2 .определения экстремума, второй вход устройства соединен соответственно со вторУми входами каналов 1 и 2.

Первый вход в каждом канале определения экстремума (цепь опорного сигнала соединен со входом регистра сдвига 3, выход каждой ячейки регистра сдвига 3, кроме последней, соединен со входом следуквдей ячейки, выход каждой ячейки соединен также со входом мультиплексора 4, причем , , где число разрядов

между входом регистра 3 и выходом (Ячейки с номером число разрядов между входом регистра и выходом предьодущей ячейки; выход мультиплексора 4 соединен со входом преобразователя и регистра сдвига 6, выход которого соединен с другим входом преобразователя 5, третий выход которого соединен со вторым входом канала, выходы преобразовател 5 соединены со счетными входами реверсивного счетчика 7, выход последнего разряда из группы младших разрядов 8 соединен со счетными входами группы старших разрядов 9 реверсивного счетчика, выходы младших разрядов 8 счетчика 7 соединены с установочными входами делителя частоты 10, вход которого соединен с выходом тактового генератора 11, а выход - с управляющими входами регистров сдвига 3 и 6 и входом блока индикации 12, выходы старших разрядов 9 реверсивного счетчика 7 соединены с блоком индикации 12 и управляющими входами мультиплексора 4, кроме того, выходил старших разрядов реверсивных счетчиков 7 каждого из каналов соединены с соответствующими входами блока 13 сравнения, выход которого соединен с первыми входами элементов И 14 и 15, первый выход преобразователя 5 канала 1 через интегратор 16, а второй выход преобрзователя 5 канала 2 через интегратор 17 подключены к соответствующим входами компаратора 18, один выход которого соединен с входом элемента И 14, а второй - с входом элемента И 15, выход элемента И 14 соединен -с первым входом (входом сложения реверсивного счетчика 7 канала 1, а выход элемента И 15 - со вторым входом (входом вычитания реверсивного счетчика 7 канала 2.

Устройство работает следующим образом.

С включением в работу производится начальная установка реверсивного счетчика 7 канала 1, соответствующая минимально возможному значению задержки, число, записанное в старших разрядах 9 реверсивного счетчика 7, коммутирует с .регистра 3 соответствующую ячейку, аналогичным образом в канале 2 устанавливается максимально возможное значение задержки.На входы регистров 3 обоих каналов и преобразователей 5 подаются соответственно опорный и исходный сигналы. При этом на выходах преобразователя 5 в Кс1ждом канале формируются сигналы, частоты которых пропорциональны.значениям взаимокорреляционной функции опорного и исходного сигналов в двух точках, соответствующих двум мало отличающимся значениямзадержки опорного сигнала ( определяемым числом разрядо

регистра сдвига 6). Разность этих частот сигналов определяет направление движения к точке экстремума и равна нулю, когда задержка соответствует положению экстремума. При рассогласовании состояние счетчика меняется, вызывая изменение частоты на выходе делителя 10. Если все младшие разряды 8 счетчиков 7 оказываются заполненными, что соответствует максимальному коэффициенту деления час0тоты генератора 11, то следующий импульс на входе реверсивного счетчика 7 сбрасывает младшие разряды счетчика и изменяет на единицу состояние старших разрядов 9. Это, в

5 свою очередь приводит к тому, что коэффициент деления делителя 10 становится минимальным; с помощью мультиплексора 4 включается следующая ячейка регистра сдвига 3, и чис

0 ло включенных разрядов увеличивается таким образом в два раза. Если продолжается движение к экстремуму в том же направлении, то процесс повторяется. Если движение происходит в обратном направлении, то последо5вательность событий соответственно изменяется.

Параллельно анализу корреляционных функци-й преобразователя напряжение-частота 5 производится интег0рирование ординат корреляционной: функции в крайних исследуемых точках интеграторами 16 и 17. В компараторе 18 производится сравнение результатов интегрирования, на соот5ветствующем его выходе вырабатывается сигнал управления, проходящий через соответствующий элемент И 14 или 15 и реверсивный счетчик 7 на вход сложения в первом канале или на

0 вход вычитания во втором канале, тем caNbiM инициируя сближение временных точек, анализируемых в первом и втором каналах. Элементы И 14 и 15 открыты для прохождения сигналов с компаратора до тех пор, пока не нас5тупит равенство результатов в старших разрядах 9 реверсивных счетчиков 7 обоих каналов, после чего оба канала переходят в режим автономной работы по определению максимума корреля0ционной функции.

В блоке индикации (фиг. 2) вырабатывается частота, пропорциональная значению задержки, в то время как частота тактировки регистра 3, рав5ная частоте на выходе делителя 10, изменяется всего в два раза, оставаясь высокой при любых значениях измеряемой задержки.

Последовательность работы устройства при движении к максимуму корре0ляционной функции (максимальному экстремуму)отражена на фиг. 3.

Начсшо анализа соответствует мо-, менту, когда первый канал анализиру(вт экстремум в точке А , а второй

5

канал-экстремум,в точке В. Так как экстремум в точке В меньше экстремума в точке А, сигнал управления с компаратора 18 через элемент И 15 поступает в реверсивный счетчик второго канала, вызывая смещение ана лиэируемого участка влево (1 marj. Так как компаратор 18 вырабатывает сигнал управления по значениям функции в крайних точках Ajj и в , на первом шаге показано, соответственно, перемещение точки . В точке в/ значение корреляционной функции равно значению функции в точке Al , с этого момента компаратор прекращает выдавать сигнал управления на элемент И 15, соответственно второй канал переходит в режим автономного поиска экстремума, постепенно переходя в точку . Как только второй канал переходит к анализу левее точки в1, значение корреляционной функции становится выше, чем фиксируемое интегратором 16, соотве ственно компаратор 18 переключает сигнал управления на другой выход, сдвигая точку анализа первого канала из экстремума А/) вправо. Таким образом, на втором шаге происходит одновременное смещение анализируемых точек в обоих каналах навстречу друг другу, пока второй канал не остановится на фиксации экстремума в точке Bj. ВТОРОЙ канал буДет зафиксирован на экстремуме в точке B-j, пока число в интеграторе 16 не достигнет числа, хранимого в интеграторе 17 (точка . С этого момента начинается третий шаг,«превый канал переходит в режим автономного поиска максимума, а второй принудительно перемещается навстречу.

В момент равенства чисел (одна и та же ячейка в регистрах 3 первого и второго каналов) в старших разрядах 9 счетчиков 7 обоих каналов блок сравнения 13 вырабатывает сигнал, закрывающий элементы И 14 и 15, оба канала переходят в режим автономного поиска максимума корреляционной функции.

Известное устройство при анализе корреляционной функции (фиг. 3) может остановиться на любом из экстремумов , соответственно выдать ошибочный результат,

Предлагаемое двухканальное устройство с дополнительными элементами И, схемой сравнения и компаратором позволяет стягивать канал с анализа промежуточного экстремума, когда соседний канал перейдет к анализу участка, в котором значение корреляционной функции превышает величи этого промежуточного экстремума.

Таким образом, исключаются ошибк определения времени задержки, связанные с фиксацией промежуточных экстремумов, так как можно сделать заключение, что устройство обладает положительным эффектом.

Формула изобретения

Корреляционное устройство для определения времени задержки, содержащее первый регистр сдвига, информационный вход которого является первь5м входом устройства, выходы первого регистра сдвига подключены к соотвётствукнцим информационным входа первого мультиплексора, тактовый генератор, выход которого подключен к счетному входу делителя частоты, выход которого соединен с управляющими входами первого и второго регистров сдвига и с тактовым входом первого блока индикации, преобразовател напряжение-частота, первый вход которого является вторым входом устройства, второй вход подключен к выходу мультиплексора и ко входу второго регистра сдвига, третий вход прерб-г разователя напряжение-частота соединен с выходом второго регистра сдвига, управ71яю1иий вход первого мультиплексора соединен с выходом первого реверсивного счетчика, первый и второй выходы преобразователя напряжение-частота соединены соответственно с первым и вторым входами реверсивного счетчика, выходы старших разрядов которого подключены к соответствующим информационным входам первого блока индикации, а выходы младших рарядов соединены с управляющими входами делителя Чгэстоты, отличающееся тем,что, с целью повышения точности определения времени задержки, в корреляционное устройство введены третий и четвертый регистры сдвига, второй мультиплексор, второй преобразователь напряжениечастота второй реверсивный счетчик, второй делитель частоты, второй блок индикации, компаратор,- два интегратора, два элемента И и блок сравнения, входы которого подключены соответственно к выходам первого и второго реверсивных счетчиков, выход блока сравнения соединен с первыми входами первого и второго элементов И, выход первого элемента И подключен к входу сложения первого реверсивного счетчика, а выход второго элемента И - к входу вычитания второго реверсивного счетчика, вторые входы элементов ,И подключены соответственно к первому и второму выходам компаратсчра, BXOJKI которого соедииешл соответственно с выходами первого и Btoporo интеграторов, вход ,перврго интегратора соединен со вторым выходом первого преобразователя напряжение-частота, вход второго интегратора подключен « первому выходу второго лреобразователя напряжение-частота, первый вход которого соединен со вторым входом устройства, вход третьего регистра сдвига подключен к первому входу устройства выходы третьего регистра соединены с соответствующими информационными входами второго мультиплексора, управляющий вход ВТОРОГО мультиплексора подключен к выходу второго реверсивного счетчика, выходы младших разрядов которого подключены к установочным входам второго делителя частоты, информационный вход которого подключен к выходу тактового генератора, а выход - подключен к тактовому входу второго блока индикации и к уп равляющим входам третьего и четвертого регистров сдвига, выход второПб мультиплексора соединен со входом четвертого регистра сдвига и со вторым входом второго преобразователя напряжение-частота, третий вход которого подключен к выходу четвертого регистра сдвига, первый и второй выходы преобразователя напряжениечастота подключены к управляницим входам реверсивного счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 466453, кл. G 06 F 15/336, 1972. 2.Авторское свидетельство СССР № 636617, кл. G 06 F 15/336, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| Корреляционное устройство для определения задержки | 1982 |

|

SU1051545A1 |

| Корреляционное устройство для определения задержки | 1976 |

|

SU636617A1 |

| Устройство коррекции шкалы времени | 1990 |

|

SU1774307A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Измеритель элементов матрицы спектральной плотности мощности двух сигналов | 1989 |

|

SU1661667A2 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-08—Подача