1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля оперативной памяти, содержащее накопитель, дешифратор адреса, формирова тели записи, усилители считывания, схему свертки по модулю три, соединенную с выходом регистра адреса, две схемы сравнения, схему свертки по модулю два, соединенную с выходом регистра числа, контрольный разряд признака четности числа, три контрольных разряда признака кода адреса, две схемы формирования обратного кода признака адреса, дешифратор признака кода адреса и элемент ИЛИ 1.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому, изобретению является устройство для контроля оперативной памяти, содержащее регистр числа, блок свертки по модулю два.

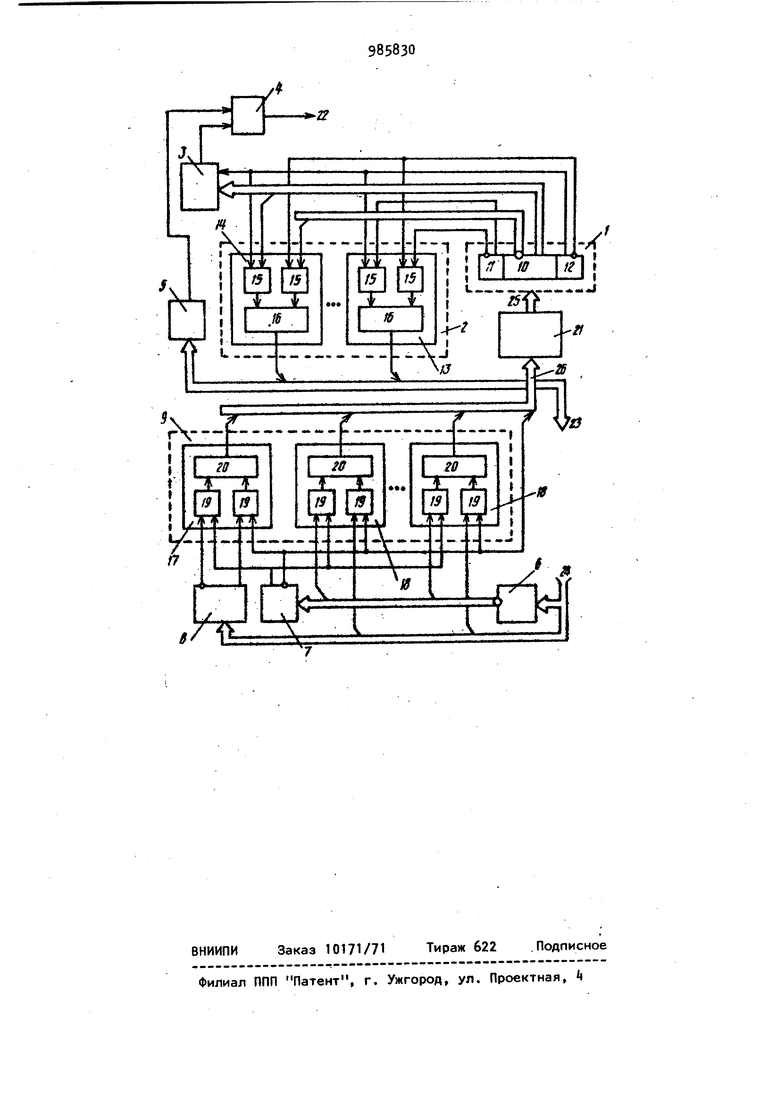

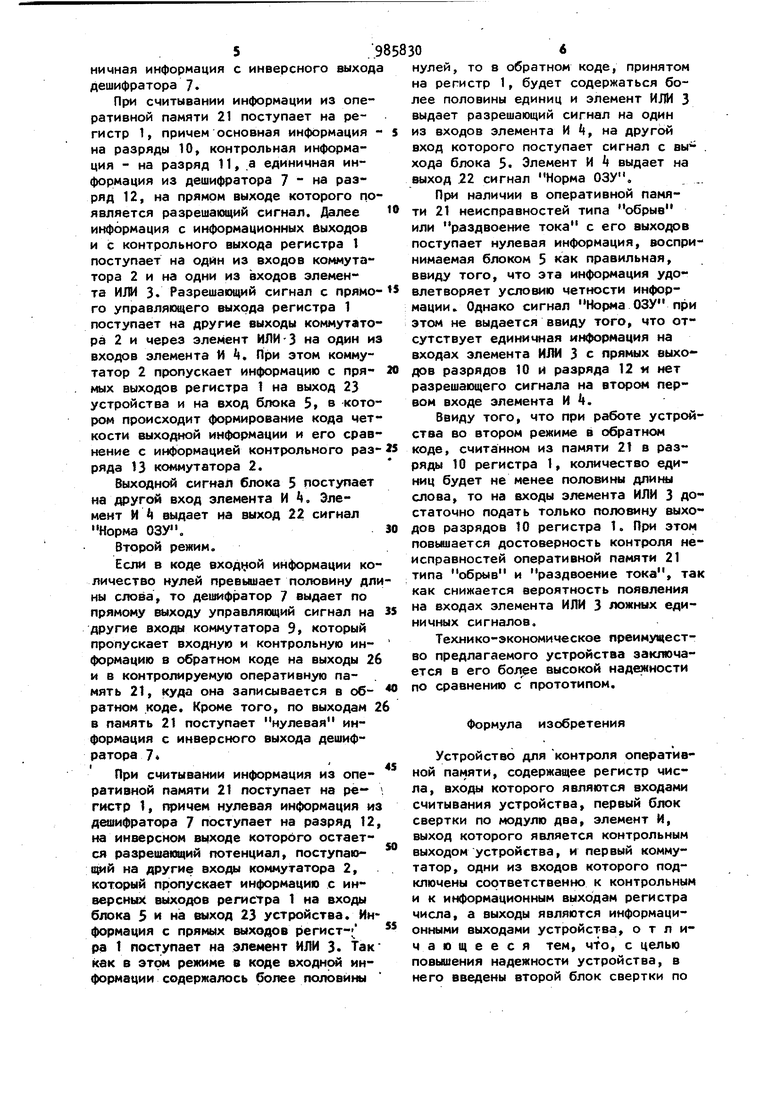

Ълок управления, схему сравнения, блок местного управления, триггер, элемент И и коммутатор, причем информационные выходы регистра числа подключены к входам блока свертки по модулю два, выход которого соединен с первыми входами схемы сравнения и блока местного управления, второй и третий входы которого подключены соответственно к первому и второму вы10ходам блока управления, а шлход соединен с контрольным входом регистра числа, прямой контрольный выход которого подключен к второму входу схемы сравнения причем третий и чет15вертый выходы блока управления соединены соответственно с вторым вхо-дом элемента И и нулевым входом триггера, единичный выход которого со20единен с третьим входом .элемента И, выход которого подключен к контрольному выходу устройства, выходы триггера соединены с одним из входов первого коммутатора, другие входы которого подключены к контрольному и информационным выходам регистра числа, а выходы первого коммутатопа соединены с выходами устройства и с магистралью записи в накопителе 2. Недостатком известного устройства является то, что оно не обеспечивает обнаружение ошибок несрабатывания адресного тракта типа обрыв или разг двоение тока, что снижает его надежность. Цель изобретения - повышение надеж ности устройства. Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее регистр числа, входы Которого явл1Я,ются входами считывания устройства, первый блок свертки по модулю два, элемент И, выход которого .является контрольным выходом устройства и первый коммутатор, одни из входов которого подключены соответственно к контрольным и к информационным выходам регистра чис ла, а выходы являются информационными выходами устройства, введены второй блок свертки по модулю два, второй коммутатор, дешифратор, элементы НЕ и элемент ИЛИ, один из входов которого соединен с прямым управляющим выходом регистра числа, а другие входы - с прямыми информационными выходами регистра числа, прямой и инверсный управляющие выходы которого подключены к другим входам первого коммутатора, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого подключен к ВЫХОДУ первого блока свертки по моду лю два, входы которого соединены с выходами первого коммутатора, выходы и входы второго блока свертки по модулю два подключены соответственно к одним из контрольных входов второго коммутатора и к входам элементов НЕ, одни из информационных входов второго коммутатора соединены соответственно с входами элементов НЕ и с выходами элементов НЕ и входами дешифратора, выходы которого подключены к другим информационным и контрольным входам второго коммутатора, выходы которого являются выходами записи устройства. информационными входами которого явля ются входы элементов НЕ. На чертеже изображена функциональная схема предлагаемого устройства. 9 04 Устройство содержит регистр 1 числа, первый коммутатор 2, элемент ИЛИ 3, элемент И , первый блок 5 свертки по модулю два, элементы НЕ 6, дешифратор 7, второй блок 8 свертки по модулю два, второй коммутатор 9, информационные 10, контрольный П и управляющий 12 разряды регистра числа, контрольный 13 и информационные 14 разряды первого коммутатора. Первый коммутатор содержит первую группу элементов И 15 и первую группу элементов ИЛИ 16. На чертеже обозначены также контрольный )7 и информационные 18 разряды второго коммутатора, который содержит вторую группу элементов И 19 и вторую группу элементов ИЛИ 20, контролируемая оперативная память 21, контрольный 22 и информационные 23 выходы устройства, информационные 2 и контрольные 25 входы устройства и выходы 26 записи устройства. Устройство работает следующим о§разом. 8 исходном состоянии регистр 1 находится в нулевом состоянии. Входная информация со входов 2k поступает на входы блока 8 и на входа элементов НЕ 6, с выходов которых она поступает на входы дешифратора 7 Дешифратор 7 реализует функцию Р А6С Л BCDAABD А АСО, где A,B,C,D- входные сигналы; Р - выходной сигнал. Кроме того, входа ая информация с входов 2k и с Ш|1ходоа элементов НЕ 6 поступает в прямом и в ратном коде на одни из информационных 16 коммутатора 9. Блок 8 ф чзмирует контрольный код четности, который в прямом ив обратном коде поступает на один из контрольных разрядов 17 коммутатора 9, Rsstee работу устройства удобно рассматривать в двух режимах. Первый рехсим. Ecrw в коде входной информации количество нулей не превышает полови- ны длины слова, то дешифратор 7 выдает по инверсному выходу управляющий сигнал на другие входы коммутатора 9, который пропускает входную и контрольную информации в прямом коде через выходы 26 в оперативную память 21, где она записывается в прямоМ коде. Кроме того, по выходам 26 в оперативную память 21 поступает единичная информация с инверсного выход дешифратора 7« При считывании информации из оперативной памяти 21 поступает на регистр 1, причем основная информация на разряды 10, контрольная информация - на разряд 11, .а единичная информация из дешифратора 7 на разряд 12, на прямом выходе которого по является разрешающий сигнал. Далее информация с информационных выходов и с контрольного выхода регистра I поступает на один из входов коммутатора 2 и на одни из входов элемента HJW 3. Разрешающий сигнал с прямо го управляющего выхода регистра 1 поступает на другие выходы коммутато ра 2 и через элемент ИЛИ-З на один и входов элемента И , При этом коммутатор 2 пропускает информацию с прямых выходов регистра 1 на выход 23 устройства и на вход блока 5, в кото ром происходит формирование кода чет кости выходной информации и его срав нение с информацией контрольного раз ряда 13 коммутатора 2. Выходной сигнал блока 5 поступает на другой вход элемента И k, Элемент И выдает на выход 22 сигнал Норма Второй режим. Если в коде входной информации ко личество нулей превьшает половину дл ны слова, то дешифратор 7 выдает по прямому выходу управляющий сигнал на другие входа коммутатора 9, который пропускает входную и контрольную информацию в обратном коде на выходы 26 и в контролируемую оперативную память 21, куда она записывается в обратном коде. Кроме того, по выходам 2 в память 21 поступает нулевая информация с инверсного выхода дешифратора 7 При считывании информация из оперативной памяти 21 поступает на ре- гистр 1, причем нулевая информация из дешифратора 7 поступает на разряд 12 на инверсном выходе которого остается разрешакйций потенциал, поступаю1Ф1Й на другие входы коммутатора 2, который пропускает информацию с инверсных выходов регист-ра 1 на входы б/юка 5 и Hia выход 23 устройства. Информация с прямых выходов регистра 1 поступает на элемент ИЛИ 3. Так как в этом режиме в коде входной информации содержалось более половим нулей, то в обратном коде, принятом на регистр 1, будет содержаться более половины единиц и элемент ИЛИ 3 выдает разрешающий сигнал на один из входов элемента И , на другой вход которого поступает сигнал с вы- . хода блока 5. Элемент И k выдает на выход ,22 сигнал Норма ОЗУ. наличии в оперативной памяти 21 неисправностей типа обрыв или раздвоение тока с его выходов поступает нулевая информация, воспринимаемая блоком 5 как правильная, ввиду того, что эта информация удовлетворяет условию четности информации Однако сигнал Норма ОЗУ при этом не выдается ввиду того, что отсутствует единичная информация на входах элемента ИЛИ 3 с прямых выхо дов разрядов 10 и разряда 12 м нет разрешающего сигнала на втором первом входе элемента И 4. Ввиду того, что при работе устройства во втором режиме в обратном коде, считанном из памяти 21 в разряды 10 регистра 1, количество единиц будет не менее половины длины слова, то на входы элемента ИЛИ 3 достаточно подать только половину выходов разрядов 10 регистра 1. При этом повьшается достоверность контроля неисправностей оперативной памяти 21 типа обрыв и раздвоение тока, так как снижается вероятность появления на входах элемента ИЛИ 3 ложных единичных сигналов. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности по сравнению с прототипом. Формула изобретения Устройство для контроля оперативной памяти, содержащее регистр числа, входы которого являются входами считывания устройства, первый блок свертки по модулю два, элемент И, выход которого является контрольным выходом устройства, и первый коммутатор, одни из входов которого подключены соответственно к контрольным и к информационным выхбдам регистра числа, а выходы являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй блок свертки по

модулю два, второй коммутатор, дешифратор, элементы НЕ и элемент ИЛИ один из входов которого соединен с прямым управляющим выходом регистра числа, а другие входы - с прямыми ийформационными выходами регистра числа, прямой и инверсный управляющие выходы которого подключены к другим входам первого коммутатора, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого подключен к выходу первого блока свертки по модулю два, входы которого соединены с выходами первого коммутатора, выходы и входы второго . блока свертки по модулю два подключены соответственно к одним из контрольных входов второго коммутатора и к входам элементов НЕ,одни из ин-

формационных входов второго коммутатора соединены соответственно с входами элементов НЕ и с выходами элементов НЕ и входакш дешифратора, выходы которого под ключены к другим информационным и контрольным входам второго коммутатора, выходы которого являются выходами записи устройства, информационными вхещакм которого являются входы элементов НЕ.

Источники информации, принятые во внимание при экспертизе

1.Авторскоесвидетельство СССР № , wi.q11 С 29/00, 1973.

2.Авторскоесвидетельство СССР ff 758260, кл. Q11 С 29/00, 1978 (прототип),

х

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

T-i

г

/л rSi

г

Г7

у /

2В

-fe-l

i гв

/Jf

fy Ifffl

ff

Авторы

Даты

1982-12-30—Публикация

1981-07-20—Подача