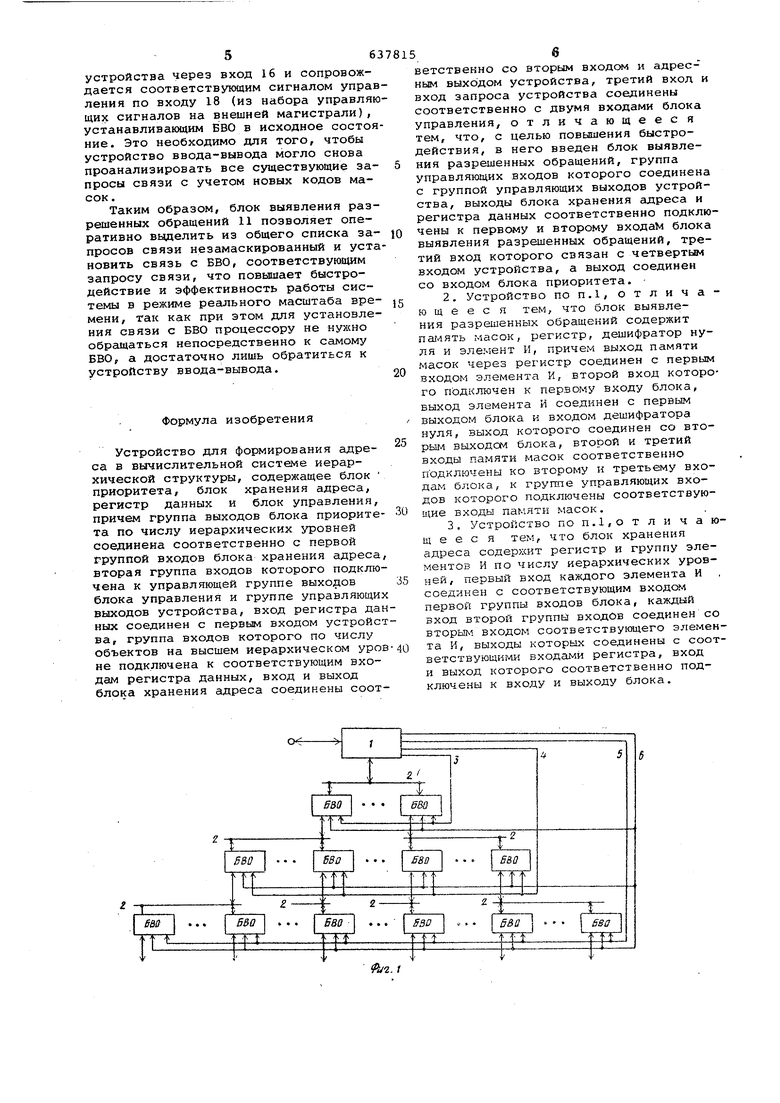

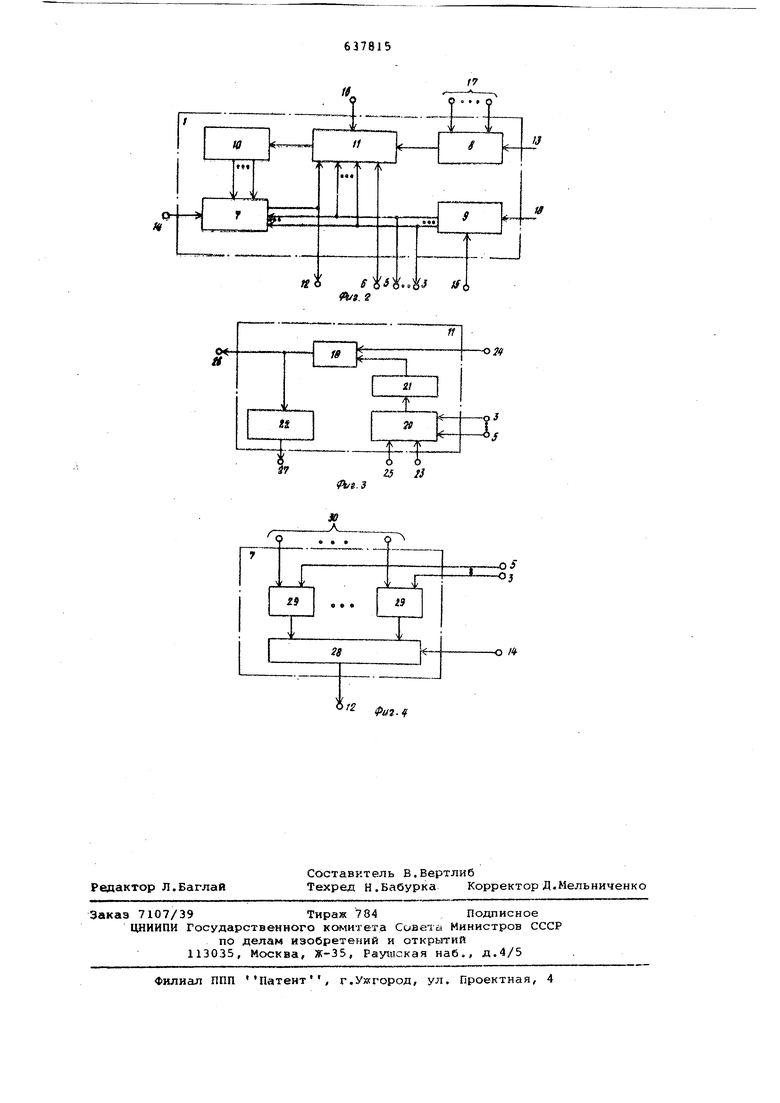

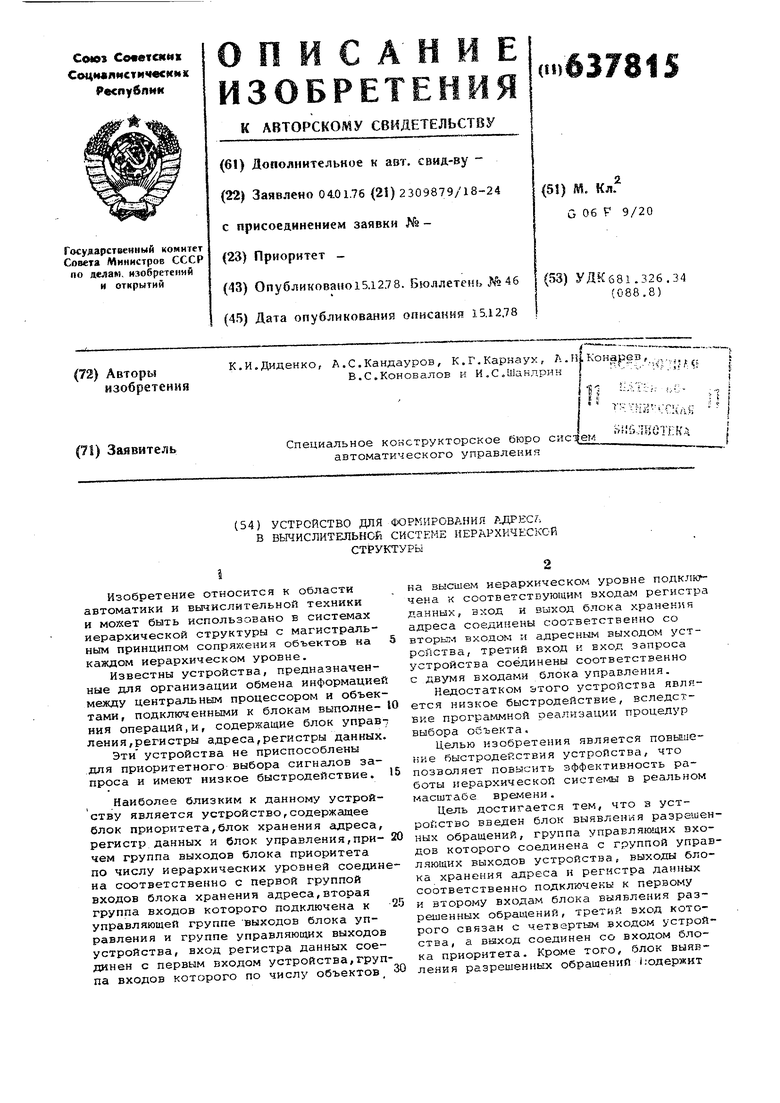

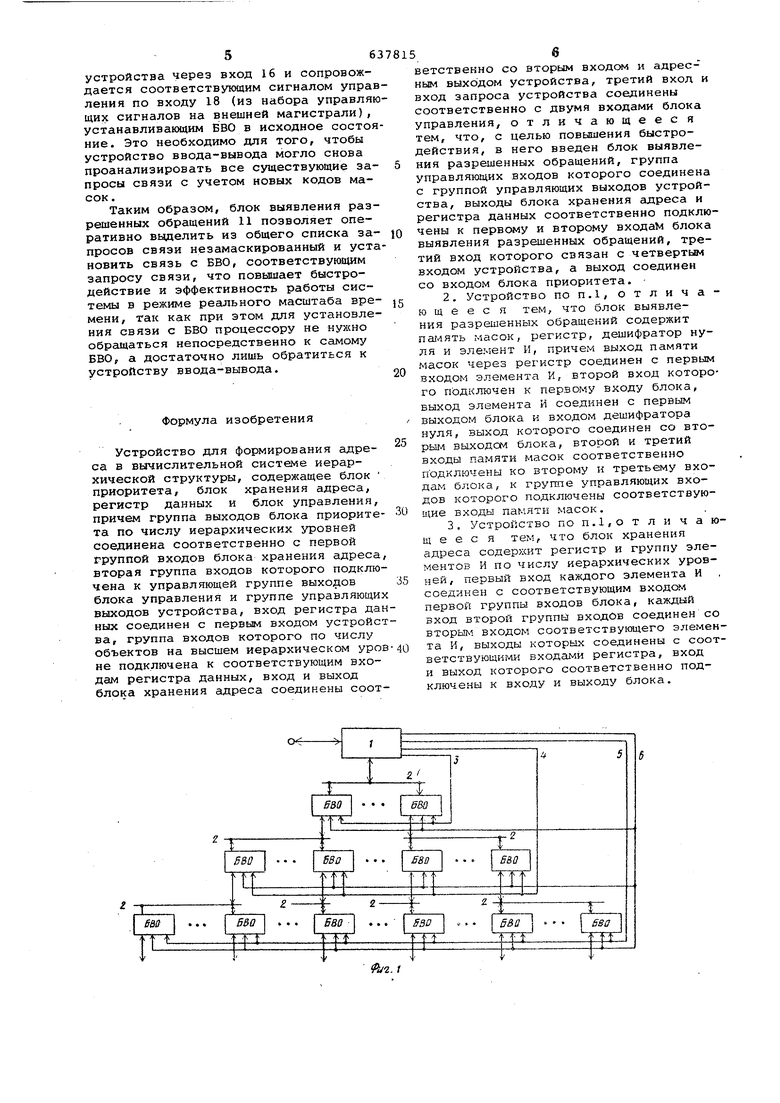

(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРКСь В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ ПЕРАРХИЧЕСКОЙ СТРУКТУРЫ память масок, регистр, дешифратор нул и элемент И, причем выход памяти масо через регистр соединен с входом элемента И, второй вход которого подключен к первому входу блока, выхо влемента И соединен с первым выходом блока и входом дешифратора нуля, выхо которого соединен со вторым выходом блока, второй и третий входы памяти масок соответственно подключены ко второму и третьему входам блока, к группе управляющих входов которого подктвочены соответствующие входы памяти масок. Кроме того, блок хране ния адреса содержит регистр и группу . элементов И по числу иерархических уровней, первый вход каяадого элемента И соединен с соответствующим входом первой группы входов блока,кажды вход второй группы входов соединен с вторым входом соответствующего элемента И, которых соединены соответствующими входами регистра, вход и выход которого соответственно подключены к входу и выходу блока На фиг.1 изображена система иерар хической структуры, в которой ИСПОЛЬ зуется рассматриваемое устройство; на фиг. 2-4 изобрал ены соответственно блок-схемы устройства, блок выявл ния разрешенных обращений и блок хра нения адреса. Описываемая система содержит блок выполнения операций (БВО), к которым подключены объекты - источники и приемники информации. БВО соединены в иерархическую стр туру и связаны между собой устройством для формирования адреса 1 посред ством магистральных шин 2, управляющих шин первого 3, второго 4, и третьего 5 уровней иерархии,а также иш блокировки 6. Устройство для формирования адрес 1 (фиг.2) содержит блок хранения адреса 7, регистр данных 8, блок упр ления 9, блок приоритета 10, блок вы ления разрешенных обращений 11, адре ный выход устройства 12, первый 13, второй 14, третий 15 и четвертый 16 входы устройства, группу входов 17 устройства по числу блоков выполнени операции, подключенных к магистрали на высшем иерархическом уровне, вход запроса 18. . Блок выявления разрешенных обраще ний 11 (фиг.З) содержит элемент И 19 память масок 20, регистр 21 и дешифр тор нуля 22,- первый вход 23, второй вход 24, третий вход 25, первый 26 и второй 27 выходы. Блок хранения адреса 7 ( фиг„4) содержит регистр 28 и группу элементов И 29 и первую группу входов 30. Устройство работает следующим образом. Когда какие-либо БВО низшего уров ня требуют связи, выдавая при этом запрос связи, то БВО высших уровней пропускают его на вход запроса 18 устройства 1 формирования адреса. Блок управления 9 вырабатывает сигнал на выходе 3 для управления группой БВО высшего уровня. По этому сигналу БВО данной группы выставляют на соответствующие разряды информационных шин магистрали 2 сигнал магистрального запроса связи ( в соответствии с позиционным приоритетом) соответствующих групп второго уровня. Эти сигналы считываются в регистре 8 данных в виде позиционных кодов, а в блоке 11 выявления разрешенных обращений из памяти 20 масок в регистр 21 считывается слово масок.Посредством элемента И 19 из позиционного кода, поступающего по входу 24, выделяются только те разряды, которые не соответствуют значениям соответствуюащх разрядов кода масок. Выделенный код поступает на дешифратор 22 нуля и на вход блока 10 приоритета. Если выделенный код оказался нулевым (все позиционные запросы связи замаскированы), то на выходе дешифратора 22 нуля формируется сигнал на выходе блокировки б. По этому сигналу в БВО производится блокировка запроса связи. Вследствие блокировки сигналов запроса связи высшего уровня, БВО снимает сигнал на запрос связи, а блок управления 9 переходит в режим ожидания следующего прерывающего сигнала, В случае, если сигнал запроса связи появится снова (например БВО, которые до этого не выставляли сигналов запросов связи, выставили их), то блок управления 9 повторяет цикл поиска приоритетного и не замаскированного сигнала запроса связи. Если выделенный код оказался не нулевым, то в блоке приоритета iO производится преобразование его в двоичный нормальный код адреса БВО первого уровня. Полученный код адреса, выдается на входа 30 блока хранения адреса 7 вместе с управляющим сигналом по шина1л 3-5, через соответствующий элемент И 29 записывается в соответствующую часть регистра адреса 28 и на .адресном выходе 12 выставляется адрес БВО, а на выходе блока управления 9 формируется сигнал управления группами БВО следующего уровня. Цикл поиска приоритетного и незамаскированного запроса связи повторяется в том порядке, как приведено вЕлше, за исключением того, что в блоке выявления разрешенных обращений 11 из памяти 20 масок считывается другой код масок. Адрес соответствующего кода масок определяется инфорузацией, находящейся в регистре адреса, и присутствием одного из управляющих сигналов по шинам 3-5. Занесение и изменение кода масок соответствующих групп, любого уровня, производится от внешнего управляющего устройства через вход 16 и сопровождается соответствующим сигналом управ ления по входу 18 (из набора управляю щих сигналов на внешней магистрали), устанавливающим БВО в исходное состоя ние. Это необходимо для того, чтобы устройство ввода-вывода могло снова проанализировать все существующие запросы связи с учетом новых кодов масок. Таким образом, блок выявления разрешенных обращений 11 позволяет оперативно выделить из общего списка запросов связи незамаскированный и уста новить связь с БВО, соответствуницим запросу связи, что повышает быстродействие и эффективность работы системы в режиме реального масштаба времени, так как при этом для установления связи с БВО процессору не нужно обращаться непосредственно к самому ВВО, а достаточно лишь обратиться к устройству ввода-вывода. Формула изобретения Устройство для формирования адреса в вычислительной системе иерархической структуры, содержащее блок приоритета, блок хранения адреса, регистр данных и блок управления, причем группа выходов блока приорите та по числу иерархических уровней соединена соответственно с первой группой входов блока хранения адреса вторая группа входов которого подклю чена к управляющей группе выходов блока управления и группе управляющи выходов устройства, вход регистра да ных соединен с первым входом устройс ва, группа входов которого по числу Объектов на высшем иерархическом уро не подключена к соответствующим входам регистра данных, вход и выход блока хранения адреса соединены соот етственно со BTOpfcfM входом и адресным выходом устройства, третий вход и вход запроса устройства соединены соответственно с двумя входами блока управления, отличающееся тем, что, с целью повышения быстродействия, в него введен блок выявления разрешенных обращений, группа управляющих входов которого соединена с группой управляющих выходов устройства, выходы блока хранения адреса и регистра данных соответственно подключены к первому и второму входам блока выявления разрешенных обращений, третий вход которого связан с четвертым входом устройства, а выход соединен со входом блока приоритета. 2. Устройство попЛ, отличающееся тем, что блок выявления разрешенных обращений содержит паглять масок, регистр, дешифратор нуля и элемент И, причем выход памяти масок через регистр соединен с первым входом элемента И, второй вход которого подключен к первому входу блока, выход элемента И соединен с первым выходом блока и входом дешифратора нуля, выход которого соединен со вторыгл выходом блока, второй и третий входы памяти масок соответственно подключены ко второму н третьему входам блокаf к группе управляющих входов которого подключены соответствующие входы памяти масок. 3 . Устройство по п.1,о т л и ч а ющ е е с я тем, что блок хранения адреса содержит регистр и группу элементов И по числу иерархических уровней, первый вход каждого элемента И , соед-лкен с соответствующим входом первой группы входов блока, каждый вход второй группы входов соединен со втopы . входом соответствующего элемента И, выходы которых соединены с соответствующими входами регистра, вход и выход которого соответственно подключены к входу и выходу блока.

IS,

ГУ

Г:

tzin

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

.з

/f

02(1

25 li

Авторы

Даты

1978-12-15—Публикация

1976-01-04—Подача