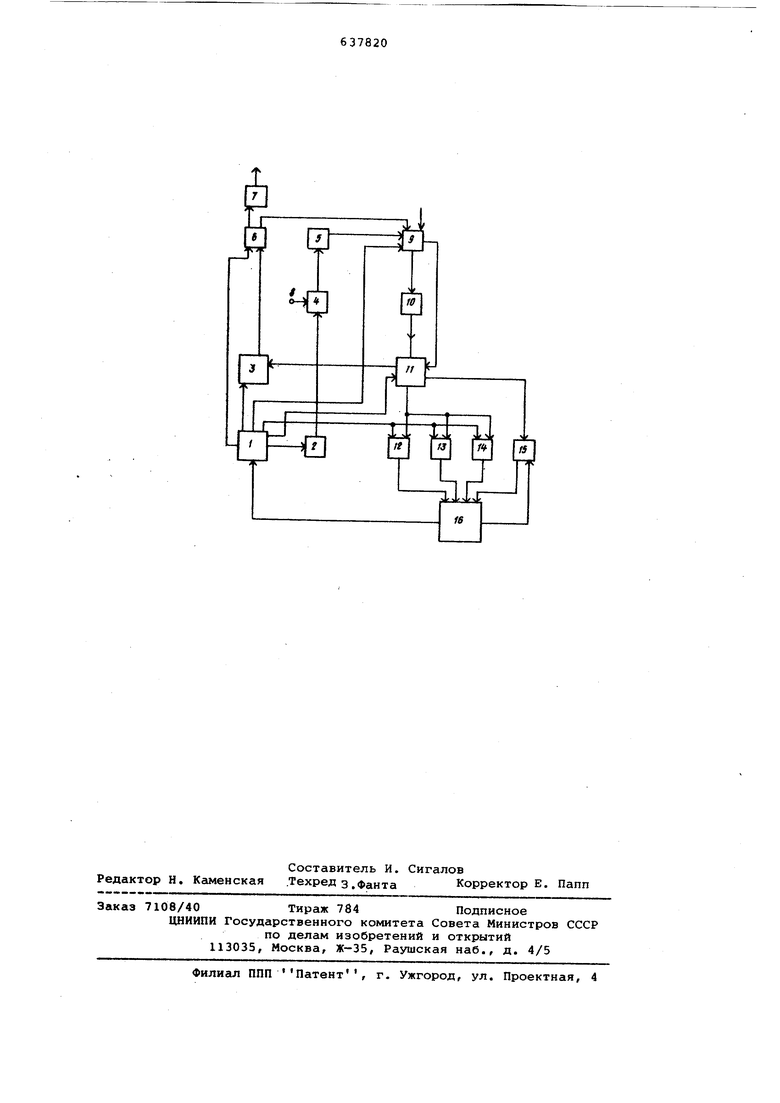

йены соответственно со входом блока памяти неисправностей, со вторым входом блока формирования сигнала ошибки выход блока памяти неисправностей соединен с третьим входом блока формирования сигнала ошибки 2, Недостатком этого устройства наляется низкое быстродействие, которое объясняется тем, что сравнение каждой кодовой комбинации стимулирующего воздействия производится по всем разрядам кодовой комбинации реакции объекта проверки. Кроме того, для поиска неисправностей необходимо многократно контролировать часть логического узла с неисправностью, что также можно реализовать путем маскирования неконтролируемойчасти логического узла (разрядов кодовых комбинаций). Целью изобретения является повышение быстродействия устройства. Это достигается тем,что в предлага емое устройство введены регистр масок блок хранения масок, блок формировани масок, причем шестой выход блока памяти соединен со входом регистра масок, выход которого соединен с первым входом блока хранения масок, второй вход блока хранения масок является вторым входом устройства, выход блока хранения масок соединен со вхо дом блока формирования масок, выход которого соединен с четвертЕ гм входом блока сравнения. Структурная схема устройства пред ставлена на чертеже. Устройство содержит блок памяти 1 регист масок 2, блок управления 3, блок хранения масок 4, блок формирования масок 5, генератор стимулирующих воздействий 6, коммутатор 7, вход устройства 8, блок сравнения 9, блок памяти неисправностей 10, блок форми рования сигнала ошибки 11, регистр п программ 12, регистр сбоев 13, регис цикла 14,регистр возврата 15, адресный коммутатор 16. Блок памяти 1 служит для хранения программ контроля и представляет собой запоминающее устройство с произвольным доступом к ячейкам памяти по адресу, задаваемому адресным коммута тором 16. Регистр масок 2 по команде блока оперативной памяти 1 осуществляет по иск массива кодовых комбинаций масок в соответствии с проверяемым объекто контроля. Блок управления 3 служит для расстановки разрядов генератора стимули рующих воздействий в соответствии с командой блока оперативной памяти и определяет взаимодействие разрядов г нератора стимулирующих воздействий. Блок хранения масок 4 служит для хранения записываемых по второму вхо ду массивов кодовых комбинаций масок сей номеклатуры проверяемых объектов онтроля. Блок формирования масок 5 формиует кодовые комбинации масок как для поразрядного маскирования, так и для аскирования всей кодовой комбинации. Блок генерации стимулирующих воздействий б формирует кодовые комбинации необходимой длины, выдает серию комбинаций по закону, установленному блоком управления, служит для установления амплитудно-временных характеристик генератора стимулирующих воздействий. Коммутатор 7 посылает последоваельность кодовых комбинаций на объект проверки. Блок сравнения Э предназначен для установления факта неисправности объекта проверки и определения соответствия программе реакций объекта проверки. Блок памяти неисправностей 10 служит для накапливания результатов отдельных этапов контроля. Блок формирования сигнала ошибки 11 определяет характер неисправности и переводит устройство на его локализацию. Регистры подпрограмм 12, сбоев 13, цикла 14 и возврата 15 служат для хранения и выдачи адресов блока памяти 1, по которым необходимо обратиться в соответствии с решением, принятым блоком формирования сигнала ошибки 11. Устройство работает следующим образом. Блок генерации стимулирующих воздействий по команде с блока памяти 1 вырабатывает серию кодовых комбинаций, которые посылает через коммутатор 7 на объект проверки. Кодовые комбинации реакции объекта проверки накапливаются в блоке сравнения 9. Если в процессе контроля с блока формирования масок 5 в блок сравнения 9 подаётся кодовая комбинация маски, то текущая кодовая комбинация реакции объекта проверки не анализируется и по команде блока памяти 1 с блока 6 на объект проверки выдается следующая кодовая комбинация стимулирующего воздействия. В этом случае происходит сравнение кодовой комбинации, реакции объекта -проверки с эталонной, поступающей с блока генерации стимулирующего воздействия и т.д. Для установления области устойчивой работы объекта проверки блок формирования сигнала ошибки 11 выдает команду блоку управления 3 на многократный перебор кодовых комбинаций ге нератора стимулирующих воздействий 6, а также по адресу, записанному в регистре циклов 14, осуществляет обращение к подпрограмме проверки области устойчивости работы объекта провар ки. При несоответствии накопленной и эталонной информации блок формирования сигнала ошибки 11 вырабатывает команду обращения к подпрограмме локализации неисправности через регистр сбоя 13. Адрес подпрограммы записывается блоком памяти 1 в регистр под программ 12. Блок памяти 1 в этом случае через генератор стимулирующих воздействий 6 и коммутатор 7 выдает нй объект проверки кодовые комбинации. Все случаи несоответствия реакций объекта проверки с эталоном фиксируются блоком памяти неисправностей 10 По окончании подпрограммы блок выработки сигнала ошибки 11 определяет вид неисправности и переходит к следуккдему участку программы по адресу, записанному ранее в регистре возврата 15 с адресного коммутатора 16 в момент перехода к подпрограмме локализации неисправности. По окончании всей программы контроля и отсутствии неисправностей объект проверки считается исправным. За счет введения регистра масок, бло ка хранения масок, блока формировани масок возрастает быстродействие устройства. Так как уменьшается количес во .анализируемых кодовых комбинаций. Формула изобретения Устройство для контроля логически блоков, содержащее блок памяти, блок управления, генератор стимулирующих воздействий, коммутатор, блок сравне ния, блок памяти неисправностей, бло формирования сигнала ошибки, регистр подпрограмм, регистр сбоев, регистр цикла, регистр возврата, адресный ко мутатор, причем первый, второй, трет четвертый и пятый выходы блока памяти соединены соответственно с первым входом генератора стимулирующих воздействий, с первым входом блока упра ления , с первым входом блока сравнения, с первыми входами регистра подпрограмм, регистра сбоев и регистра цикла, с первым входом блока формирования сигнала ошибки, первый, второй и третий выходы которого соединены соответственно со вторым входом блока управления, с первым входом регистра возврата, со вторыми входами регистра подпрограмм, регистра сбоев и регистра цикла, выходы регистра подпрограмм, регистра сбоев, регистра цикла, регистра возврата соединены соответственно с первым, вторым, третьим и четвертым входом адресного коммутатора, первый и второй выходы которого соединены соответственно со входом блока памяти и со вторым вз:одом блока возврата, выход блока управления соединен со вторым входом генератора стимулирующих воздействий, первый и второй выходы которого соединены соответственно со входом коммутатора и со вторым входом блока сравнения, выход коммутатора является выходом устройства, вход устройства соединен с третьим входом блока сравнения , первый и второй.выходы которого соединены со входом блока памяти неисправностей, со вторым входом блока формирования сигнала ошибки, выход блока памяти неисправностей соединен с третьим входом блока формирования сигнала ошибки, отличающеес я тем, что, с целью повышения быстродействия, в устройство введены регистр масок, блок хранения масок, блок формирования масок, причем шестой выход блока памяти соединен со входом регистра масок, выход которого соединен с первым входом блока хранения масок, второй вход блока хранения масок является вторым входом устройства, выход блока хранения масок соединен со входом блока формирования масок, выход которого соединен с четвертым входом блока сравнения. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 390526, кл, G|06 F 11/04, 1971. 2.Авторское свидетельство СССР № 469971, кл. G06 F 11/00, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логическихузлОВ | 1978 |

|

SU813431A2 |

| Устройство для контроля логических узлов | 1973 |

|

SU469971A1 |

| Устройство для контроля логических узлов | 1978 |

|

SU666544A2 |

| Устройство для контроля логических узлов | 1976 |

|

SU612247A2 |

| Система для контроля параметров | 1985 |

|

SU1255996A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для программного контроля | 1978 |

|

SU805316A1 |

Авторы

Даты

1978-12-15—Публикация

1976-08-01—Подача