1

Изобретение относится к вычислительной технике и может быть использовано для контроля логических узлов.

По основному авт. св. № 469971 известно устройство для контроля логических узлов, содержащее адресный коммутатор, первый выход которого подключен к первому входу блока анализа неисправностей и логической обработки, блок оперативной памяти, первый и второй выходы которого подключены к блоку управления, третий выход- к первому входу блока генерации стимулирующих воздействий, а четвертый - к блоку анализа неисправностей и логической обработки, выходы блока управления соединены со вторым и третьим входами блока стимулирующих воздействий, три выхода которого подключены к блоку коммутации стимулирующих воздействий, а один выход-к блоку выявления неисправностей, выходы которого соединены со вторым входом блока анализа неисправностей и логической обработки и первым входом блока оперативной памяти, кроме того, устройство дополнительно содержит блок памяти неисправностей, соединенный входом с блоком выявления неисправностей, а выходом - с третьим входом блока анализа неисправностей jd логической обработки, один выход которого подключен к блоку управления и четыре выхода - к адресному коммутатору, второй выход которого соединен с блоком оперативной памяти {.

Недостатком этого устройства является низкое быстродействие, так как оно ограничивается временем формирования кодовой комбинации стимулирующего воздействия при проверке любого логического блока.

Цель изобретения - повышения быстродействия.

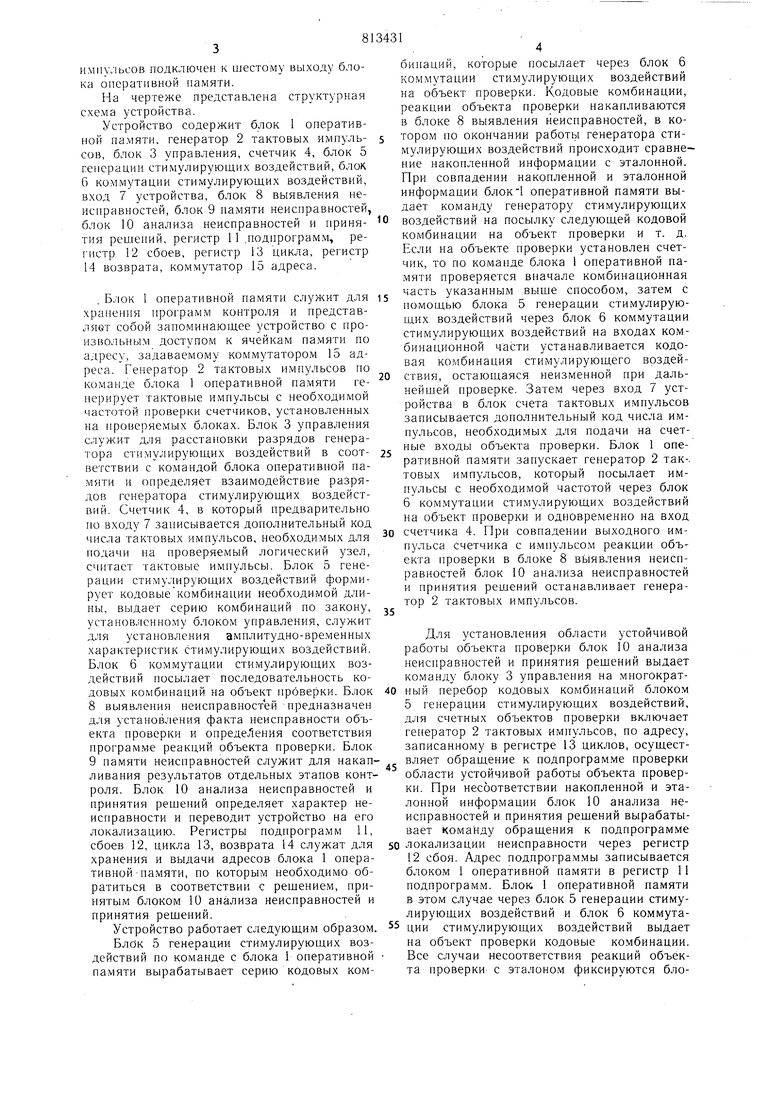

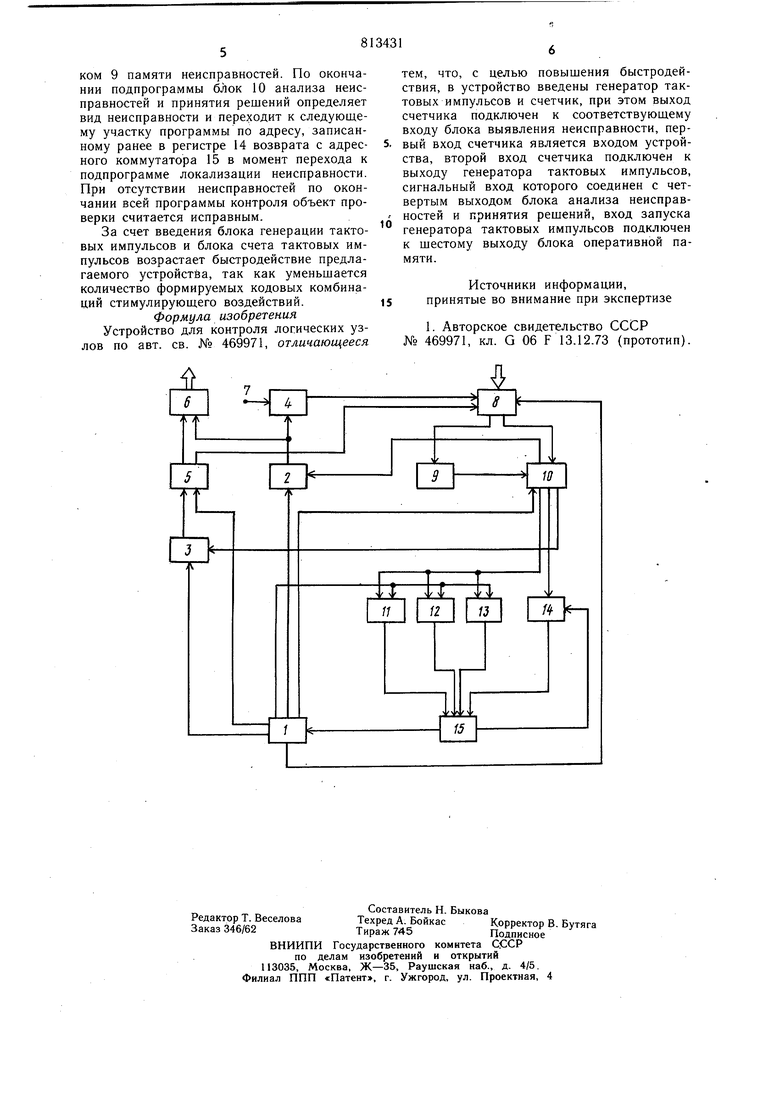

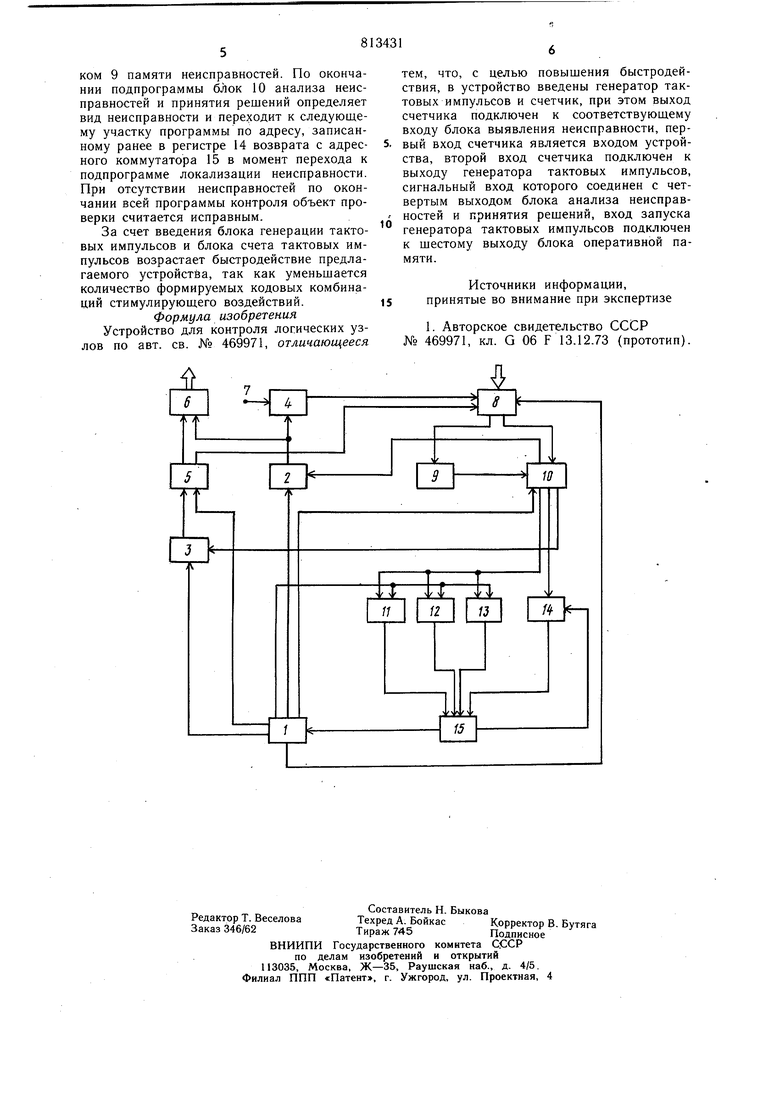

Поставленная цель достигается тем, что в устройство для контроля логических узлов введены генератор тактовых импульсов и счетчик, при этом выход счетчика подключен к соответствующему входу блика выявления неисправности, первый вход счетчика является входом устройства, второй вход

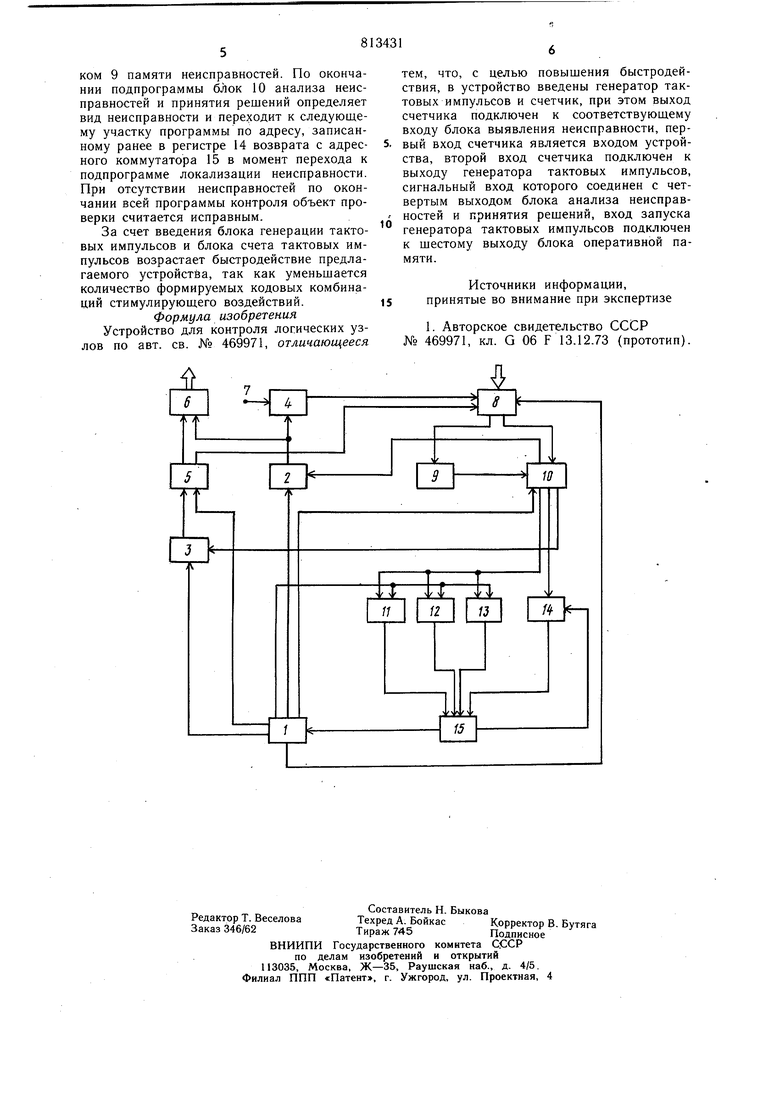

счетчика подключен к выходу генератора тактовых импульсов, сигнальный вход которого соединен с четвертым выходом блока анализа неисправностей и принятия рещений вход запуска генератора тактовых импульсов подключен к шестому выходу блока оперативной памяти. На чертеже представлена структурная схема устройства. Устройство содержит блок 1 оперативной памяти, генератор 2 тактовых импульсов, блок 3 управления, счетчик 4, блок 5 генерации стимулирующих воздействий, блок 6 коммутации стимулирующих воздействий, вход 7 устройства, блок 8 выявления неисправностей, блок 9 памяти неисправностей, блок 10 анализа неисправностей и принятия решепий, регистр 11 .подпрограмм, регистр 12 сбоев, регистр 13 цикла, регистр 14 возврата, коммутатор 15 адреса. . Блок 1 оперативной памяти служит для храпения программ контроля и представляет собой запоминающее устройство с произвольным доступом к ячейкам памяти по адресу, задаваемому коммутатором 15 адреса. Генератор 2 тактовых импульсов по команде блока 1 оперативной памяти генерирует тактовые импульсы с необходимой частотой проверки счетчиков, установленных на проверяемых блоках. Блок 3 управления служит для расстановки разрядов генератора стимулирующих воздействий в соответствии с командой блока оперативной памяти и определяет взаимодействие разрядов генератора стимулирующих воздействий. Счетчик 4, в который предварительно по входу 7 записывается дополнительный код числа тактовых импульсов, необходимых для подачи на проверяемый логический узел, считает тактовые импульсы. Блок 5 генерации стимулирующих воздействий формирует кодовые комбинации необходимой длины, выдает серию комбинаций по закону, установленному блоком управления, служит для установления амплитудно-временных характеристик стимулирующих воздействий. Блок 6 коммутации стимулирующих воздействий посылает последовательность кодовых комбинаций на объект прбверки. Блок б выявления неисправностей предназначен для установления факта неисправности объекта проверки и определения соответствия программе реакций объекта проверки. Блок 9 памяти неисправностей служит для накапливания результатов отдельных этапов контроля. Блок 10 анализа неисправностей и принятия рещений определяет характер неисправности и переводит устройство на его локализацию. Регистры подпрограмм 11, сбоев 12, цикла 13, возврата 14 служат для хранения и выдачи адресов блока 1 оперативной памяти, по которым необходимо обратиться в соответствии с рещением, принятым блоком 10 анализа неисправностей и принятия решений. Устройство работает следующим образом. Блок 5 генерации стимулирующих воздействий по команде с блока 1 оперативной памяти вырабатывает серию кодовых комбииаций, которые посылает через блок 6 коммутации сти.мулирующих воздействий на объект проверки. Кодовые комбинации, реакции объекта проверки накапливаются в блоке 8 выявления неисправностей, в котором по окончании работь генератора стимулирующих воздействий происходит сравнение пакопленной информации с эталонной. При совпадении накопленной и эталонной информации оперативной памяти выдает команду генератору стимулирующих воздействий на посылку следующей кодовой комбинации на объект проверки и т. д. Если на объекте проверки установлен счетчик, то по команде блока 1 оперативной памяти проверяется вначале комбинационная часть указанным выще способом, затем с помощью блока 5 генерации стимулирующих воздействий через блок 6 коммутации стимулирующих воздействий на входах комбинационной части устанавливается кодовая комбинация стимулирующего воздействия, остающаяся неизменной при дальнейшей проверке. Затем через вход 7 устройства в блок счета тактовых импульсов записывается дополнительный код числа импульсов, необходимых для подачи на счетные входы объекта проверки. Блок 1 оперативной памяти запускает генератор 2 так-, товых импульсов, который посылает импульсы с необходимой частотой через блок 6 коммутации стимулирующих воздействий на объект проверки и одновременно на вход счетчика 4. При совпадении выходного импульса счетчика с и.мпульсо.м реакции объекта проверки в блоке 8 выявления неисправностей блок 10 анализа неисправностей и принятия решений останавливает генератор 2 тактовых импульсов. Для установления области устойчивой работы объекта проверки блок 10 анализа неисправностей и принятия рещений выдает команду блоку 3 управления на многократный перебор кодовых комбинаций блоком 5 генерации стимулирующих воздействий, для счетных объектов проверки включает генератор 2 тактовых импульсов, по адресу, записанному в регистре 13 циклов, осуществляет обращение к подпрограмме проверки области устойчивой работы объекта проверки. При несоответствии накопленной и эталонной информации блок 10 анализа неисправностей и принятия рещений вырабатывает команду обращения к подпрограмме локализации неисправности через регистр 12 сбоя. Адрес подпрограммы записывается блоком 1 оперативной памяти в регистр 11 подпрограмм. Блок. 1 оперативной памяти в этом случае через блок 5 генерации стимулирующих воздействий и блок 6 коммутации стимулирующих воздействий выдает на объект проверки кодовые комбинации. Все случаи несоответствия реакций объекта проверки с эталоном фиксируются блоком 9 памяти неисправностей. По окончании подпрограммы блок 10 анализа неисправностей и принятия решений определяет вид неисправности и переходит к следующему участку программы по адресу, записанному ранее в регистре 14 возврата с адресного коммутатора 15 в момент перехода к подпрограмме локализации неисправности. При отсутствии неисправностей по окончании всей программы контроля объект проверки считается исправным.

За счет введения блока генерации тактовых импульсов и блока счета тактовых импульсов возрастает быстродействие предлагаемого устройства, так как уменьшается количество формируемых кодовых комбинаций стимулирующего воздействий. Формула изобретения

Устройство для контроля логических узлов по авт. св. № 469971, отличающееся

тем, что, с целью повышения быстродействия, в устройство введены генератор тактовых импульсов и счетчик, при этом выход счетчика подключен к соответствующему входу блока выявления неисправности, первый вход счетчика является входом устройства, второй вход счетчика подключен к выходу генератора тактовых импульсов, сигнальный вход которого соединен с четвертым выходом блока анализа неисправностей и принятия решений, вход запуска генератора тактовых импульсов подключен к шестому выходу блока оперативной памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 469971, кл. G 06 F 13.12.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1978 |

|

SU666544A2 |

| Устройство для контроля логических блоков | 1976 |

|

SU637820A1 |

| Устройство для контроля логических узлов | 1973 |

|

SU469971A1 |

| Устройство для контроля логических узлов | 1976 |

|

SU612247A2 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841060A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для диагностирования логических узлов | 1979 |

|

SU892447A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

Авторы

Даты

1981-03-15—Публикация

1978-07-31—Подача