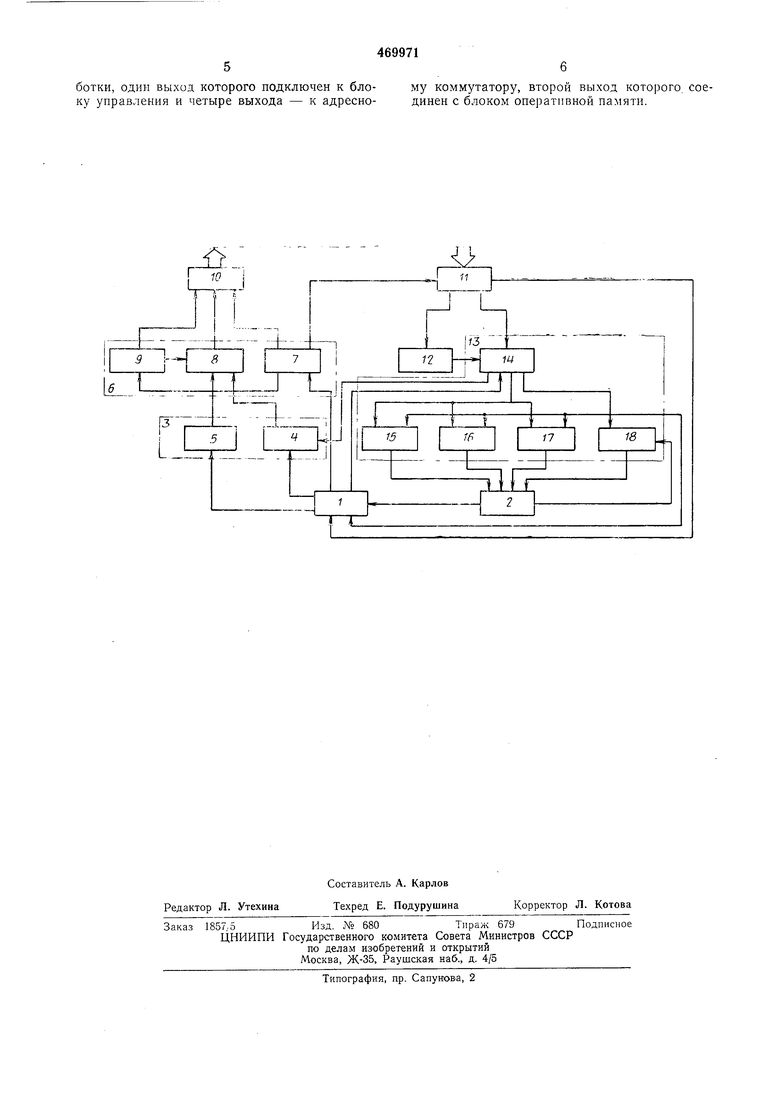

тора чисел 8 с различным порядком следования.

Блок задания времени 5 и блок преобразования код - аналог 9 служат для установления амплитудно-временных характеристик генератора чисел 8. Блок формирования кодовых комбинаций 7 предназначен для расстановки разрядов в кодовых комбинациях необходимой длины и последовательности при ограниченном числе разрядов в слове блока оперативной памяти 1. Блок формироваиия кодовых комбинаций 7 может быть выполнен в виде 1егистра памяти с управляемыми входами и выходами.

Блок коммутации стимулирующих воздействий 10 посылает последовательность кодовых комбинаций на объект проверки (на чертеже не показан).

Блок выявления неисправностей 11 предназначен для установления факта неиснравности объекта проверки и определения соответствия программе реакций объекта проверки.

Блок памяти неисправностей 12 служит для накапливания результатов отдельных этапов контроля.

Блок анализа неисправностей и принятия решений 14 определяет характер неисправности и переводит устройство на его локализацию.

Регистры подпрограмм, 15, сбоев 16, цикла 17 и возврата 18 служат для хранения и выдачи адресов блока оперативной памяти 1, по которым необходимо обратиться в соответствии с решением, принятым блоком анализа неисправностей, и принятия решений 14.

Устройство работает следующим образом.

Генератор чисел 8 по команде с блока оперативной памяти 1 через блоки 4, 5 и 9 вырабатывает серию кодовых комбинаций, которые посылает через блок коммутации стпмулирующих воздействий 10 на объект проверки, при этом обеспечивается проверка на рабочей частоте объекта проверки независимо от быстродействия блока оперативной памяти 1. Кодовые комбинации реакции объекта проверки накапливаются в блоке выявления неисправностей 11, в котором происходит сравнение по окончании работы генератора чисел накопленной информации с эталонной, поступающей с блока формирования кодовых комбинаций 7. При совпадении накопленной и эталонной информации блок оперативной памяти 1 задает следующий порядок следования воздействий генератору чисел 8 и т. д.

Установление области устойчивой работы производится путем изменения амплитудновременных характеристик стимулирующих воздействий блоками 5 и 9. В этом случае блок анализа неисправностей и принятия решений 14 выдает команду блоку задания порядка следования 4 на многократный перебор кодовых комбинаций генератором чисел 8, а также, по адресу, записанному в регистре цикла 17, осуществляет обращение к подпрограмме проверки области устойчивой работы объекта проверки. При несоответствии накопленной и эталонной информации блок анализа неисправностей и принятия решений 14 вырабатывает команду обращения к подпрограмме локализации неисправности через регистр сбоя 16. Адрес подпрограммы записывается блокам оперативной памяти 1 в регистр подпрограмм 15. Блок оперативной памяти 1 в этом случае через блоки формирования кодовых комбинаций 7 и коммутации стимулирующих воздействий 10 выдает на объект проверки кодовые комбинации. После выдачи каждого стимулирующего воздействия блок оперативной памяти 1 через блок формирования 7 выдает в блок выявления неисправностей И эталонный код реакции объекта проверки. Все случаи несоответствия реакций объекта проверки с эталоном фиксируются блоком памяти неисправностей 12. По окончании подпрограммы блок апализа неисправностей и принятия решений 14 определяет вид неисправности и переходит к следующ,ему участку программы по адресу, записанному ранее в регистре возврата 18 с адресного коммутатора 2 в момент перехода к подпрограмме локализации неисправности.

В случае необнаружения неиснравности по подпрограмме блок анализа неисправностей 14 принимает рещение о случайном отказе

объекта проверки ири работе на рабочей частоте, и но адресу, записанному в регистре сбоев 16, устройство переходит к очередному участку программы.

По окончании всей программы контроля и

отсутствии неисправностей объект проверки считается исправным.

Предмет изобретения

Устройство для контроля логических узлов, содержащее адресный коммутатор, первый выход которого подключен к первому входу блока анализа неисправностей и логической

обработки, блок оперативной памяти, первый и второй выходы которого подключены к блоку управления, третий выход - к- первому входу блока генерации стимулирующих воздействий, а четвертый - к блоку анализа псиснравностей и логической обработки, выходы блока управления соединены со вторым г, третьим входами блока стимулирующих воздействий, три выхода которого подк.чючены к блоку коммутации стимулирующих воздейстВИЙ, а один выход - к блоку выявления леисправностей, выходы которого соединены со вторым входом блока анализа неисправностей и логической обработки и первым входом блока оиеративной памяти, отличающеес я тем, что, с целью повышения точности и полноты контроля, устройство дополнительно содержит блок памяти неисправностей, соединенный входом с блоком выявления неисправностей, а выходом - с третьим входом блока

анализа неисправностей и логической обработки, один выход которого подключен к блоку управления и четыре выхода - к адресному коммутатору, второй выход которого, соединен с блоком оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логическихузлОВ | 1978 |

|

SU813431A2 |

| Устройство для контроля логических узлов | 1978 |

|

SU666544A2 |

| Устройство для контроля логических узлов | 1976 |

|

SU612247A2 |

| Устройство для контроля логических блоков | 1976 |

|

SU637820A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841060A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля логичесикх узлов | 1976 |

|

SU613324A1 |

/

О

Авторы

Даты

1975-05-05—Публикация

1973-12-13—Подача