1

Изобретение относится к области вычислительной техники.

В основном авт. св. 469971 описано устройство для контроля логических узлов, содержащее адресный коммутатор, первый выход которого подключен к первся у входу блока анализа неисправностей и логической обработки, блок оперативной памяти, первый и второй выходы которого подключены к блоку управления, третий выход - к первому входу блока гензрации стимулирующих воздействий, а четвертый - к блоку анализа неисправностей и логической обработки, выходы блока управления соединены со вторым и третьим входами блока стимулирующих воздействий, три выхода которого подключены к блоку коммутаций стимулирукядих воздействий, а один выход - к блоку выявления неисправн ост ей, выходы которого соединены со вторым входом блока анализа неисправностей и логической обработки и первым входом блока оперативной памяти, и блок памяти неисправностей, соединенный входом с блоком выявления неисправностей, а выходом с третьим входом блока неисправностей и логической обработки, один выход которого подключен к блоку управления и четыре выхода - к адресному коммутатору, второй выход кото рого соединен с блоком оперативной памяти.

Однако функциональные возможности такого устройства ограничены и вследствие этого, коэффициент использования оборудования низок.

0

Целью изобретения является повышение коэффициента использования оборудов ания.

Поставленная цель достигается тем, в предложенное устройство вве5дена группа элементов И, входы которых являются соответствующими входами устройства, а первый и второй управляющие входы - соединены соответственно с третьим.выходом блока

0 управления и управляющим выходом блока коммутации стиммулирующих воздействий, четвертым входом соединенного с четвертым выходом блока управления, выходы элементов И груп5пы подключены к соответствующим входам блока выявления неисправностей.

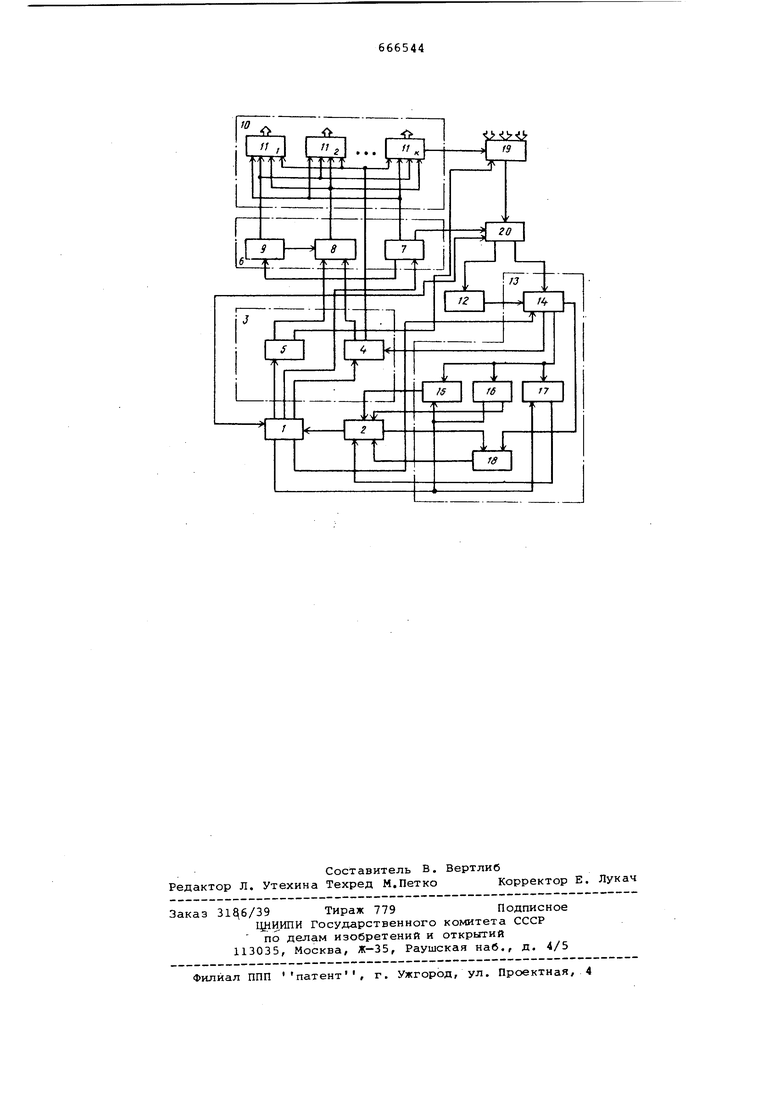

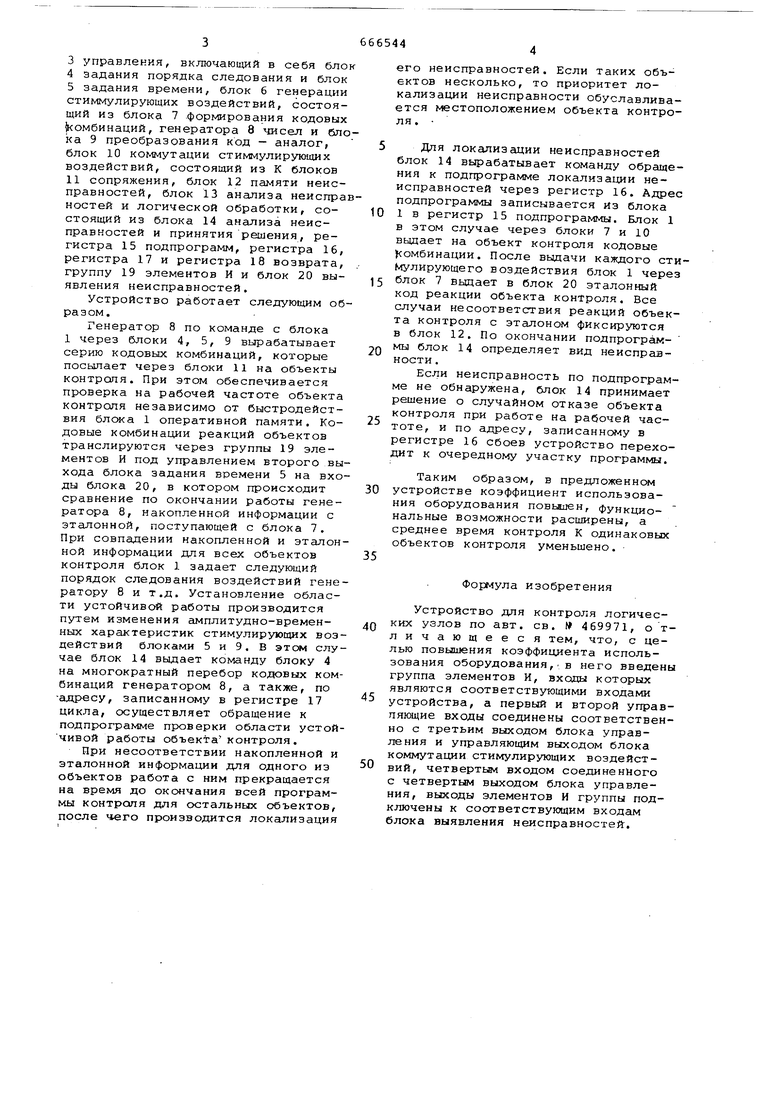

На чертеже представлена блок-схема устройства.

I Оно содержит блок 1 оперативной памяти, адресный коммутатор 2, блок

3управления, включающий в себя бло

4задания порядка следования и блок

5задания времени, блок 6 генерации стиммулирующих воздействий, состоящий из блока 7 формирования кодовых {комбинаций, генератора 8 чисел и блока 9 преобразования код - аналог, блок 10 коммутации стиммулирующих воздействий, состоящий из К блоков

11 сопряжения, блок 12 памяти неисправностей, блок 13 анализа неиспраностей и логической обработки, состоящий из блока 14 анализа неисправностей и принятия решения, регистра 15 подпрограмм, регистра 16, регистра 17 и регистра 18 возврата, группу 19 элементов И и блок 20 выявления неисправностей.

Устройство работает следующим образом.

Генератор 8 по команде с блока 1 через блоки 4, 5, 9 вырабатывает серию кодовых комбинаций, которые посылает через блоки 11 на объекты контроля. При этом обеспечивается проверка на рабочей частоте объекта контроля независимо от быстродействия блока 1 оперативной памяти. Кодовые комбинации реакций объектов транслируются через группы 19 элементов И под управлением второго выхода блока задания времени 5 на входы блока 20, в котором происходит сравнение по окончании работы генератора 8, накопленной информации с эталонной, поступающей с блока 7. При совпадении накопленной и эталонной информации для всех объектов контроля блок 1 задает следующий порядок следования воздействий генератору 8 и т.д. Установление области устойчивой работы производится путем изменения амплитудно-временных характеристик стимулирующих воздействий блоками 5 и 9. В этсм случае блок 14 вьщает команду блоку 4 на многократный перебор кодовых комбинаций генератором 8, а также, по адресу, записанному в регистре 17 цикла, осуществляет обращение к подпрограмме проверки области устойчивой работы объекта контроля.

При несоответствии накопленной и эталонной информации для одного из объектов работа с ним прекращается на время до окончания всей программы контроля для остальных субъектов, после чего производится локализация

его неисправностей. Если таких объектов несколько, то приоритет локализации неисправности обуславливается местоположением объекта контроля.

5 Для локализации неисправностей блок 14 вырабатывает команду обращения к подпрограмме локализации неисправностей через регистр 16. Адрес подпрограммы записывается из блока

0 1 в регистр 15 подпрограммы. Блок 1 в этом случае через блоки 7 и 10 выдает на объект контроля кодовые Комбинации. После выдачи каждого стиМулирующего воздействия блок 1 через

5 блок 7 выдает в блок 20 эталонный код реакции объекта контроля. Все случаи несоответствия реакций объекта контроля с эталоном фиксируются в блок 12. По окончании подпрограмQ мы блок 14 определяет вид неисправности .

Если неисправность по подпрограмме не обнаружена, блок 14 принимает решение о случайном отказе объекта контроля при работе на рабочей частоте, и по адресу, записанному в регистре 16 сбоев устройство переходит к очередному участку программы.

Таким образом, в предложенном устройстве коэффициент использования оборудования повьдден, функцно- нальные возможности расширены, а среднее время контроля К одинаковых объектов контроля уменьшено.

Формула изобретения

Устройство для контроля логических узлов по авт. св. ( 469971, отличающееся тем, что, с целью повышения коэффициента использования оборудования, в него введены группа элементов И, входы которых являются соответствующими входами устройства, а первый и второй управляющие входы соединены соответственно с третьим выходом блока управления и управляющим выходом блока коммутации стимулирующих воздейстВИЙ, четверть входом соединенного с четвертым выходом блока управления, выходы элементов И группы подключены к соответствующим входам блока выявления неисправностей.

10

Оо .

га иШ

ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логическихузлОВ | 1978 |

|

SU813431A2 |

| Устройство для контроля логических узлов | 1973 |

|

SU469971A1 |

| Устройство для контроля логических блоков | 1976 |

|

SU637820A1 |

| Устройство для контроля логических узлов | 1976 |

|

SU612247A2 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Устройство для диагностирования логических узлов | 1979 |

|

SU892447A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841060A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля логичесикх узлов | 1976 |

|

SU613324A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

Авторы

Даты

1979-06-05—Публикация

1978-01-04—Подача