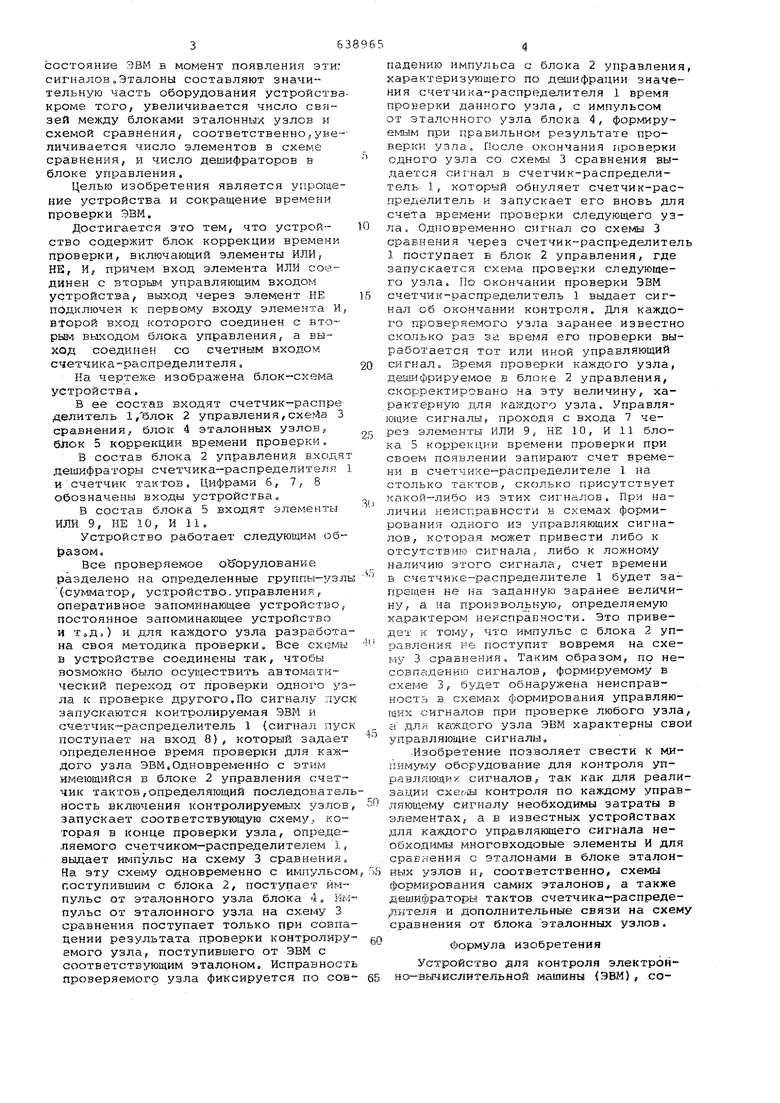

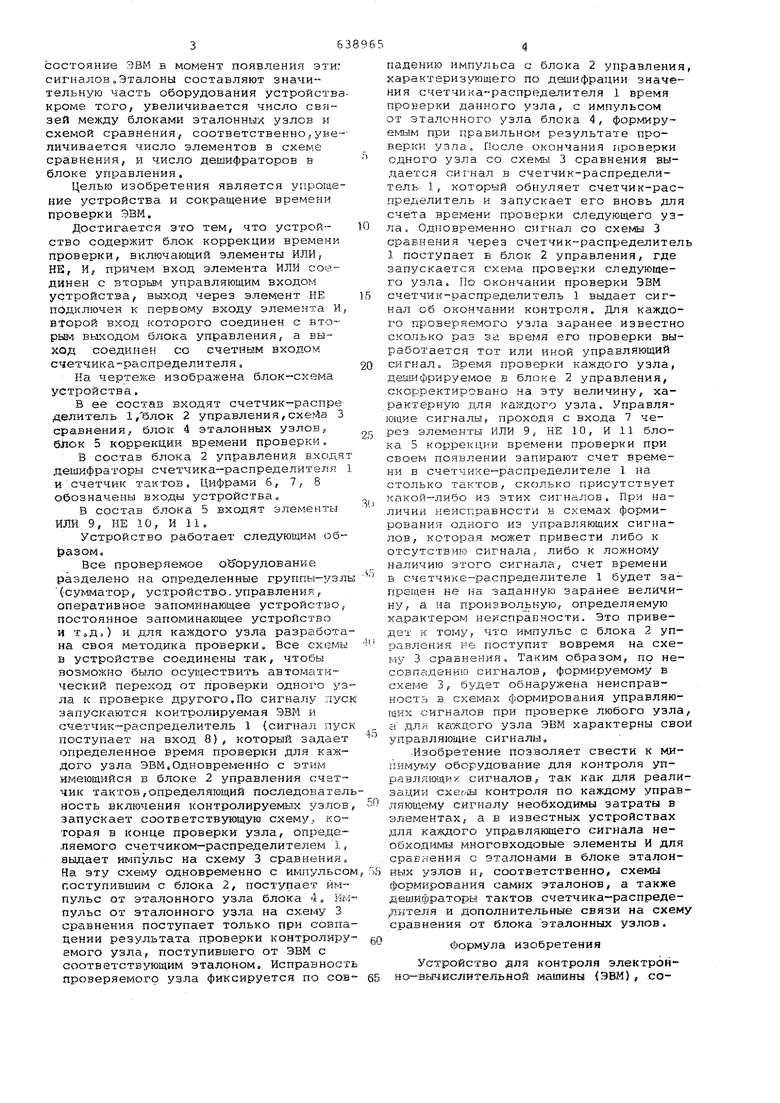

Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах для контроля и локализации места неисправности с точностью до блока. Известно устройство для контроля ЭВМ, содержащее цифровую вычислитель ную машину, регистр сравнения, соеди ненный со схемой сравнения, схему анализа, счетчик тактовых импульсов и распределитель тактовых импульсов счетчик поиска места неисправности, дешифратор тактов поиска, распределитель тактов поиска, триггер локализации места неисправности |l| . Однако это устройство является сложным, так как в нем в качестве эталона сравнения с проверяемой ЭВМ используется другая ЭВМ. Известно устройство, содержащее блок памяти для записи контролируемы событий и времени их правильного выполнения, блок подсчета фактического времени, блок сравнения времен, регистр событий, Зсщаниых во времени, входной регистр, регистр записи 2j Контроль отдельных управляющих сигналов в этом устройстве осуществляется аналогично контролю прочих событий, т.е. записи в блоке памяти самих сигналов и времени их появления с последукхцим контролем при считывании. Такой контроль требует значительных затрат зремени, так как он осуществляется последовательно с контролем основных, событий, кроме того требуется большой объем памяти. Из известных устройств наиболее близким по технической сущности к изобретению является устройство, содержащее счетчик-распределитель, блок управления, схему сравнения и блок эталонных узлов, вход которого соединен с информационным входом устройства, выход-подключен к первому входу схемы сравнения , второй вход которой соединен с первым выходе блока управления, а выход подключен к первому входу счетчика-распределителя, второй, вход которого соединен с первым управляющим входом устройства, выход соеданен с входом блока управления з. Для каждого проверяемого узла ЭВМ в устройстве имеется эталон для сравнения с ним результата проверки узла, поступающегопо инфо| 4ационному входу. Однако для контроля отдельных управлякжшх сигналов в это устрюйство также, как и для информационных сиг13алов, введены эталоны, дешифрируквдие состояние ЭВМ в момент появления эти; сигналов„Эталоны составляют значительную часть оборудования устройства кроме того, увеличивается число связей между блоками эталонных узлов и схемой сравнения, соответственно,,увеличивается число элементов в схеме сравнения, и число дешифраторов в блоке управления. Целью изобретения является ynpoiaeние устройства и сокращение времени проверки ЭВМ. Достигается это тем, что устрой-ство содержит блок коррекции времени проверки, включающий элементы ИЛИ, НЕ, И, причем вход элемента ИЛИ соединен с вторым управляющим входом устройства, выход через элемент НЕ подключен к первому входу элемента И, второй вход которого соединен с втоptJM выходом блока управления, а выход соединен со счетным входом счетчика-распределителя, На чертеже изображена блок схема устройства, В ее состав входят счетчик-распре делитель 1/6лок 2 управления,схе:йа 3 сравнения, блок 4 эталонных узлов.. блок 5 коррекции времени проверки„ В состав блока 2 управления входя дешифраторы счетчика-распределителя и счетчик тактов Цифрами б, 1, 8 обозначены входы устройства. В состав блока 5 входят элементы ИЛИ 9, НЕ 10, И 11. Устройство работает следующим образом. Все проверяемое о горудование разделено на определенные группы-узл (-cy iмaтop, устройство, управления, оперативное запоминающее устройство, постоянное запоминающее устройство и ТаДа) и для каждого узла разработа на своя методика проверки. Все схемы в устройстве соединены так, чтобы возможно было осуществить автоматический переход от проверки одно1о уз ла к проверке другого.По сигналу пус запускаются контролируемая ЭВМ и счетчик-распределитель 1 {сигнал пус поступает на вход 8) , который задает определенное время проверки для каждого узла ЭВМ.Одновременно с этим имеющийся в блоке 2 управления счетчик тактов,определяющий последовател ность включения контролируемых узлов запускает соответствующую схему., которая в конце проверки узла, определяемого счетчиком-распределителем 1, вьщает импульс на схему 3 сравнения. На эту схему одновременно с импульсо поступившим с блока 2, поступает импульс от эталонного узла блока 4, Им пульс от эталонного узла на схему 3 сравнения поступает только при совпа дении результата проверки контролиру емого узла, поступившего от ЭВМ с соответствующим эталоном Исправност проверяемого узла фиксируется по сов падению импульса с блока 2 управления, характеризующего по дешифрации значения счетчика-распределителя 1 время проверки данного узла, с импульсом от эталонного узла блока 4, формируемым при правильном результате проверки узла После окончания проверки одного узла со схемы 3 сравнения выдается сигнал в счетчик-распределитель 1, который обнуляет счетчик-распределитель и запускает его вновь для счета времени проверки следующего узла Одновременно сигнал со схемы 3 сравнения через счетчик-распределитель 1 поступает в блок 2 управления, где запускается схема проверки следующего узла По окончании проверки ЭВМ счетчик-распределитель 1 выдает сигнал об окончании контроля. Для каждого проверяемого узла заранее известно сколько раз за время его проверки выработается тот или иной управляющий си гнал о Время проверки каждого узла, дешифрируемое в блоке 2 управления, скорректировано на эту величину, характерную для каждого узла. УправляГсщие сигналы, проходя с входа 7 через элементы ИЛИ 9, НЕ 10, И 11 блока 5 коррекции времени проверки при своем появлении запирают счет времени в счетчике-распределителе 1 на столько тактов, сколько присутствует какой-либо из этих сигналов. При наличии неисправности в схемах формирования одного из управляющих сигналов, которая может привести либо к отсутствию сигнала, либо к ложному наличию этого сигнала, счет времени Б счетчике-распределителе 1 будет запрещен не на заданную заранее величину, а на произвольную, определяер.1ую характером неисправности. Это приведет к тому, что импульс с блока 2 управления не поступит вовремя на схему 3 сравнения. Таким образом, по несовпс1дени 0 сигналов, формируемому в схеме 3, будет обнаружена неисправность в схемах формирования управляющих сигналов при проверке любого узла, а ДЛИ каждого узла ЭВМ характерны свои управляющие сигналы. Изобретение позволяет свести к минимуму оборудование для контроля управля.тадих скгнапов, так как для реализа-дии -cxef.-ifca контроля по каждому управляющему сигналу необходимы затраты в элементах, а в известных устройствах для каждого управляющего сигнала необхгодимы многовходовые элементы И для сравнения с эталонами в блоке эталонных узлов и, соответственно, схемы формирования самих эталонов, а также дешифраторы тактов счетчика-распределителя и дополнительные связи на схему сравнения от блока эталонных узлов. Формула изобретения Устройство для контроля электронно-вычислительной машины (ЭВМ), содержащее счетчик-распределитель, блок управления, схему сравнения и блок эталонных узлов, вход которого соединен с информационньл. входом устройства, выход подключен к первому входу схемы сравнения, второй вход которой, соединен с первым выходом блока управления, а выход подключен к первому входу счетчика-распределителя, второй вход которого соединен с первьгм управляюидим входом устройства, выход соединен с входом блока управления, отличающееся тем, что, с целью упрощения устройства и сокра- щения времени проверки ЭВМ, оно содержит блок коррекции времени проверки, включающий элементы ИЛИ, НЕ, И,

причем вход элемента ИЛИ соединен с вторым управляющим входом устройства, выход через элемент НЕ подключен к первому входу элемента И, второй вход которого соединен с вторым выходом блока управления, а выход соединен со счетным входом счетчика-распределителя .

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

№ 435526, М,Кл.2 Q 06 Г 11/00,1974.

2.Патент США № 3723975,

кл, 340-172,5,М,Кл Q 06 Р 9/00, 1973.

3.Авторское свидетельство СССР

W 149262, М.Кл/ q 06 F 11/00, 1961.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДУПЛЕКСНЫХ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 1967 |

|

SU435526A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1128267A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

S I

Авторы

Даты

1978-12-25—Публикация

1976-04-13—Подача