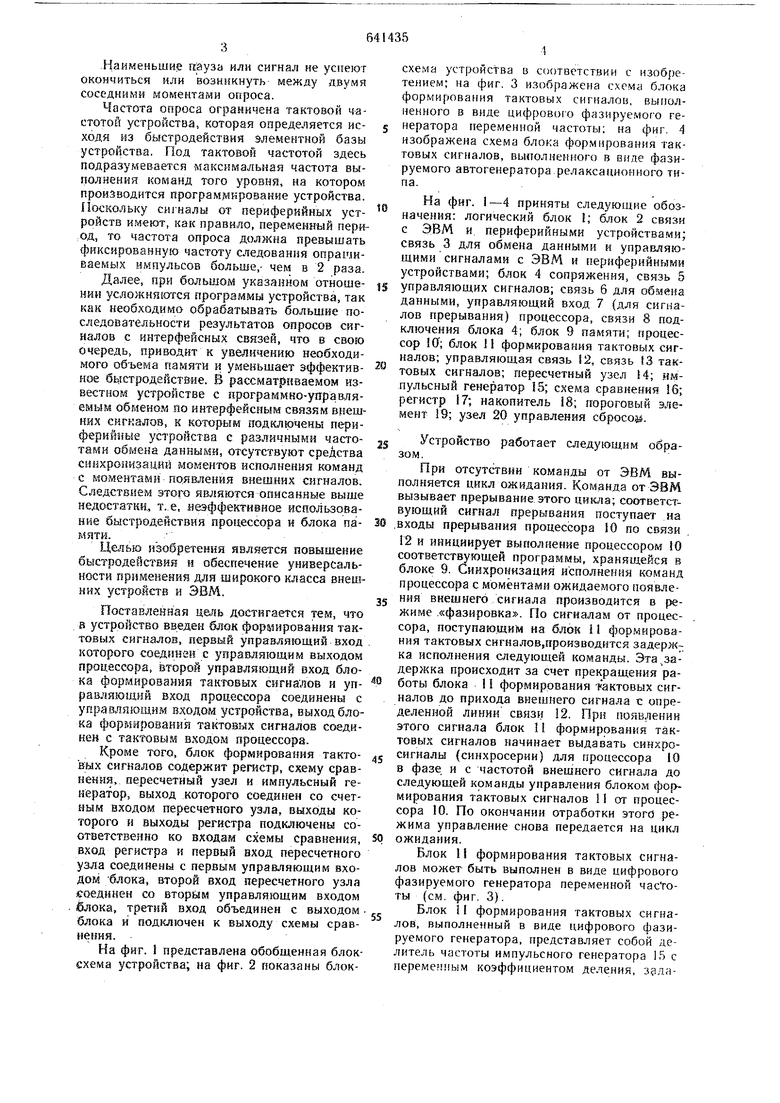

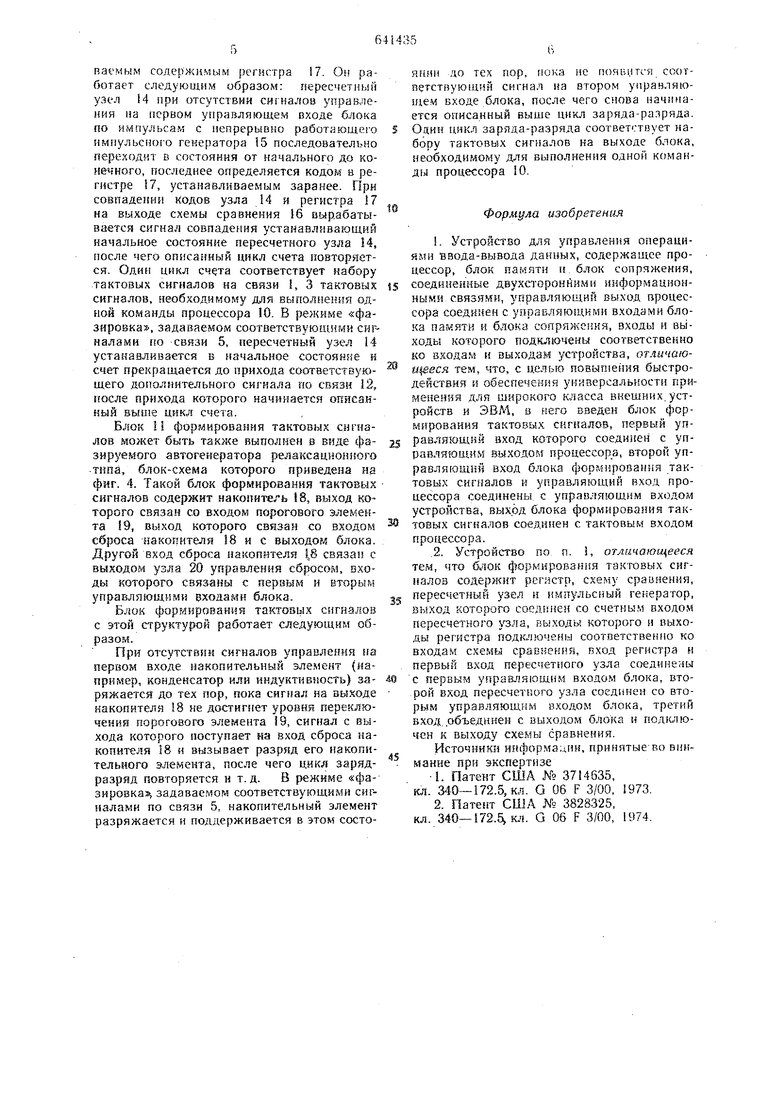

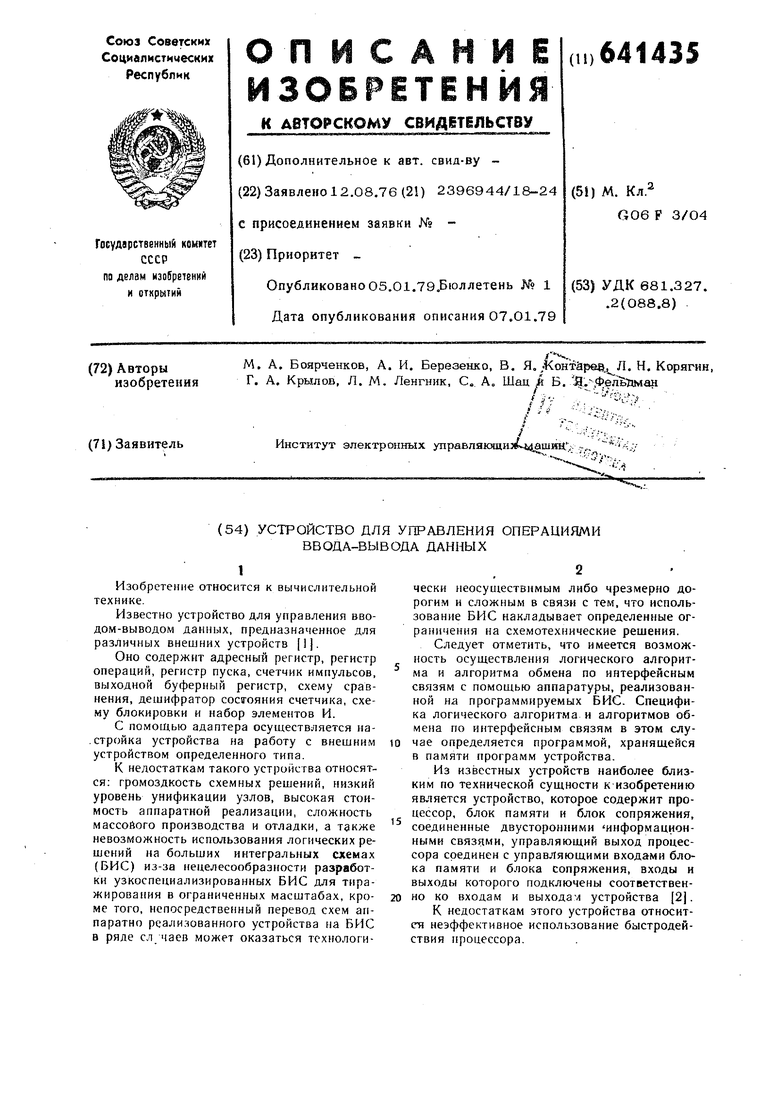

(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАЦИЯМИ ВВОДА-ВЫВОДА ДАННЫХ .Наименьшие ггйуза или сигнал не успеют окончиться или возникнуть- между двумя соседними моментами опроса. Частота опроса ограничена тактовой чаcTOTOEli устройства, которая определяется исходя из быстродействия элементной базы устройства. Под тактовой частотой здесь подразумевается максимальная частота выполнения команд того уровня, на котором производится программирование устройства. Поскольку сигналы от периферийных устройств имеют, как правило, переменный пери:Од, ТО частота опроса должна превышать фиксированную частоту следования опрашиваемых импульсов больше,- чем в 2 раза. Далее, при больо ом указанном отношении усложняЕОтся программы устройства, так как необходимо обрабатывать большие последовательности результатов опросов сигналов с интерфейсных связей, что в свою очередь, приводит к увеличению необходимого объема памяти и уменьшает эффективное бь етродействие, В рассматриваемом известном устройстве с «рограммко-уяравляемым обменом по интерфейсным связям внешних сигналов, к которым подключены периферийные устройства с различными частот&ын обмена данными, отсутствуют средства CHHxpoiSHsaumi моментов исполнения команд с моментами появления вкешних сигналов. Следствием этого являются описанные выше недостатки., т..е, неэффективное использование быстродействия процессора и блока памяти. Целью изобретения является повышение быстродействия и обеспечение универсальности применения для широкого класса внешних устройств и ЭВМ. Поставленная щель достигается тем, что 8 устройство введен блок формирования тактовых сигналов, первый управляющий вход которого соединен с управляющим выходом процессора, второй управляющий вход блока формирования тактовых сигналов и управлйющий вход процессора соединены с управляющим входом устройства, выход блока фор&шровани)Я тактойых сигналов соединен с raKtoBbiM входом процессора. Кроме того, блок формирования тактоЕых сигналов содержит регастр, схему сравнения, пересчетиый узел и импульсный генератор, выход которого соединен со счетным входом пересчетного узла, выходы которого и выходы регистра подключены соответственно ко входам схемы сравнения, вход регистра и первый вход пересчетного узла соединены с первым упраааяющим входом блока, второй вход пересчетного узла еоединен со вторим управляющим входом . (блока, третий вход объединен с выходом блока н подключен к выходу схемы сравиения. На фиг. 1 иредставлена обобщенная блок схема устройства; на фиг. 2 показаны блоксхема устройства в соответствии с изобретением; на фиг. 3 изображена схема блока фор.мирования тактовых сигналов, выполненного в виде цифрового фазнруе.мого генератора переменной частоты: на фиг. 4 изображена схема блока формирования тактовых сигналов, вьнюлнениого в виде фазируемого автогенератора релаксационного типа. На фиг. 1-4 приняты следующие обозначения: логический блок ; блок 2 связи с ЭВМ и периферийными устройствами; связь 3 для обмена данными и управляющимисигналами с ЭВМ и перифериннырли устройствами; блок 4 сопряжения, связь 5 управляющих сигналов; связь б для обмена данными, управляющий вход 7 (для сигналов прерывания) процессора, связи 8 подключения блока 4; блок 9 памяти; процессор Ш; блок 1 формирования тактовых сигналов; управляющая связь (2, связь 13 тактовых сигналов; пересчетный узел 4; импульсный генератор 5; схема сравнения 16; регистр 17; накопитель 18; пороговый элемент 19; узел 20 управления сбросоа. Устройство работает следующим образом. При отсутствии команды от ЭВМ выполняется цикл ожидания. Команда от Э8М вызывает прерывание этого цикла; соответствующий сигнал прерывания поступает на .входы прерывания процессора 10 по связи 12 и инициирует выполиеняе процессором 0 соответствующей программы, хранящейся в блоке 9. Синхронизация исполнения команд процессора с моментами ожидаемого iioHB-ieния внешнего сигнала производится в реЖиме .«фазировка. По сигналам от процессора, поступающим на блок формирования тактовых снгналов.производится задержка исполнения следующей команды. Эта задержка происходит за счет прекращения работы блока 11 формирования тактовых сигналов до прихода внешнего сигнала с определенной линии связи 12. При появлении этого сигнала блок 11 формирования тактовых сигналов начинает выдавать синхросигналы (синхросерии) для процессора 10 в фазе, и с частотой внешнего сигнала до следующей команды управления блоком фогь мирования тактовых сигналов 1I от процессора 10. По окончании отработки этого режима управление снова передается на цикл ожидания. Блок I i формирования тактовых сигналов может быть выполнен в виде цифрового фазируемого генератора переменной частоты (см. фиг. 3). Блок II формирования тактовых сигналов, выполненный в виде цифрового фазируемого генератора, представляет собой делитель частоты импульсного генератора 15 с переменным коэффициентом деления, залаваемым содержимым регистра 17. Он работает следующим образом: г ересчетный узел 14 при отсутствии сигналов управления на первом упрг) входе блока по импульсам с непрерывно работйющего импульсного генератора 15 последовательно переходит в состояния от начального до конечного, гос.чеднее определяется кодом в регистре 17, устанавливаемым заранее. При совпадении кодов узла 14 и регистра 17 на схемы сравнения 16 вырабатывается сигнал совпадения устанавливающий начальное состоянке пересчетного узла 14, после чего опясанный цикл счета повторяется. Один цикл счета соответствует набору тактовых сигналов на связи 1, 3 тактовых сигналов, необходимому для выполнения одной команды процессора 10. В режиме «фазировка, задаваемом соотаетствующнми сигналами по связи 5, пересчетный узел 14 уста1{азливается в начальное состояние и счет прекращается до прихода соответствующего дополнительного сигнала но СБЯЗН 12, гюсле прихода которого начинается описанный выше цикл счета.

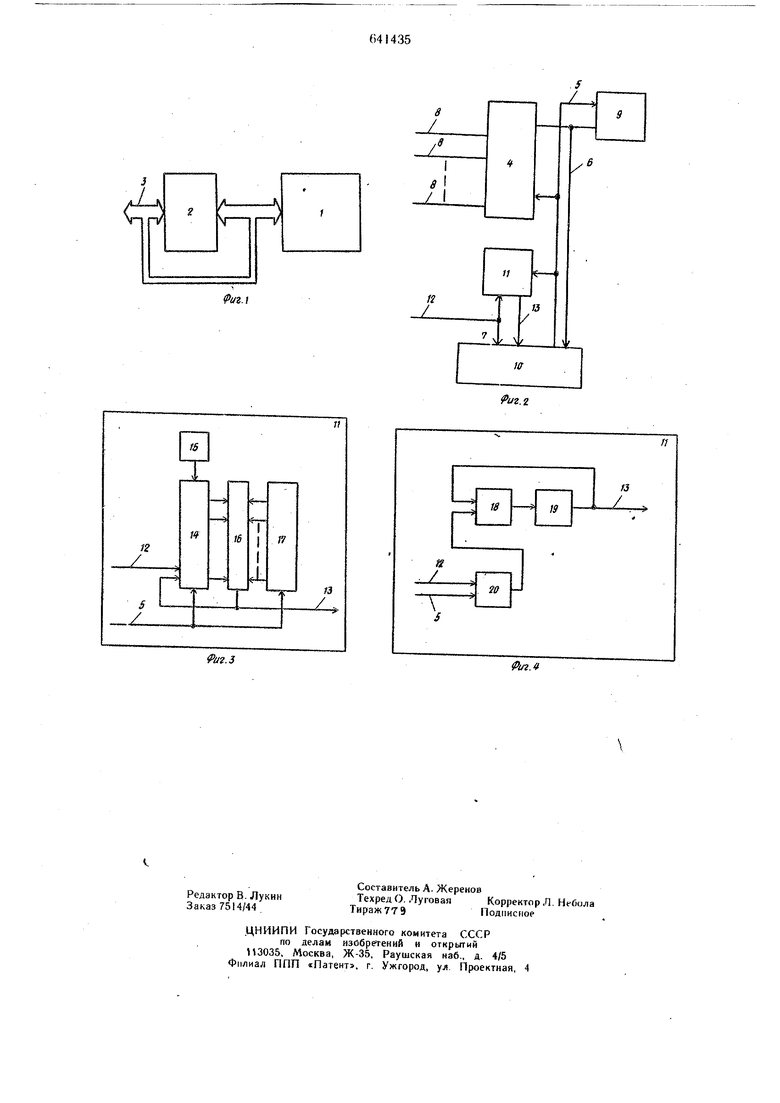

Блок 11 формирования тактовых сигналов может быть также выполнен в виде фазируемого автогенератора релаксациогиюго -Т1ша, блок-схема которого приведена на фиг. 4. Такой блок формирования тактовых сигналов содержит накопнгегь 18, выход которого связан со входом порогового элемента 19, выход которого связан со входом сброса иаког итеу1я 18 и с выходом блока. Другой вход сброса накопителя 8 связан с выходом узла 20 угфааления сбросом, входы которого связаны с первым и вторым управляющими входами блока.

Ьлок форрлгфования тактовых сигналов с этой структурой работает следующим образом.

При отсутствии сигналов управления на первом входе накопительный элемент (например, конденсатор или индуктивгюсть) заряжается до тех пор, пока сигнал на выходе накопителя 18 не досгиг ет уровни переключения гюроговопз элемента 19, сигнал с выхода которого поступает на вход сброса накопителя 18 н вызывает разряд его какопителыюго элемента, после чего цик/( зарядразряд повторяется н т. д. В режиме «фазировка, задаваемом соответствующими сигналами по связи 5, накопительный элемент разряжается и поддерживается в этом состоянни до тех пор, пока не появится соотпетстг ующий сигнал на втором управляющем входе блока, после чего снова начинается опнсанный выше цикл заряда-разряда. Один цикл заряда-разряда соответствует набору тактовых сигналов на выходе блока, необходимому для выполнения одной к(манды процессора 10.

Формула изобретения

1.Устройство для управления операциями ввода-вывода данных, содержащее процессор, блок памяти и. блок сопряжения, соединенные двухсторонними информационными связями, управляющий ВЫХО.Д процессора соединен с уоравляющими входами блока памяти и блока сопряжения, входы н выходы которого подк. соответственно ко входам ч выходам устройства, отличшои еся тем, что, с целью по8ып ения быстродействия и обеспечения укизерсальиостн применения для широкого класса внешних,устройств и ЭВМ, а него введен блок форрлйрования такторзых сигналов, первый управл5 ющий вход которого соединен с управляюаим выходом процессор а, второй управляющий вход блока формнройания тактовых снгьалов и управляющий вход процессора соединены, с упра 5ляюш.н.м входом устройства, вых,дд блока формирования тактовых сигналов соединен с тактовым входом процессора.

,2. Устройство по п. 1, отличающееся тем, что блок формирОБан я тахтовьлх сигналов содержит регистр, схему сравнения, пересчетный узел н импульсный reiiepaTOp, выход которого coeAiiiieH со счетным входом пересчеткого узла, выходы которого и выходы регистра подключены соответственно ко входам схемы сравнения, вход регистра н первый вход пересчетпого узла соедш ены с первым управляющим входом блока, вто,рон вход пересчет(5ого узла соединен со вторым управляющим входом блока, третий вход, объединен с выходом блока и под(.лючсн к выходу схемы сравнения.

Источники ниформации, принятые-во внимание при экспертизе

1. Патент США № 3714635, кл. 34-0-172.5, кл. G 06 F 3/00, 1973.

2.Патент США № 3828325,

кл. 340-172.5, кл. G 06 F 3/00, 1974.

f3

W

16

n

12

JL

a

/.

5 /

аг.З

к

/

й/г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство сопряжения процессора с внешними устройствами | 1987 |

|

SU1509893A1 |

| Устройство синхронизации двух ЭВМ | 2018 |

|

RU2682402C1 |

Авторы

Даты

1979-01-05—Публикация

1976-08-12—Подача