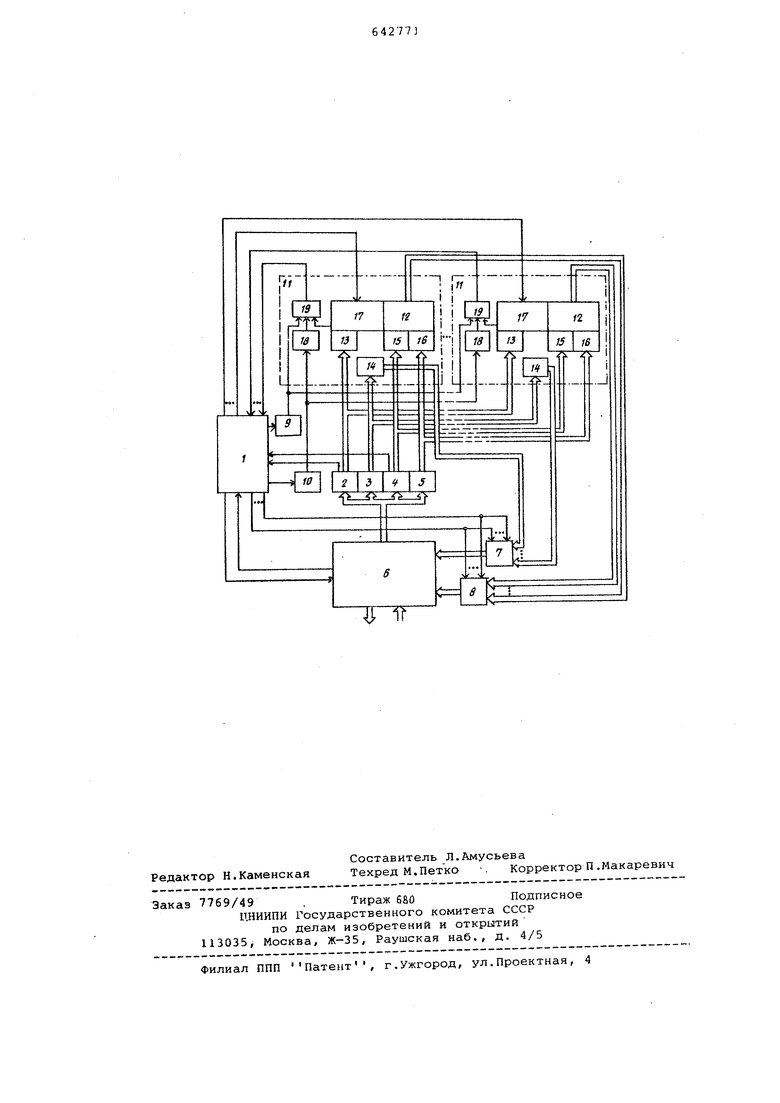

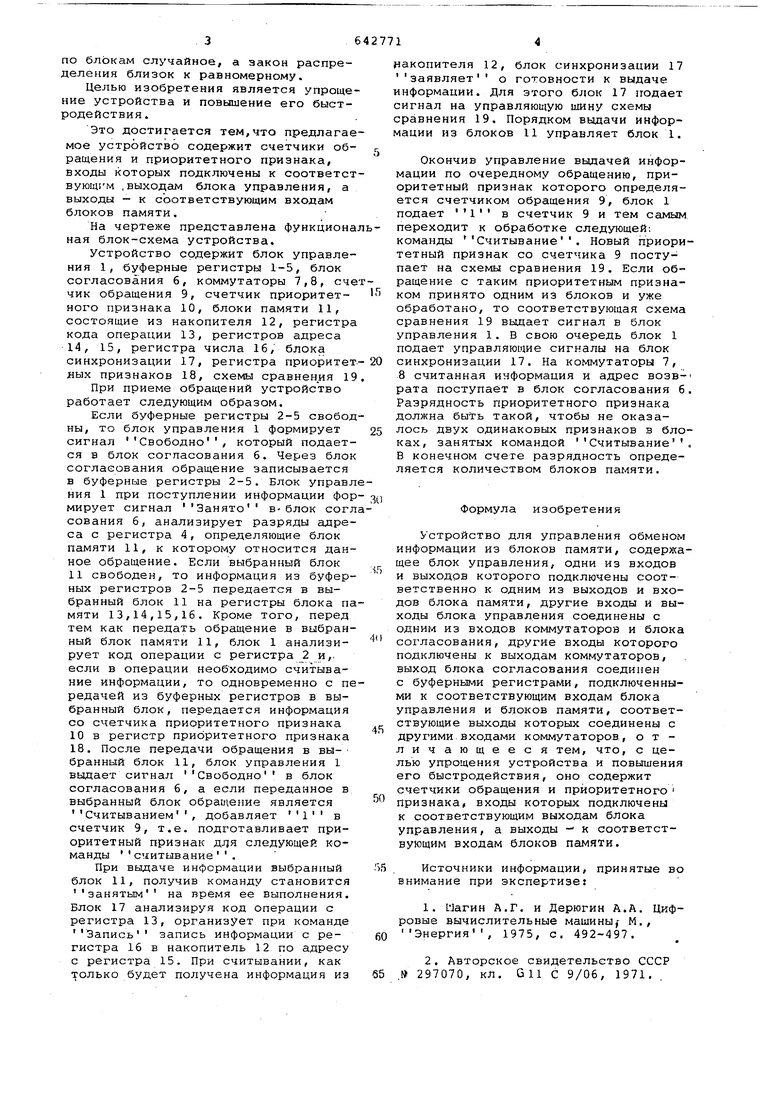

по блокам случайное, а закон распределения близок к равномерному. Целью изобретения является упроще ние устройства и повышение его быстродействия. Это достигается тем,что предлагае мое устройство содержит счетчики обращения и приоритетного признака, входы которых подключены к соответст вующим ,выходс1М блока управления, а выходы - к соответствующим входам блоков памяти. На чертеже представлена функциона ная блок-схема устройства. Устройство содержит блок управления 1, буферные регистры 1-5, блок согласования 6, коммутаторы 7,8, сче чик обращения 9, счетчик приоритетного признака 10, блоки памяти 11, состоящие из накопителя 12, регистра кода операции 13, регистров адреса 14, 15, регистра числа 16, блока синхронизации 17, регистра приоритет ных признаков 18, схемы сравнения 1 При приеме обращений устройство работает следующим образом. Если буферные регистры 2-5 свобод ны, то блок управления 1 формирует сигнал Свободно, который подается в блок согласования 6. Через блок согласования обращение записывается в буферные регистры 2-5. Блок управл ния 1 при поступлении информации фор мирует сигнал Занято в-блок согл сования б, анализирует разряды адреса с регистра 4, определяющие блок памяти 11, к которому относится дан ное обращение. Если выбранный блок 11 свободен, то информация из буферных регистров 2-5 передается в выбранный блок 11 на регистры блока п мяти 13,14,15,16. Кроме того, перед тем как передать обращение в выбран ный блок памяти 11, блок 1 анализирует код операции с регистра 2 и,, если в операции необходимо считывание информации, то одновременно с п редачей из буферных регистров в выбранный блок, передается информация со счетчика приоритетного признака 10 в регистр приоритетного признака 18. После передачи обращения в вы- бранный блок 11, блок управления 1 выдает сигнал Свободно в блок согласования 6, а если переданное в выбранный блок обращение является Считыванием, добавляет i в счетчик 9, т.е. подготавливает приоритетный признак для следующей команды считывание. При выдаче информации выбранный блок 11, получив команду становится занятым на время ее выполнения. Блок 17 анализируя код операции с регистра 13, организует при команде Запись запись информации с регистра 16 в накопитель 12 по адресу с регистра 15. При считывании, как только будет получена информация из акопителя 12, блок синхронизации 17 заявляет о готовности к выдаче нформации. Для этого блок 17 подает игнал на управляющую шину схемы равнения 19. Порядком выдачи инфорации из блоков 11 управляет блок 1. Окончив управление выдачей информации по очередному обращению, приоритетный признак которого определяется счетчиком обращения 9, блок 1 подает i в счетчик 9 и тем самым переходит к обработке следующей: команды Считывание. Новый приоритетный признак со счетчика 9 поступает на схемы сравнения 19. Если обращение с таким приоритетным признаком принято одним из блоков и уже обработано, то соответствующая схема сравнения 19 выдает сигнал в блок управления 1. В свою очередь блок 1 подает управляющие сигналы на блок синхронизации 17. На коммутаторы 7, 8 считанная информация и адрес возв-i рата поступает в блок согласования 6. Разрядность приоритетного признака должна быТь такой, чтобы не оказалось двух одинаковых признаков в блоках, занятых командой Считывание. В конечном счете разрядность определяется количеством блоков памяти. Формула изобретения Устройство для управления обменом информации из блоков памяти, содержащее блок управления, одни из входов и выходов которого подключены соответственно к одним из выходов и входов блока памяти, другие входы и выходы блока управления соединены с одним из входов коммутаторов и блока согласования, другие входы которого подключены к выходам коммутаторов, выход блока согласования соединен с буферными регистрами, подключенными к соответствующим входам блока управления и блоков памяти, соответствующие выходы которых соединены с другими,входами коммутаторов, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, оно содержит счетчики обращения и приоритетного признака, входы которых подключены к соответствующим выходам блока управления, а выходы - к соответствующим входам блоков памяти. Источники информации, принятые во внимание при экспертизе: 1.Иагин А.Г. и Дерюгин А.А. Цифровые вычислительные машины М., Энергия, 1975, с. 492-497. 2.Авторское свидетельство СССР . 297070, кл. Gil с 9/06, 1971.

ir

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными | 1974 |

|

SU506847A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

Авторы

Даты

1979-01-15—Публикация

1977-07-25—Подача