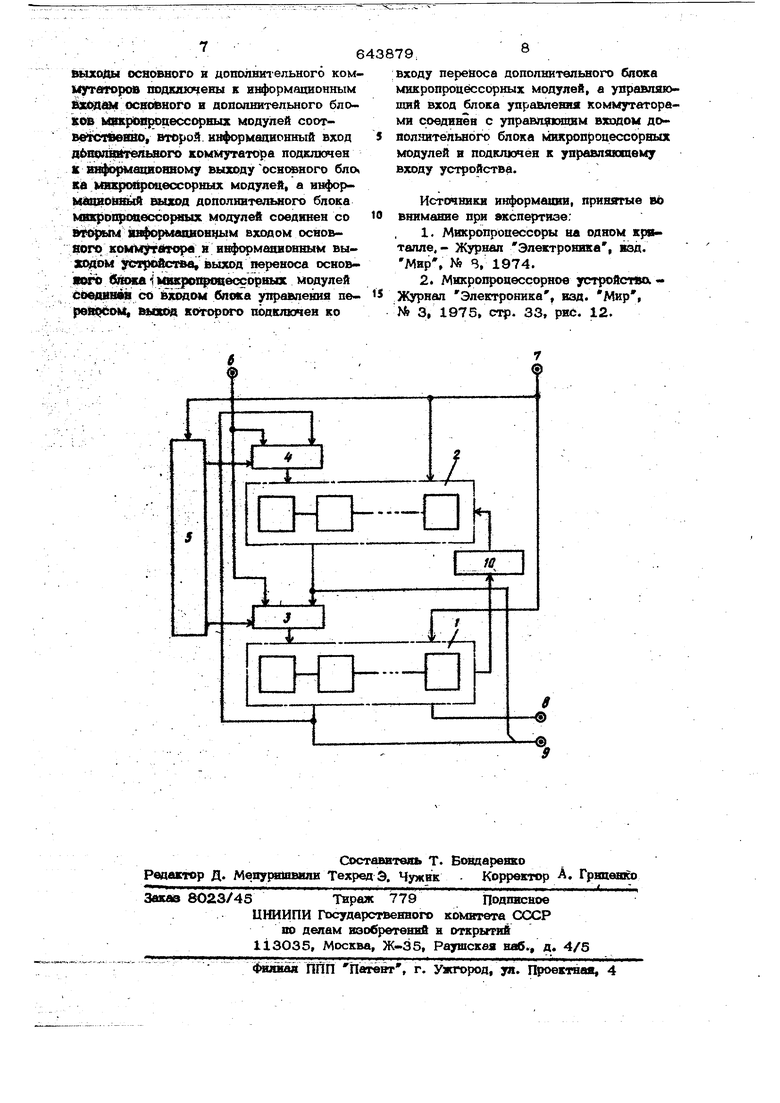

(54) МИКРОПРОЦЕССОРНОЕ. ВЫЧИСЛИТЕЛЬЮЕ .УСТРСЙСТВО ВЫХОДЫ которого подключены к управляющим входам основного и дополнительно- го коммутаторов соответственно, первые информацирнные входы которых под)ючены к информшионному входу устройства, а выходы основного и дополниTfiitbHoro коммутаторов подключены к нн.формационмым входам основного и дополнительного блоков микропроцессорных мо дулей соответственно, второй ннформационный вход дополнительного коммутатора подключен к информд1шош1ому выходу основного блока микропроцессорных модулей, а информационный выход дополниTertwioro блока микропроцессорных модулей соединен со вторым информационным входом dCHOi&HOtO коммутатора и информационным выходом устройства, выход переноса основного блока микроггроцессорных модулей соединен со входом блока управлений иереносрм .вызьод которого подключен ко входу переноса дополнительного блтаа мйсропроаессорйых модулей, а управляоснаий вход блока уп коммутаторами лоедийен с упрбвпшошим входом дополнительного блежа Микропроцессорных модулей и подключен к уяравлякяцему входу устройства На чертеже представлена функциональная схема микропроцессорного вычисли тельного устройства. Микропроцессорное вычисяительное устройство содержит: основной 1 микропроцессорных модулей, допсяшитеяь ный блок 2 микропроя«гсорных модулей, основной коммутатор 3, дойЬйнительаьвй коммутатор 4 блок 5 упра&леявя коммутаторами, информационный вход 6 устройст аа, уир яювшй взсод 7, адресный выход 8, шф)рмйционный выход 9, блсж 10 управивння переносом. Управляющие входы блока 5 уйравlfёmя коммутаторами подкточены к управляющему входу 7 устройства, а выходы блоКа 5 управления коммутаторами подключены к управляющим входам основного коммутатора 3 и дополнительного коммутатора 4, Первые инф6рм аайонкые входы которых подключены к информ аионному входу -6 устройства, а выходы соответственно подключены к информационным входам основного блока 1 микропроцессорных модулей и дополнительного блока 2 микропроцессорных модулей, управпяюишв входы которых подключены к управляющему входу 7 устройства. Ин рмащюнный выход основного блока Д. Члшропроцессорных модулей и дополш тельного блока 2 соединены с информационным выходом 9 устройства. Кроме того, информацЬонный выход основного блока 1 микропроцессорных модулей подключен ко второму информационному входу дополнительного коммутатора 4, а информационный выход дополнительного блока 2 микропроцессорных модулей подключен ко второму информационному входу основного коммутатора 3. Выход адреса основного блока 1 микропроцессо ных модулей соединен с адресным выходом 8, а выход переноса подключен ко входу блока 10 управления переносом, выход которого подключен ко входу переноса дополнительного блока 2 микропроцессорных модулей. Работу микропроцессорного вычислительного устройства рассмотрим, например, при выполненииI короткой операции типа сложение. {Ц выполнении операции в формате регистр-регистр (согласно системе команд ЕС ЭВМ) допустим, что первый операнд (адрес R-f ) находится в основном блоке 1, а второй {адрес R2) - в дополнительном блоке 2. В этом случае выполнение операции происходит в том блоке микропроцессорных модулей, где находатса первый операнд ( lif ). Поэтому второй операнд ( К2 ) необходимо переслать в основной блок 1 микропроцессорных модулей. На управляющий вход 7 устройства поступает последовательность микрокоманд. Первая микрокоманда подается на дополнительный блок 2 микропроцессорных модулей и на управлякшше входы блока 5 управления коммутаторами. На управляющий вход основного блока 1 микропроцессорных модулей со входа 7 устройства подается холостая команда. При этом происходит передача второго оперангда ( |2|| ) на вызи)Д допол1Штелы{ого блока 2 микропрсяаессорных модулей и далее - на второй информационный вход оснЬвного коммутатора 3. На выходе бло ка 5 упра)йления коммутаторами появляется управлякшшй сигнал, который разрещает прохождение второго операнда ( R2) через основной коМмугатбр 3 на нгаформашонЬый вход основного блсжа 1 мик- рояроцессорных модулей. Прн подаче.следующей микрокоманды происходит выпол нение операции и результат onepmtHH остается в основном блоке 1 микропроцессорных модулей (согласно системе кЪ манд ЕС ЭВМ). 56 ЕСЛИ первый операнд { R1) находится в дополнительном блоке 2 микропроцессорных («одулей, а второй операнд (R2 ) - в основном блоке 1, то абота устройства происходит аналогичным образом, только операция выполняется- в дополнительном блоке 2 микропроцессорных модулей, При вьшолнении операции в формате регистр-память (согласно системе ко манд ЕС ЭВМ из внешней памяти на информационный вход устройства подает ся п -разрядное слово (X) на первые информационные входы основного комму татора 3 и дгщолнительного коммутётора 4. Допустим, что первый операнд ( RI ) находится в дополнительном блоке 2 микропроцессорных модулей. На вход 7 устройства подается последовательность микрокоманд. Первая микроко- манда поступает на управляющие входы блока 5 управления коммутаторамч и обеспечивает появление на его выходе управляющего сигнала, который разрешает прохождение М -разрядного слова (X) Ни информационный вход дополнитель ного блока 2 микропроцессорных модулей через дополнительный коммутатор 4. При подачб следующей микрокоманды про исходит выполнение операции. Если первый операнд ( R-i ) находится в основном блоке 1 микропроцессорных модулей, то работа устройства происходит аналогичным образом, только операция выполняется в основном блоке 2 микропроцессорных модулей. При работе с 2 П -разрядными словами в основном блоке 1 микропроцессорных модулей находится младшая часть 2 П - разрядного слова, а в дополнитель ном блоке 2 микропроцессорных модулей - старшая часть 2 11 -разрядного слова. Из внешней памяти 2 П - разрядной магистрали на вход устройства 6 подается 2 h разрядное слово на первые информационные входы основного коммутатора 3 и дополнительного коммутатора 4. На управляющий вход 7 поступает последовательность микрокоманд, которая подается на управлякяпие входы блока 5 управления коммутаторами и на управляющие входы основного блока 1 в дополнительного блока 2 микропроцессорных модулей. Первая микрокоманда обеспечивает цоявленве на выходе блока 5 управления коммутаторами управляюшего сигнала, который разрешает прохождение младшей части 2 h -разряд79ного слова на информационный вход основного блока 1 микропроцессорных модулей через основной коммутатор 3, а старшей части 2 Я -рвзрядного слова на информаЕИонный вход дополнительного блока 2 микропрсщессорных модулей через дополнительнь1й коммутатор 4. При подаче следующей микрокоманды происходит выполнение операции. По окончании операции,если появляется перенос из младшей части 2 Цразрядного слова в старшую часть, то он поступает с выхода переноса основного блока 1 микропроцессорных модулей через блок 1О управления переносом на вход переноса дополнительного блока 2 микропроцессорных модулей, где по очередной микрокоманде, формируется окончательный результат опеУвеличение встроенной сверхоперативной памяти путем введения дополнительного блока микропроцессорных модулей, основного и дополнительного коммутаторов, блоков управления переносом и коммутаторами позволило расширить функциональные восзможности микропроцессорного вьгчислительного устройства, .а также увеличить быстродействие более, чем в 1,5 раза путем уменьшения времени обработки 2 п - разрядной информации. формула изобретения Микропроцессорное вычислительное устройство, содержащее основной блок микропроцессорных модулей, управляющий вход которого подключен к управляющему входу устройства, информационный выход основного блока микропроцес-, сорных модулей подключен к информационному выходу устройства, адресный выход, основного блока ьшкропроцессорных модулей соединен с адресным выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены дополнительный блок микропроцессорных модулей, рсновной я дополнительный коммутаторы, блок управления переносом и блок управления комм -таторами, первый и второй выходы которого подклюхгены к управляюпгам входам основного в дбполннтелыюго коммутаторов соответственао, вёреые информационные входы которых подклктены к информашюввому входу устройства, &

waxofe основного и допопния-ельного коммутаторш подхдкчевы к информационным осноёного н доооошительного бпоков мшс яшроаессорных модулей соотвегствеЕЕВо, второй, информационный вход дбшмшйгеяьвого коммутатора подключен X 11Я)ф6{ маш1оаному выходу осн жного бло ка шкро11р(М1вссорных модулей, а ннфор МЮшоешый BiiUcoA дополнительного блока мвзфопрсшессориых модулей соединен со вторым йвформаоновщлм &хоаом основного коммутАгора н информааионным выходом устройстве, выход переноса основного I мвк|Ю1 1И|ессор1шх модулей СбениЕИП со бходом блока управления пеpe QbOM, пьосбя которсяч} подключен ко

входу переноса дополнительного бпсжа микропроцессорных модулей, а управляющий вход блока управления коммутаторами соединен с улравл кшшм входом дополнительного блока мшсропроцессорвых модулей и подключен к управляюшему входу устройства.

Источники информации, принятые во внимание при экспертизе;

1.Микропроцессоры на одном кро тапле. - Журнал Электроника, кзд. Мир, № В, 1974.

2.Микропроцессорное устройства Журнал Электроника, изд. Мир,

М 3, 1975, стр. 33, рнС. 12.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

Авторы

Даты

1979-01-25—Публикация

1976-12-27—Подача