(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электропитания электронных вычислительных машин | 1984 |

|

SU1164714A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Коммутатор | 1978 |

|

SU723777A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Коммутатор | 1984 |

|

SU1167720A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

- . .1 .

Иэобрегение относится к коммутаци-онной технике.

Известны коммутаторы, содержащие в каждом канале элемент И один из входов которого соединен с соответствующей входной шиной коммутатора, а также элементы ИЛИ, И, регистр сдвига, рас1чэеделитоп1Ь, триггер и элемент задержки l .

Целью изобретения является повышение надежности коммутатора.

Достигаегся это за счет того, что в коммутаторе, содержащем в каждом канале элемент И, один V3 входов которого соединен, с соответствующей входной шиной коммутатора, а также элементы ИЛИ, И, регистр сдвига, распределитель трэдтер и элемеит задержки, другой вход Канального элемента И соединен с соот ветствуюшим выходом распределителя, а выход - с одним из входов первого элемента И/Ш, выход которого подключен к выходной шине коммутатора и информационному входу регистра сдвига, управляющий вход которого соединен с первой шиной тактирования, прямые разрядные выходы подключены к входам nepBoix И, а инверсные разрядные выходы - к входам второго элемента И

выходы первого и элементов И соединены с.входами BTOfWiro элемента ИЛИ, выход которого подключен к единичному входу триггера, нулевой вход которого соединен с выходом элемента

задержки, единичный выход - сю входом элемента задержки, а нулевой выход с одним из входов третьего элемента И, второй вход которого подключен ко второй шине тактирование а выход - ко входу распределнтеля.

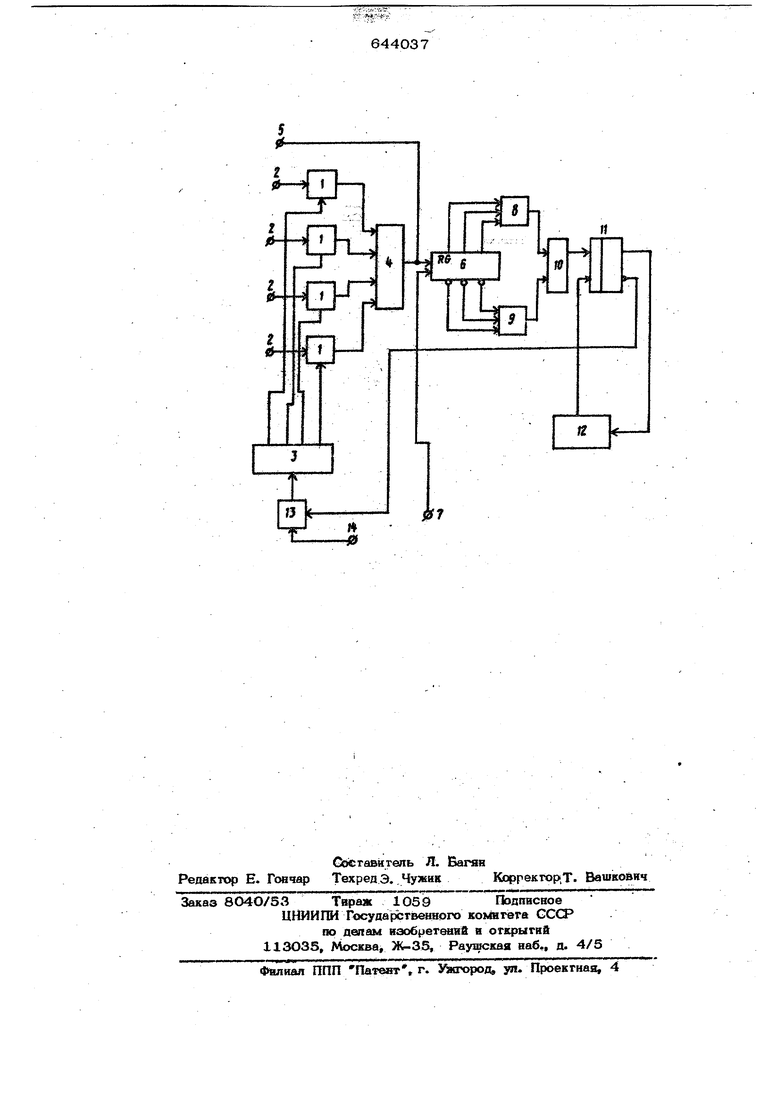

На чертеже дана функциональная схема Коммутатс эа.

Она содержит элементы И1 ,однн из входов каждого из которых соедн юн с соответсгвующей входной шиной 2 коммутатора, а второй вход соединенС соответствующим выходом распределителя 3, причем выход каждого элемента И I пошипочен

к одному из входов первого элеменга ИЛИ 4, выход которого подключен к выходной шине 5 коммутатора и информационному входу регистра сдвига 6, управляющий вход которого соединен с первой Шиной тактирования 7, прямые разрядные выходы подключены к входам первого элемента И 8, а инверсные разрядные выходы - к входам второго элемента И 9; выходы первого и второго элементов И 8 и 9 схэединены с входами, второго эпе 1ента ИЛИ 10, выход которого подключен к единичному входу триггера 11, нулевой вход которого соединен с выходом элемента задержки 12, , единичный выход - с входом элемента задерискй 12, а нулевой выход - с одним из входов третьего элемента И 13, второй вход которого подключен к второй шине тактирования 14, а выход - к входу распределителя 3.

Функционирование коммутатора осуществляется следующим образом. Расяредепитель 3 генерирует сдви нутые огйо,сительно друг друга импульсы опроса входных шин 2 коммутатора, кртсфые поступают на элементы И 1, тем самым подключая каждую из входных шин 2 4epie3 элемент ИЛИ 4 к выходной шине 5 коммутатора и йнформапибнному вхбду регистра сдвига 6, Время поочвт редного подключевил входнкк шин 2 к регистру сдвига 6 определяется ОТитель нбсгью импульсов с выхода распредели/теля 3 и г ыбирается;равньш несжопько больше межсяогового интервала, ИнформаииеЙ об активности одного иа абонентов авлается наличие на входной шине 2. пйчек из трех и более импульсов, котчэ ч рые регистрируются регистром сдвига 6, Вели появилась пачка из трёх импульсов, го и а выходе элемента ИЗ по$Ш1яется один импульс, который та1кже появится на выходе элемента ИЛИ iO, В результате этого тригг 11 переходит в единичное состояние. Время занятяя канала активным абонентом опредепйется элементом задержки 12 и выб(1ра@тся несколько больше межспогового янтервала. В этом случае с нулевого выхода трвпгера 11 запирается элемент И 13 и коммутатор находится в одном и том же состоянии до тех пор, пока активный абонент не закончит передавать инфор мацию. Как только передача информации закончится на выходе элемента ИЛИ 1О образуется нулевой логический уровень и через элемент .задержки 12 триггер 11 переходит в нулевое состояние. При этом на нулевом выходе триггера 11 появится сигнал разрешения, под действием которого распределитель 3 начнет генерировать импульсы.

15 Формула изобрете

кия

Коммутатс, содержащий в каждом канале элемент И, один из входов которого соединен с соответствующей входной шиной коммутатора, а также элемен-г ты ИЛИ, И, регистр сдвига, распределитель, триггер и элемент задержки, о тличающийся тем, что, с цепью повышения надежности, другой вход ка- ,

5 нального элемента И соеаинён с соответ ствукишим выходом распределителя, а выход - с одним из входов первого элемента ИЛИ, выход которого подключен к выходной шине коммутатора и информационному входу регистра сдВига, управ ляющий вход которого соединен с первой шиной тактирования, прямые разрядные выходь подключень ко входам первого элемента И, а инверсные разрядные выходы - ко входам второго элемента И, выходы первого и второго элементов И соединены со входами второго элемента ИЛИ, выход которого подключен к - единичному входу триггера, нулевой вход которого соединен с выходом элемента задержки, единичный выход - с входом элемента , а нулевой выход - с одним из входов третьего элемента И, второй вход которого подключен ко второй шине тактирования, а выход - к входу распределителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-01-25—Публикация

1976-12-30—Подача