: - „ . 1 .-/

Изоб|эетение относится к области специализированных вычиспитепьных устройств.

Известны преобразователи пересчетного типа ll, в которых в качестве устройства с переменным коэффициентом пересчета используется счетчик, имеющий цепи обратной с4язи и регистр, в котором записывается код, управляющий коэффициентом пересчета.

Недостатком указанных преобразователей является то, что они при высоких точностях преобразования требуют бопь- . шого объема оборудования за счет увеличения разрядаости элементов схем.то в свою очередь снижает быстродействие.

Наиболее близким к данному техническим решением является устройство содержащее ц -разрядный входной регистр, логический блок блок управления и первой дешифратор, причем выходьг (П - К ) старших разрядов входного регистра соединены со входами первого дешифратора, группа выходов которого

соединена с первой группой входов блок задания характеристики.

Недостатком известного устройства является его сложность.

Целью изобретения является упрощение устройства.

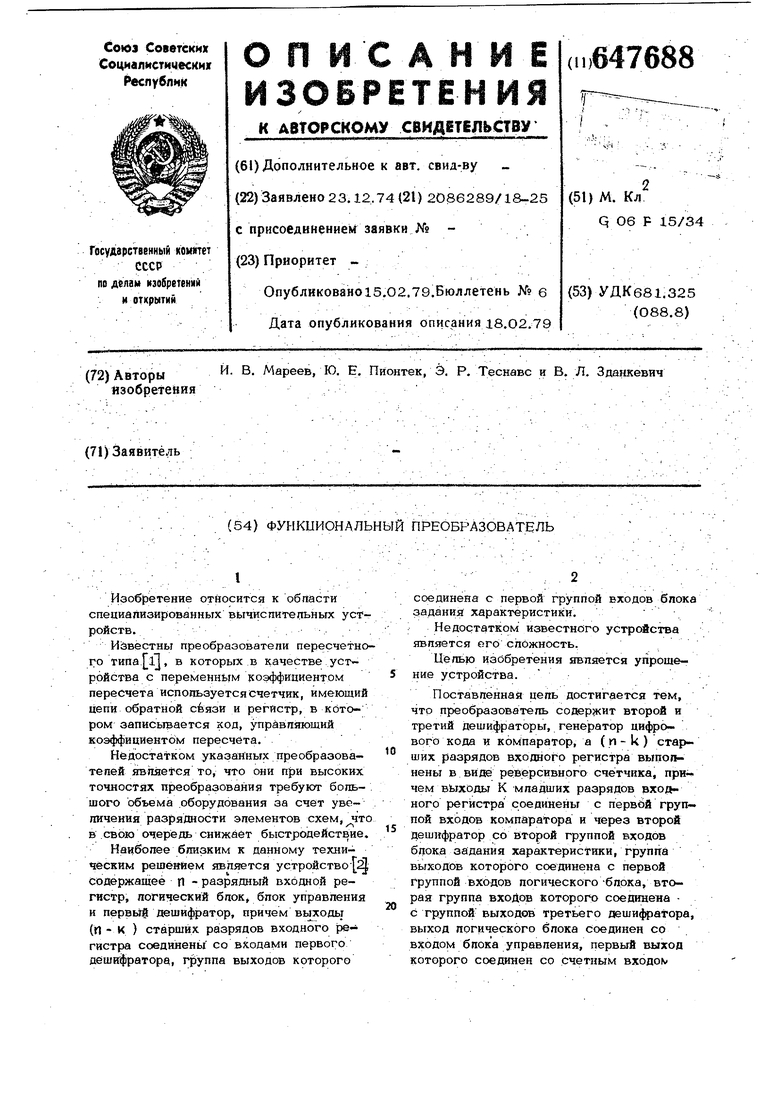

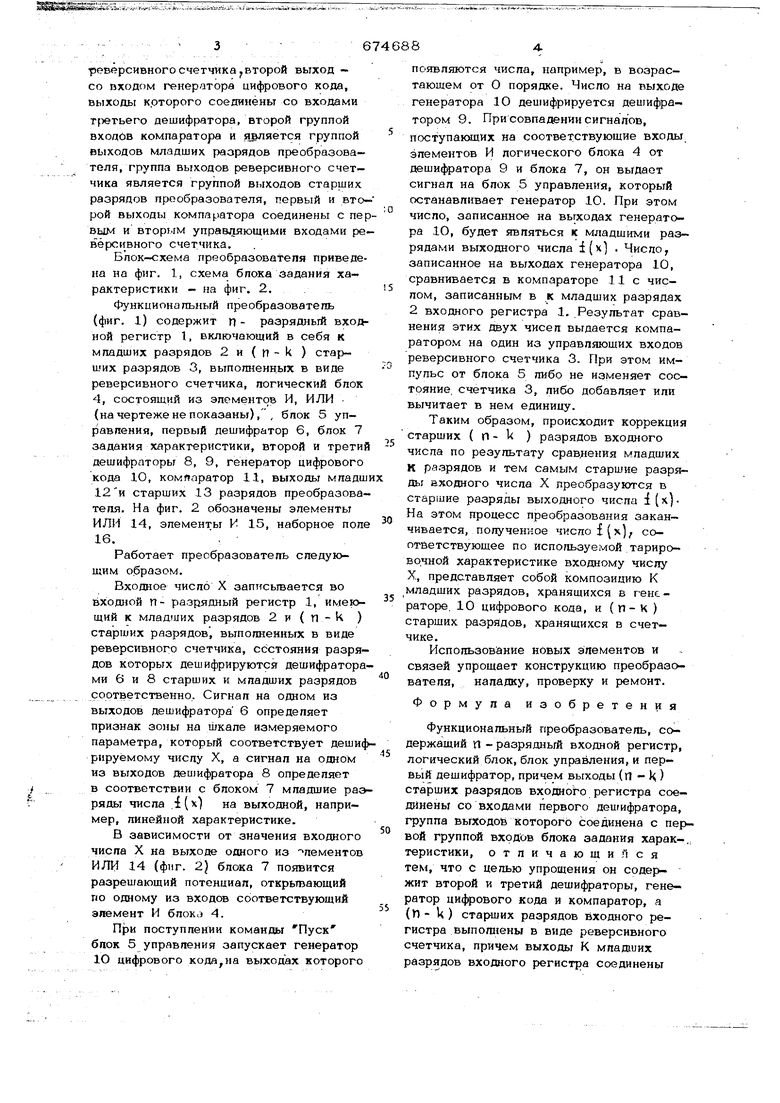

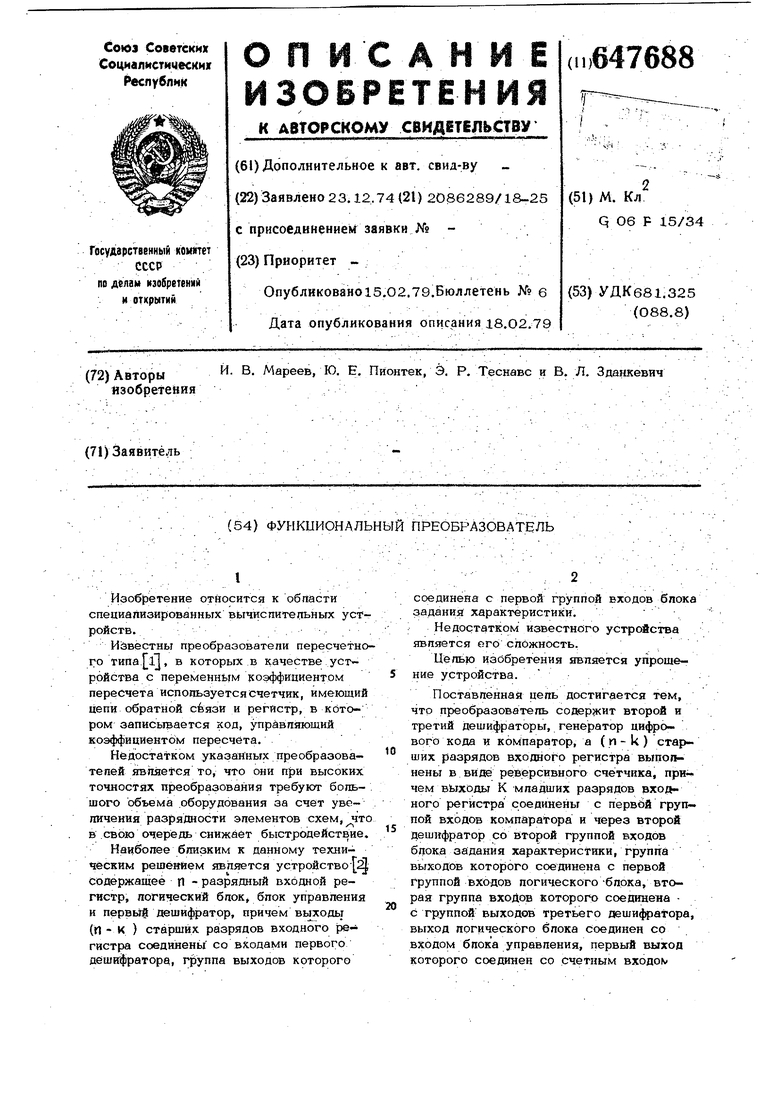

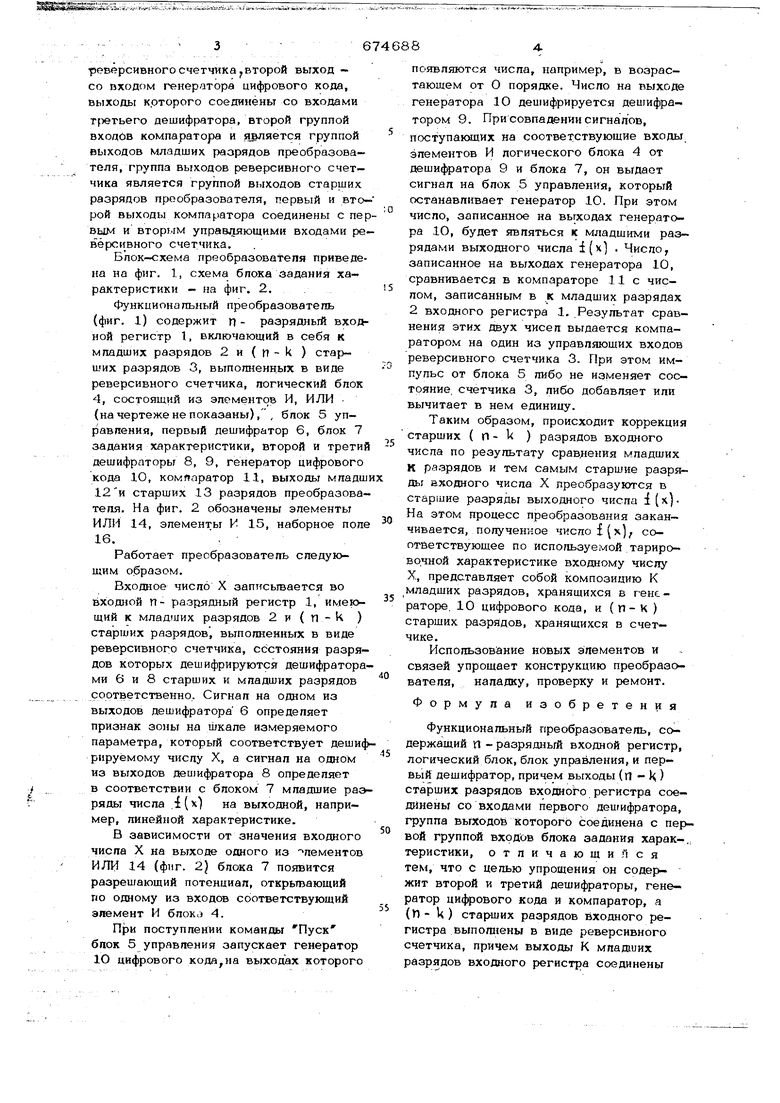

Поставленная цель достигается тем, что преобразователь содержит второй и третий дешифраторы, генератор цифрового кода и компаратор, а ( п - k ) старших разрядов вхошого регистра выполнены в виде реверсивного счётчика, причем вьгходы К младших разрядов входного регистра соединены с первЬй группой входов компаратора и через второй дешифргатор со второй группой входов блока задания характеристики, группа выходов которого соединена с первой Группой входов логического-блока, вторая группа входов которого соединена С труппой выходов третьего деши4чратора выход логического блока Соединен со входом блока управления, первый выход которого соединен со счетным входокреверсивного счетчика второй выход - со входом генератора цифрового кода, выходы которого соединены со входами Т{5егьего дешифратора, второй группой входов компаратора и является группой выходов младших разрядов преобразователя, труппа выходов реверсивного счетчика является группой выходов старших разрядов прообразователя, первый и вто- рой выходы компаратора соединены с пер вым и вторым управляющими входами ре вёрси вного счетчика. Бпок-схема преобразователя приведена на фиг. 1, схема блока задания характеристики - на фиг. 2. Функциональный преобразователь (фиг. 1) содержит П- разрядный входной регистр 1, включающий в себя к младших разрядов 2 и ( ц - k ) старших разрядов 3, выполненных в виде реверсивного счетчика, логический блок 4, состоящий из элементов И, ИЛИ (начертеже не показаны), , блок 5 управления, первый дешифратор 6, блок 7 задания характеристики, второй и третий дешифраторы 8, 9, генератор цифрового кода 10, компаратор И, выходы младш 12и старших 13 разрядов преобразователя. На фиг. 2 обозначены элементы ИЛИ 14, элементы И 15, наборное поле 16. . Работает преобразователь следук щим образом. Входное число X запттсьгоается во входной П- разрядный регистр 1, к младших разрядов 2 и ( п -К ) старших разрядов , выполненных в виде реверсивного счетчика, состояния разрядов которых дешифрируются дешифратора ми 6 и 8 старших и младших разрядов соответственно. Сигнал на одном из выходов дешифратора 6 определяет признак зоны на шкапе измеряемого параметра, который соответствует дешиф рируемому числу X, а сигнал на одном из выходов деишфратора 8 определяет в соответствии с блоком 7 младшие раэ ряды числа ,i(x) на выходной, например, линейной характеристике. В зависимости от значения входного числа X на выходе одного из лементов ИЛИ 14 (фиг. 2) блока 7 появится разрешающий потенциал, открьтающий по одному из входов соответствующий элемент И блока 4. Щрк поступлении команды Пуск блок 5 управления запускает генератор Ю цифрового кода,на выходах которого

674688 пояпвпяются числа, например, в возрастающем от О порядке. Число на выходе генератора Ю дешифрируется дешифратором 9. При совпадении сигналов, поступакяцих на соответствующие входы элементов И логического блока 4 от дешифратора 9 и блока 7, он выдаст сигнал на блок 5 управления, который останавливает генератор 10. При этом число, записанное на выходах генератора 10, будет являться к младшими разрядами выходного числа i(4 . Число, записанное на выходах генератора 10, сравнивается в компараторе 11 с числом, записанным в к младших разрядах 2 входного регистра 1..Результат сравнения этих двух чисел выдается компаратором на один из управляющих входов реверсивного счетчика 3. При этом импупьс от блока 5 либо не изменяет состояние, счетчика 3, либо добавляет или вычитает в нем единицу. Таким образом, происходит коррекция старших ( П - U ) разрядов входного числа по результату сравнения младших К ра.эрядов и тем самым старшие разрядь входного числа X преобразуются в старшие разряды выходного числа 1(ч)На этом процесс преобразования заканчивается, полученное 4Kcnof( соответствующее по используемой тариро- вочной характеристике входному числу Х, представляет собой композицию К младших разрядов, хранящихся в генераторе. 10 цифрового кода, и ( П- К ) старших разря;дов, хранящихся в счетчике. Использование новых элементов и связей упрощает конструкцию преобразователя, наладку, проверку и ремонт. Формула изобретения Функциональный преобразователь, содержащий п разрядный входной регистр, логический блок, блок управления, и первый дешифратор, причем выходы (п - К ) старших разрядов входного регистра соединены со входами первого дешифратора, группа выходов которого соединена с первой группой входов блока задания харак-.; теристики, отличающийся тем, что с цепью упрощения он содержит второй и третий дешифраторы, генератор ци4 1ового кода и компаратор, а (П- k) старших разрядов входного регистра выполнены в виде реверсивного счетчика, причем выходы К млаД1иих разрядов входного регистра соединены с первой группой входов компаратора и через второй дешифратор со второй груп пой входов блока задания характеристики, группа выходов которого соединена с первой группой.входов логичес кого блока, вторая группа входов которого соединена с группой выходов треть го дешифратора, выход логического блок соединен со входом блока управления, первый выход которого соединен со счетным входом реверсивного счетчика, второй выход - со входом генератора цифрового кода, выходы которого соединены со входами третьего дешифратора, второй группой входов компаратора Вых и 5ШЛяетСЯ группой выходив ;паД1ИИХ разрядов преобразователя, группа выходов реверсивного счетчика является группой выходов старших разрядов преобразователя, первый и второй выходы компаратора соединены соответственно с первым и вторым управляющими входами реверсивного счетчика. Источники информации, принятые во внимание при экспертизе1. Авторское свидетельство СССР №372708, кл. Q 06 q 7/26, 1971. 2; Авторское свидетельство СССР №369589, кл. q 06 i 1/02, J.971. - L V

fffff

иг.г -f-r

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Способ интегрального преобразования релаксационных сигналов и устройство для его осуществления | 1986 |

|

SU1695324A1 |

| Устройство для регулирования расходажидКОСТи | 1979 |

|

SU842728A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| УСТРОЙСТВО ДЛЯ ГЕНЕРАЦИИ КОДА ПОСТОЯННОГО ВЕСА | 1969 |

|

SU238886A1 |

Авторы

Даты

1979-02-15—Публикация

1974-12-23—Подача