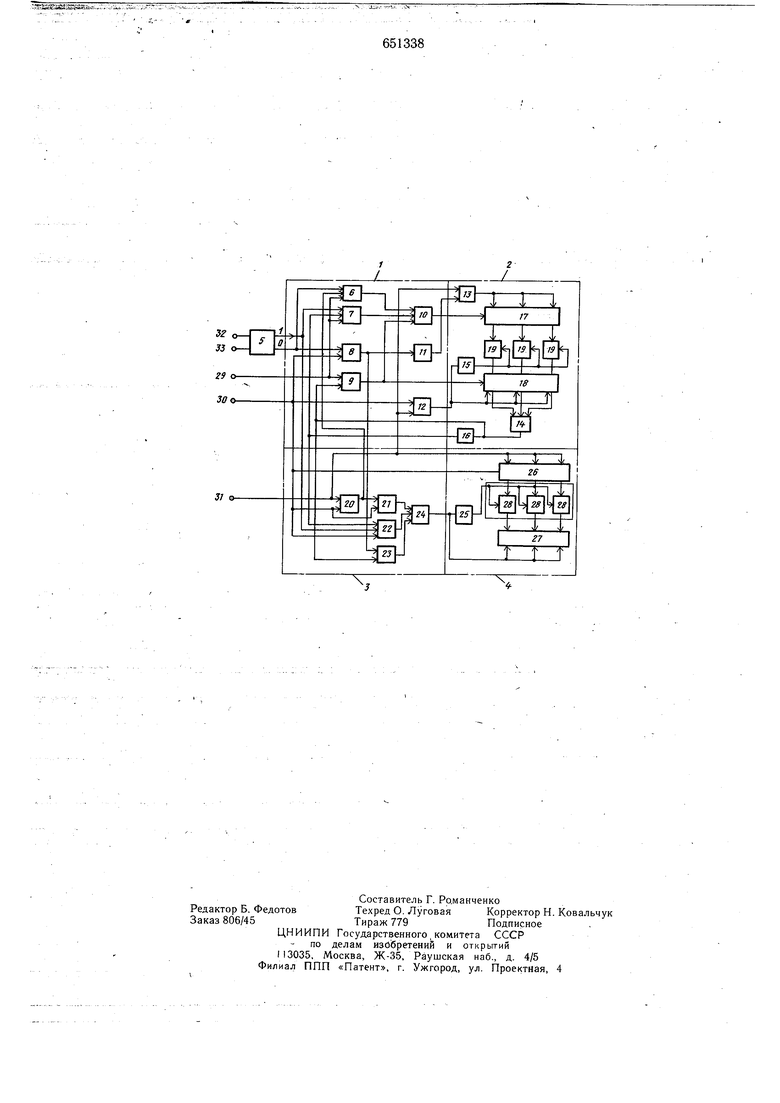

HE, вход которого подключен ко второму , входу третьего элемента И и первому входу седьмого элемента И, второй вход которого соединен с выходом четвертого элемента И и через второй элемент задержки - со вторым входом первого элемента ИЛИ. Выходы первого, второго и третьего элементов И через четвертый элемент ИЛИ подключены ко второму входу первого регистра, второй и третий входы второго регистра соединены соответственно с выходами третьих элементов ИЛИ и И, выходы третьего регистра через вторую группу элементов И подключены к первым входам четвертого регистра, ко вторым входам которого через пятый элемент ИЛИ подсоединены выходы пятого, , шестого и седьмого элементов И. Выход пятого элемента ИЛИ -через третий элемент задержки соединен со вторым входом второй группы элементов И. На чертеже представлена функциональная схема устройства. Устройство состоит из блока ввода чисел 1, блока 2 определения экстремальных значений чисел, блока формирования сигналов 3, блока 4 определения номеров чисел. Блок 1 содержит триггер 5, элементы И 6-9, элемент ИЛИ 10, элемент задержки 11, элемент ИЛИ 12, блок 2 - элементы ИЛИ 13, 14, элемент задержки 15, элемент НЕ 16, регистры 17, 18, группу элементов И 19. В блок 3 входят триггер 20, элементы И 21 - 23, элемент ИЛИ 24, в блок 4 - элемент задержки 25, регистры 26, 27, группы элементов И 28. Устройство работает следующим обраПоследовательность множества импульсно кодированных чисел поступает на вход 29 устройства. Импульсы сброса (между серией импульсов) поступают на вход 30. В начале процесса выбора регистры 17, 18 устанавливаются в нулевое состояние через - элементы ИЛИ 12, 13 и регистр 26. В блоке фор яирования сигналов 3 триггер 20 устанавливается в единицу по входу 31. При выборе числа с минимальным значением триггер 5 устанавливается в нулевое состояние по входу 33. Уровень «нуль выхода триггера 5 поступает на разрешающие входы элементов И 6 и 9. Серии импульсов первого числа из множества чисел, поступающих на вход 29, с помощью разрещающих уровней «единица с выхода триггера 20 и «нуль с выхода триггера 5 прохоДят через элемент И 6 и элемент ИЛИ 10 и заносятся в регистр 17 по второму (суммирующему) входу. Первый импульс сброса, поступающий на вход 30 устройства, добавляет единицу в регистр 26, устанавливает в нулевое состояние регистр 27 и заносит содержимое регистра 26 в регистр 27 через элемент ИЛИ 24, группу элементов И 28 и элемент задержки 25 импульсом длительностью нсек с элемента И 21 с раз651338решения триггера 20; устанавливает в нуль триггер 20; устанавливает в нуль регистр 18 через элемент ИЛИ 12; заносит содержимое регистра 17 в реУистр 18 через элемент задержки 15 и группу элементов И 19; устанавливает в нуль регистр 17 через элемент И 9, элемент ИЛИ 13, и элемент задержки 11 При поступлении на вход 29 устройства серии импульсов следующего числа сигнал с регистра 18 через элемент ИЛИ 10 разрешает ей пройти на третий (вычитающий) вход регистра 18 через элемент И 8 (вь1пол-у пяется операция вычитания из содержимо-. го регистра 18) и на суммирующий вход регистра 17 через элемент ИЛИ 10. В процессе вычитания, если содержимое регистра 18 равняется нулю (предыдущее число меньше, чем данное), прекращается вычитание в этом регистре и сложение в регистре 17 низким уровнем сигнала с элемента ИЛИ 14 через элемент И 8 и элемент ИЛИ 10. Поступающий на вход 30 устройства следующий импульс добавляют единицу.в регистр 26 по первому (суммирующему) входу; гасит регистр 18 через элемент ИЛИ 12; заносит содержимое регистра 17 в регистр 18 через элементь задержки 15 и 11; устанавливает в нулевое состояние регистр 17 через элемент И 9, элемент ИЛИ 13 и элемент задержки 11. В результате вычитания, если содержимое регистра 18 не равняется нулю (предыдущее число больше данного), то поступающий на вход 30 устройства следующий импульс сброса добавляет единицу в регистр 26 заносит содержимое этого регистра в регистр 27 через элемент И 23, элемент ИЛИ 24, группу элементов И 28 и элемент задержки 25 с предварительным гащением регистра 27; гасит регистр 18 сигналом с элемента ИЛИ 12 и заносит содержимое регистра 17 в регистр 18 через элементы задержки 15 и 11; устанавливает в нуль регистр 17 через элемент И 9, элемент ИЛИ 13 и элемент задержки 11. Приведенные последовательности операций повторяются при поступлении серии импульсов следующего числа и импульса сброса.,, При выборе числа с максимальным значением триггер 5 устанавливается в единицу по входу 32 устройства. Единичный уровень триггера 5 является разрешающим при выборе максимума и поступает на вторые входы элементов И 7 и 22. В начале выбора максимума регистры 17 и 18 устанавливаются в нулевое состояние через элементы ИЛИ 13 и 12 и регистр 26, а в блоке формирования сигналов 3 триггер 20 устанавливается в единицу по входу 31 устройства. Поступающий на вход 30 первый импульс сбороса добавляет единицу в регистр 26, заносит его содержимое в регистр 27 через элемент ИЛИ 24, группу элементов И 28 и элемент задержки 25 импульсом длительностью нсек с элемента И 21, сформированным триггером 20 и элементом И 21; устанавливает в нуль триггер 20; гасит регистр 18 через элемент ИЛИ 12 и заносит содержимое регистра 17 в регистр 18 через элемент задержки 15 и групну элементов И 19.. Поступаюи1,ая на вход 29 устройства серия импульсов следующего числа из множества чисел направляется разрешающим сигналом с элемента ИЛИ 14 на вычитающий вход регистра 18 через элемент И 8 и уменьшает содержимое этого регистра. В результате вычитания, если содержимое регистра 18 равняется нулю (предыдущее число меньще данного), нулево,е состояние этого регистра через элемент ИЛИ 14 запрещает поступление следующих импульсов кода данного числа на вычитающий вход регистра 18, а через элемент НЕ 16 разрещает им поступить на суммирующий вход регистра 17 через элемент И 7 и элемент ИЛИ 10, в результате чего увеличивается содержимое регистра 17. Поступающий на вход 30 устройства следующий импульс сброса добавляет единицу в регистр 26; гасит регистр 18 через элемент ИЛИ 12 и заносит содержимое регистра 17 в регистр 18 через элемент задержки 15 и группу элементов И 19; гасит регистр 27 через элемент И 22 и элемент ИЛИ 24 и зайосит содержимое регистра 26 в регистр 27 через группу элементов И 28 и элемент задержки 25 разрещающим уровнем «единица с триггера 5 и разрешающим сигналом с элемента НЕ 16. ПривехТ,енные последовательности операций повторяются при поступлении на вход 29 устройства серии импульсов пЪследующих чисел, н результаты выбора и формирования запоминаются в регистрах 18, 26 и 27 соответственно. В результате вычитания, если содержимое регистра 18 не равняется нулю (предыдущее число больще, чем данное), поступающий на вход 30 следующий импульс сброса добавляет единицу в регистр 26, гасит регистр 18 через элемент ИЛИ 12 и заносит содержимое регистра 17 в регистр 18 через элемент задержки 15 и группу элементов И 19. Приведенные последовательности.операций повторяются при поступлении на входы 29 и 30 устройства последующих импульсов. Результаты запоминаются в регистрах 18. 26 и 27. Описанное устройство позволяет не только выбирать экстремум чисел, но и определять порядковый номер числа с экстремальным значением и количество чисел в последовательности чисел. Формула изобретения Устройство для сравнения импульсно кодированных чисел, содержащее первый регистр, первые входы которого соединены с выход,ом первого элемента ИЛИ, а выходы через первую группу элементов И - с первыми входами второго регистра, выходы которого через второй элемент ИЛИ подключены ко входу элемента НЕ, и первый элемент задержки, вход которого соединен со вторыми входами второго регистра, а выход - со вторым входом первой группы элементов И, отличающееся тем, что, с целью расщирения его функциональных возможностей, в него введены дополнительно три элемента ИЛИ, два элемента задержки, два триггера, вторая группа элементов И, два регистра и семь элементов И, к первым входам первого, второго и третьего элементов И подключен первый вход устройства, второй его вход соединен с первыми входами четвертого элемента И, третьего элемента ИЛИ, третьего регистра, первого триггера, пятого и шестого элементов И, третий вход устройства подключен ко вторым входам первого триггера, третьего элемента ИЛИ, третьего регистра и первому входу первого элемента ИЛИ, четвертый и пятый входы устройства соединены соответственно с первым и вторым входами второго триггера, первый.выход которого соединен со вторыми входами второго и щестого элементов И, а второй выход - со вторыми входами первого и четвертого элементов И, к третьему входу первого элемента И и второму входу пятого элемента И подключен выход первого триггера, третьи входы второго и шестого элементов И соединены с вых.одом элемента НЕ, вход которого подключен ко второму входу третьего элемента И и первому входу седьмого элемента И, второй вход которого соединен с выходом четвертого элемента И и через второй элемент задержки - со вторь1м входом первого элемента ИЛИ, выходы первого, второго и третьего элементов И через четвертый элемент ИЛИ подключены ко второму входу первого регистра, второй и третий входы второго регистра соединены соответственно с выходами третьих элемен тов ИЛИ и И, выходы третьего регистра через вторую группу элементов И подключек первым входам четвертого регистра, ны вторым входам которого через пятый элемент ИЛИ подсоединены выходы пятого, щестого и седьмого элементов И, выход пятого элемента ИЛИ через третий элемент задержки соединен со вторым входом второй группы элементов И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 275869, G 06 F 7/02, 15.07.68. 2.Авторское свидетельство СССР № 256363, G 06 F 7/02, 12.08.68.

651338

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU220631A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Устройство для сортировки чисел | 1981 |

|

SU1024903A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для сравнения чисел | 1981 |

|

SU993247A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

J/ о

Авторы

Даты

1979-03-05—Публикация

1976-07-07—Подача