1

Изобретение относится к вычислительной технике.

Известен аналого-цифровой преобразователь, содержащий устройство сравнения, преобразователь кода в напряжение, регистр и логический блок t1}.

Однако устройство имеет большое время преобразования.

Известен аналого-цифровой преобразователь, содержащий устройство С15авнения, вход которого соединен с выходом преобразователя кода в напряжение, выход соединен с первым входом блока логики, второй вход которого соединен с выходом генератора Тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ и распределителя, а третий вход б.г1ока логик соединен с вторыми входами элемента ИЛИ ц распределителя 2,

Однако время преобразования устройства велико,

С целью уменьшения времени.преобразования в аналого-цифровой преобразователь, содержащий устройство сравнения, преобразователь кода в напряжение, блок логики, генератор тактовых импульсов, элемент ИЛИ

и распределитель,введены п основных двоично-десятичных счетчиков, п блоков управления, п коммутаторов и дополнительный двоично-десятичный С етчик, причем выход устройства сравнекия соединен с первым входом блока логики, второй вход которого соединен с вькодом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ и распределителя, а второй, третий иЧетвертый выходы блока логики соединены соответственно с входами дополнительного ДвоичSно-десятичного счетчика и входами п блоков управления, выходи которых соединены с соответствующими входами л основных двоично-десятичных счетчиков, их выходы соединены с первыми входами п коммутаторов, вторые входы которых соединены с выходом дополнительного двоичиодесятичного счетчика, а выходы сое динены с соответствующими

5 п преобра ;ователя .кода -в напряхение, выход элемента ИЛИ соединен с входом установки в нуль дополнительного двоично-десятичного счетчика, шин Яапуск соединена с вторым

0 входом элемента ИЛИ, и с входом

YCtSntisKW в нуль основ ных двоич но ДёсГЯ й н ах счетчиков, управ ляющие аьйоды распределителя соединены соответственно с управляющими входами п коммутаторов и п блоков управления.

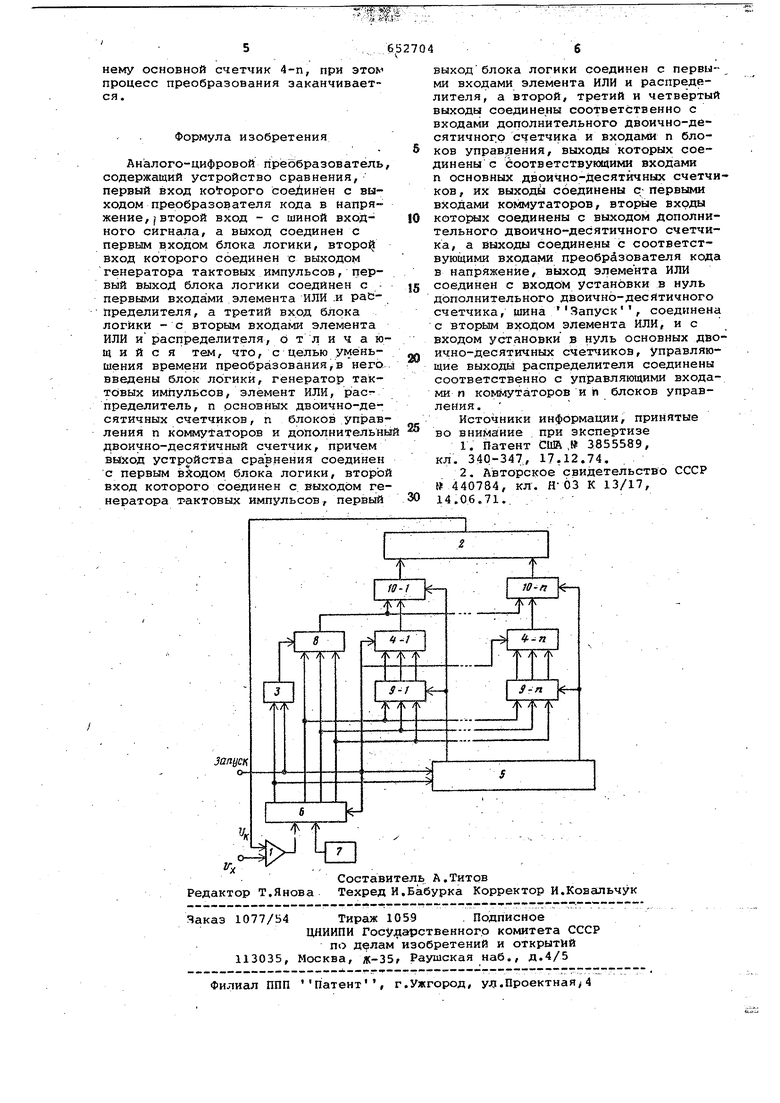

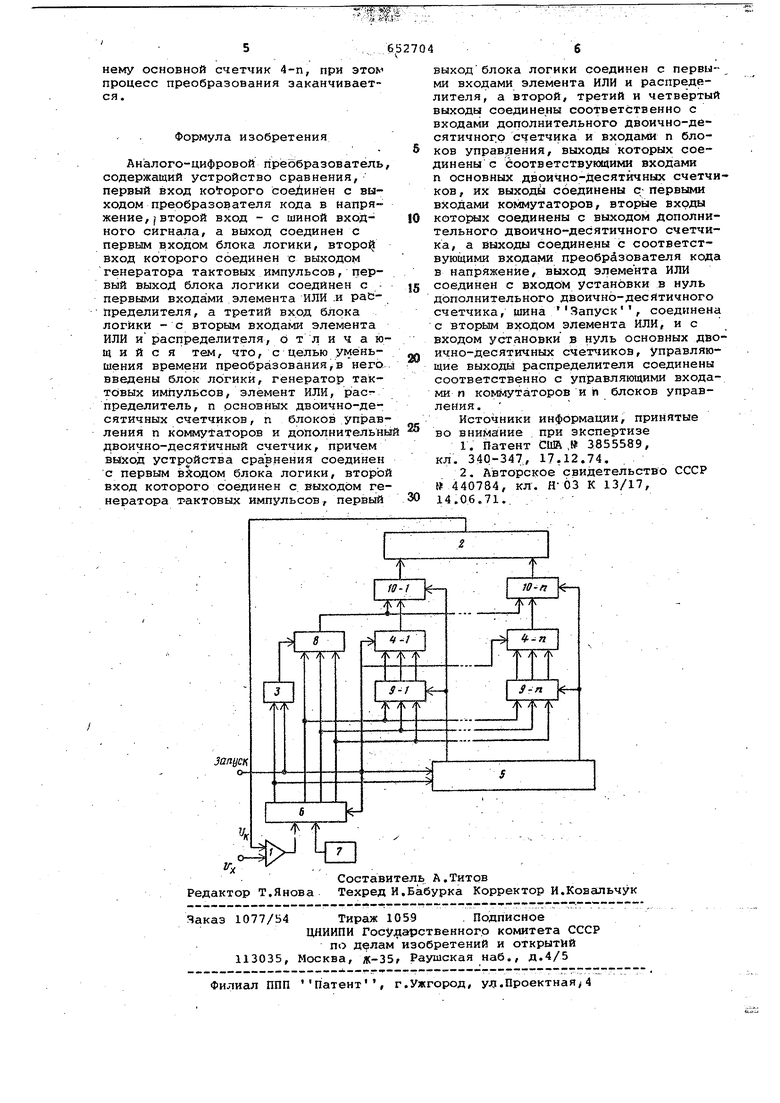

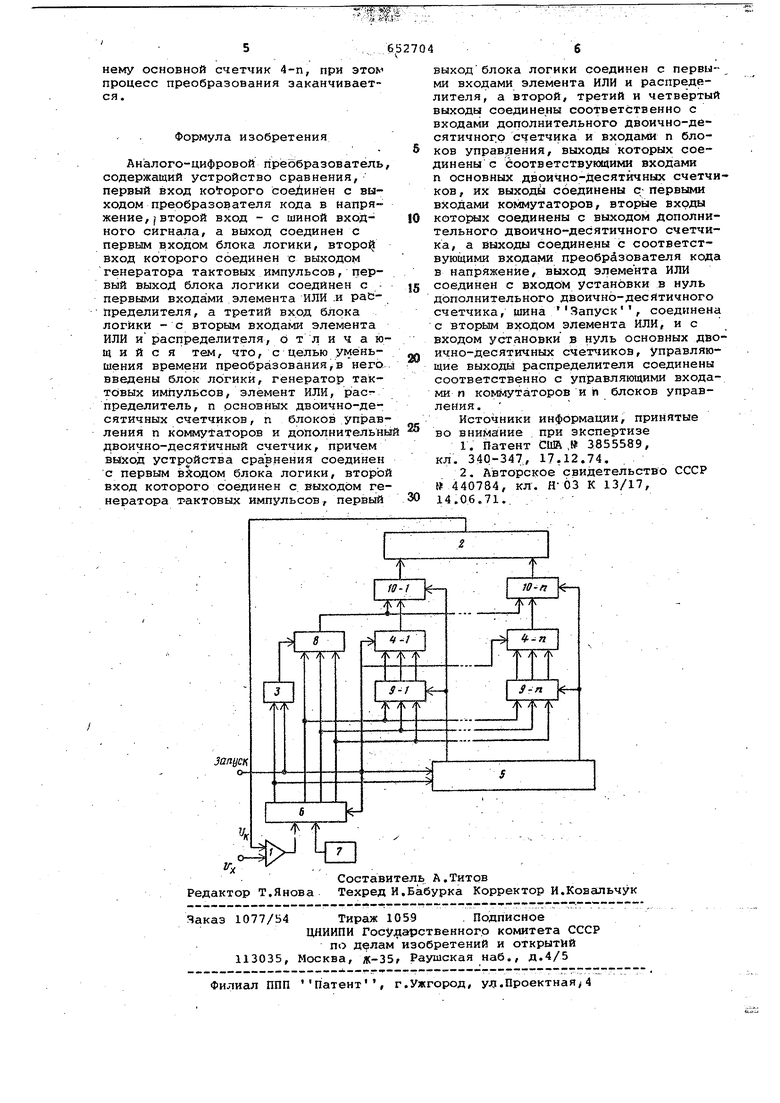

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Аналого-цифровой преобразователь содержит устройство 1 сравнения, преобразователь 2 кода в напряжение, элемент ИЛИ 3, п основных двоичнодесятичных : счетчиков 4-1 - 4-п распределитель 5, блок 6. логики, Генератор 7 тактовых импульсов, дополнительный двоично-десятичный счетчик 8, п блоков 9-1-9-п управления и п коммутаторов. Выход основных бчетчиков 4-1-4-п является выходом устройства.

Преобразование напряжения Ux начинается с установки в нуль сиг- . Налом Запуск дополнительнргрсчетчика 8 и основных счетчиков 4-1-4-п, а распредбшителя 5 и лЪка б логики висходное состояние, в

Жбйбдйой соЬтояййй с распределителя 5 на коммутатор 10 и на блок 9-1 поступает сигнал,который подключает дополнительный счетчик 8 вместо старшей декады основного счетчика 4 и разрешает поступать через блок 9-1. сигналам, формируемым блоком 6, на выходы отключенного счетчика 4-1.

С приходом первого тактового импульса с генератора 7 в блок б на втором,выходе блока 6 формируется, сигнал устанЬвки в основном двоично-десятичном счетчике 4-1 через блок 9-1 управления числа 4 (0100) , а в счетчике 8 - числа 5 (0101),.в результате которого с выхода преобразователя 2 на вход устройства1

поступает компенсирующее напряжение (JK , равное I-OK, где Оц максимальное напряжение компенсации, при этом, если величина компенсирующего напряжения UK окажется преобразуемого сигнала Ux , т.е J-i-u.M U /, о с выхода устройства 1 на первый управляю1сий вход блока б поступает сигнал Превышения.

С Приходом второго тактового импульса с генератора 7 в блок 6 на третьем выходе блока б формируется сигнал установки в основном двоично-десятичном счетчике .4-1 через блок 9-1 числа О (0000), а В дополнительном счетчике 8-числа 1 (0001), в результатечего на соответствующий вход преобразователя 2 через коммутатор 10-1 поступает цифровая информация числа , а с его выхода на второй входустройства 1 сравнения - компенсирующее напряжение U , равное 10 1к.м, при этом, если величина компенсирующего напряжения станет меньше пре10 и«„ х

образуемого, т.е. , то с выхода устройства 1 сра1;ейия на первый управляющий вход блок.ч 6 поступает сигнал Недокомпенсации, при наличии которого .с четвёртого выхода блока 6 на счетный вход основного двоично-десятичного счетчика 4-1 через блок 9-1 и на счетный вход счетчика 8 начинают поступать тактовые импульсы, в результате которых компенсирую14ее напряжение на выходе преобразователя 2 начинает увеличиваться от , если

Т-ик.,илй от|-и .,если i-U.Ux с квантования, равным 10 и .

Как толькЬ напряжение компенсации Охстанет больше преобразуемого Ux т.е. UK Ц(, с устройства 1 на первый управляющий вход блока б поступает сигнал Превышения, в результате которого с первого .выхода блока 6 на входе установки нуля счетчика 8 через элемент ИЛИ 3 поступает сигнал Установки в нуль, а-на управляющий входраспределителя 5 - сигнал, в результате которого он переходит в очередное состояние, при этом дополнительный двоично-десятичный счетчик 8 подключается вместо очередной декады основного двоичнодесятичного счетчика 4-2, а старшая декада основного двоично-десятичного счетчика 4-1, через коммутатор 10-1к соответствующему, входу преобразователя 2.

Так как в старшей декаде счетчика 4-1 записывается число, на единицу меньше числа, которое записывается в счетчике 8, то при подключении выхода старшей декады счетчика 4-1 через коммутатор 10-1 к соответствующему входу преобразователя 2 напряжение компенсации Кц на его выходе уменьшается на величину шага кВантования этой декады, равному .M вследствие чего компенсирующее на41ряжение UK станет-меньше иаи рйвно преобразуемому Ux , т.e. где А( - число, записанное в старшей декаде основного двоично-десятичного счетчика 4-1.

Если напряжение компенсации U меньше преобразуемого, то с выхода устройства на первый управляющий вход блока б поступает сигнал Недокрмпенсации|, при котором блок б устанавливается в исходное состояние после чего начинается цикл обработки очередной декады. , .

Обработка очередной и последующих декад основных счетчиков 4-2 4-п производится в той же последовательности, что и обработка старшей декады. . .

После обработки п-ной декады распределитель 5 отключает счетчик 8 от коммутатора 10-п, подключив к

нему основной счетчик 4-п, при этo процесс преобразования заканчивается.

Формула изобретения

Аналого-цифровой преобразователь содержащий устройство сравнения, первый вход которого соеЛинен с выходом преобразователя кода в напряжение, / второй вход - с шиной входного сигнала, а выход соединен с первым входом блока логики, втрро вход которого соединен с выходом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ .и распределителя, а третий вход блока логики - с вторым входами элемента ИЛИ и распределителя, о т л и ч а ющ и и с я тем, что, с Целью уменьшения времени преобразования в него введены блок логики, генератор тактовых импульсов, элемент ИЛИ, рас пределитель, п основных двоично-десятичных счетчиков, п блоков управления п коммутаторов и дополнительны двоично-десятичный счетчик, причем выход устройства сравнения соединен с первым входом блока логики, второй вход которого соединен с. выходом генератора Тактовых импульсов, первый

б

выходблока логики соединен с первыми входами элемента ИЛИ и распределителя, а второй, третий и четвертый выходы соединены соответственно с входами дополнительного двоично-десятичного счетчика и входами п блоков управ тення, выходы которых соединены с Соответствующими входами п основных двоично-десятичных счетчиков , их выходы соединены с- первыми входами коммутаторов, вторые входы

0 которых соединены с выходом дополнительного двоично-десятичного счетчика, а выходы соединены с соответствующими входами преобразователя кола в напряжение, выход элемента ИЛИ соединен с входом установки в нуль

5 дополнительного двоично-десятичного счетчика, шина Запуск, соединена с вторым входом элемента ИЛИ, и с входом установки в нуль основных двоично-десятичных счет 1иков, управляющие выходи распределителя соединены соответственно с управляющими входами п коммутаторов и п блоков управления.

Источники информации, принятые

5 во внимание при экспертизе

Г. Патент США, 3855589, кл. 340-347., 17.12.74.

2. Авторское свидетельство СССР 440784, кл. Я-03 К 13/17, 14.06.7.. .

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых величин | 1987 |

|

SU1476616A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU243281A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

Авторы

Даты

1979-03-15—Публикация

1976-01-23—Подача