1

Изобретение касается импульсной техники, а именно счетчиков цифровых вычислительных устройств.

Известен двоичный счетчик импульсов, содержащий триггеры с входными логическими элементами, выходы которых соединены с входами триггеров, блок сквозного переноса, состоящий из последовательно включенных логических элементов . Выходы логических элементов И-НЕ блока сквозного переноса соединены с входами входных логических элементов разрядов счетчика. В блоке сквозного переноса формируется прямое и инверсное значение сигнала переноса в каждый разряд счетчика 1.

Однако этот двоичный счетчик не обеспечивает необходимого быстродействия и имеет сложный блок сквозного переноса.

Известен также двоичный счетчик импульсов, содержащий триггеры с входными логическими элементами 2И-ИЛИ-НЕ, выходы которых соединены с входами триггеров, блок сквозного переноса, состоящий из последовательно включенных логических элементов 2И-ИЛИ-НЕ и И--НЕ. Выходы логических элементов 2И-ИЛИ-НЕ блока

СКВОЗНОГО переноса соединены с входами входных логических элементов 2И-ИЛИ- -НЕ четных разрядов счетчика. Счетчик содержит также логический элейент И-НЕ, вход которого соединен с источником сигналов обнуления, а выходы подключены к входам триггеров четных разрядов и входам входных логических элементов 2И-ИЛИ-НЕ нечетных разрядов. Соответствующие выходы триггеров нечетных разрядов соединены с входами логических элементов И-НЕ блока сквозного переноса, а выходы триггеров четных разрядов соединены с входами логических элементов 2И-ИЛИ-НЕ блока сквозного переноса. В блоке сквозного переноса формируется прямое или инверсное значение сигнала переноса в каждый разряд счетчика 2.

Однако схема этого двоичного счетчика импульсов сложна,

Цель изобретения - упрощение счетчика.

Это достигается тем, что в предложенном двоичном счетчике импульсов, содержащем триггеры с входными логическими элементами 2И-ИЛИ-НЕ, выходы которых соединены с входами триггеров, блок сквозного переноса, состоящий из последовательно включенных логических элементов И-НЕ и входного элемента И-НЕ, выходы блока сквозного переноса попарно соединены с первыми и вторыми входами логических элементов 2И-ИЛИ-НЕ нечетных разрядов, шина обнуления через логический элемент И-НЕ подключена к первым и третьим -входам логических элементов 2И-ИЛИ-НЕ четных и нечетных разрядов соответственно, прямой выход триггера каждого разряда соединен с четвертым в нечетном и с вторым в четном входом элемента 2 И-ИЛИ-НЕ данного разряда, инверсный выход триггера нечетных разрядов соединен с пятым входом логического элемента 2И-ИЛИ-НЕ данного разряда, к третьим и четвертым входам логических элементов 2И-ИЛИ-НЕ четных разрядов подключены соответствующие щины инверсного сигнала переноса в последующий разряд, а к пятым .и шестым входам - соответственно шины прямого сигнала переноса в предыдущий разряд и прямой выход триггера предыдущего разряда. В блоке сквозного переноса формируется прямое и инверсное значение сигнала переноса только в нечетные разряды счетчика. В блоке сквозного переноса сложные логические элементы 2И-ИЛИ-НЕ заменены на простые логические элементы И-НЕ, что упрощает схему счетчика.

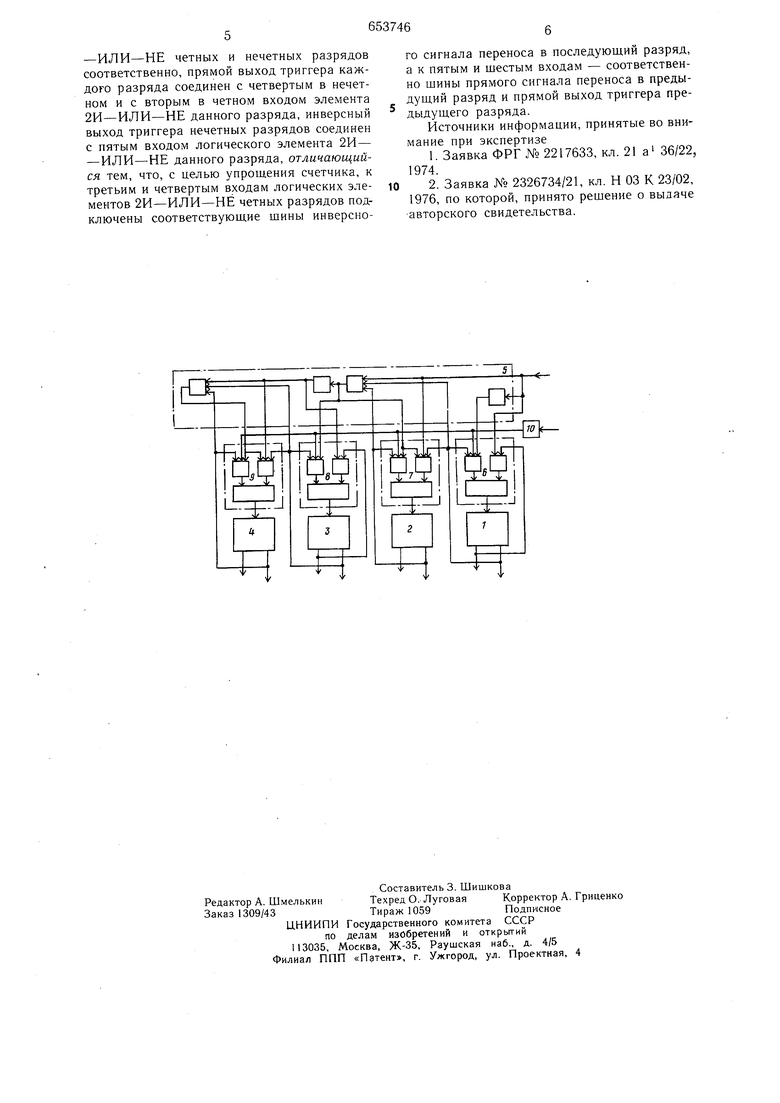

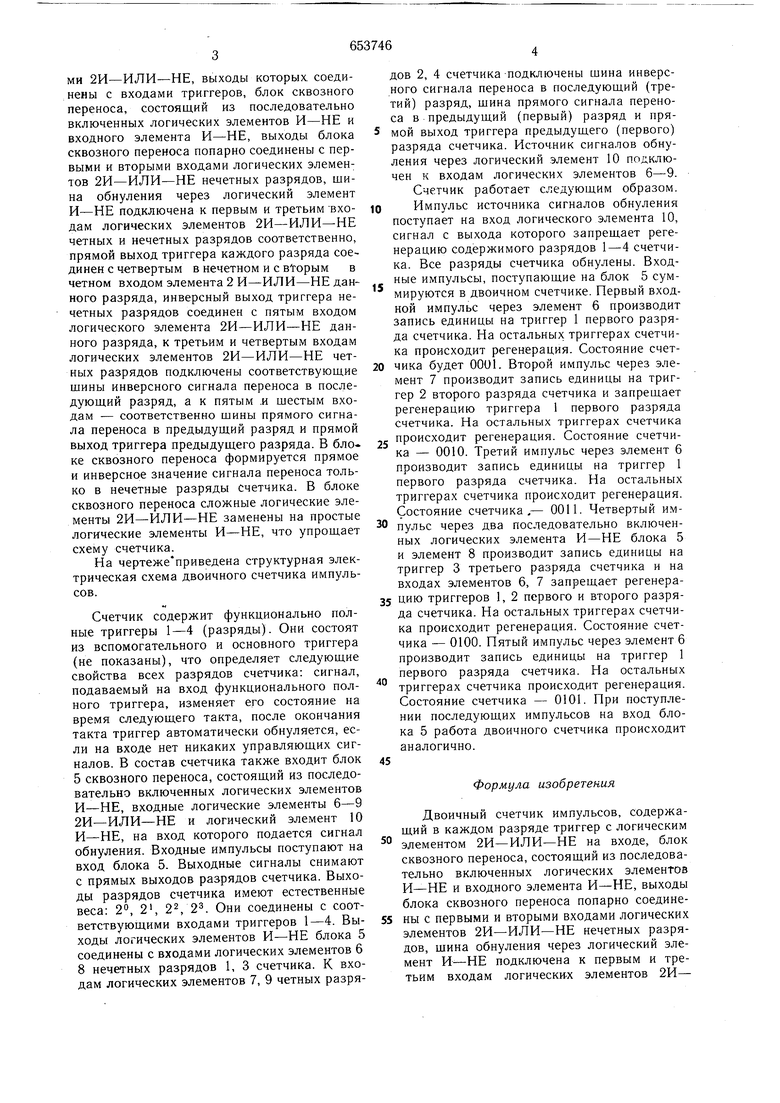

На чертежеприведена структурная электрическая схема двоичного счетчика импульсов.

Счетчик содержит функционально полные триггеры 1-4 (разряды). Они состоят из вспомогательного и основного триггера (не показаны), что определяет следующие свойства всех разрядов счетчика: сигнал, подаваемый на вход функционального полного триггера, изменяет его состояние на время следующего такта, после окончания такта триггер автоматически обнуляется, если на входе нет никаких управляющих сигналов. В состав счетчика также входит блок 5 сквозного переноса, состоящий из последовательно включенных логических элементов И-НЕ, входные логические элементы 6-9 2И-ИЛИ-НЕ и логический элемент 10 И-НЕ, на вход которого подается сигнал обнуления. Входные импульсы поступают на вход блока 5. Выходные сигналы снимают с прямых выходов разрядов счетчика. Выходы разрядов счетчика имеют естественные веса: 2°, 2, 2, 2. Они соединены с соответствующими входами триггеров 1-4. Выходы логических элементов И-НЕ блока 5 соединены с входами логических элементов 6 8 нечетных разрядов 1, 3 счетчика. К входам логических элементов 7, 9 четных разрядов 2, 4 счетчика -подключены шина инверсного сигнала переноса в последующий (третий) разряд, щина прямого сигнала переноса в предыдущий (первый) разряд и прямой выход триггера предыдущего (первого) разряда счетчика. Источ-ник сигналов обнуления через логический элемент 10 подключен к входам логических элементов 6-9. Счетчик работает следующим образом.

Импульс источника сигналов обнуления поступает на вход логического элемента 10, сигнал с выхода которого запрещает регенерацию содержимого разрядов 1-4 счетчика. Все разряды счетчика обнулены. Входные импульсы, поступающие на блок 5 суммируются в двоичном счетчике. Первый входной импульс через элемент 6 производит запись единицы на триггер 1 первого разряда счетчика. На остальных триггерах счетчика происходит регенерация. Состояние счетчика будет 0001. Второй импульс через элемент 7 производит запись единицы на триггер 2 второго разряда счетчика и запрещает регенерацию триггера 1 первого разряда счетчика. На остальных триггерах счетчика

- происходит регенерация. Состояние счетчика - 0010. Третий импульс через элемент 6 производит запись единицы на триггер 1 первого разряда счетчика. На остальных триггерах счетчика происходит регенерация. Состояние счетчика,- ООП. Четвертый импульс через два последовательно включенных логических элемента И-НЕ блока 5 и элемент 8 производит запись единицы на триггер 3 третьего разряда счетчика и на входах элементов 6, 7 запрещает регенерацию триггеров 1, 2 первого и второго разряда счетчика. На остальных триггерах счетчика происходит регенерация. Состояние счетчика - 0100. Пятый импульс через элемент 6 производит запись единицы на триггер 1 первого разряда счетчика. На остальных триггерах счетчика происходит регенерация. Состояние счетчика - 0101. Нри поступлении последующих импульсов на вход блока 5 работа двоичного счетчика происходит аналогично.

Формула изобретения

Двоичный счетчик импульсов, содержащий в каждом разряде триггер с логическим

элементом 2И-ИЛИ-НЕ на входе, блок сквозного переноса, состоящий из последовательно включенных логических элементов И-НЕ и входного элемента И-НЕ, выходы блока сквозного переноса попарно соединены с первыми и вторыми входами логических элементов 2И-ИЛИ-НЕ нечетных разрядов, шина обнуления через логический элемент И--НЕ подключена к первым и третьим входам логически х элементов 2И-

-ИЛИ-НЕ четных и нечетных разрядов соответственно, прямой выход триггера каждого разряда соединен с четвертым в нечетном и с вторым в четном входом элемента 2И-ИЛИ-НЕ данного разряда, инверсный выход триггера нечетных разрядов соединен с пятым входом логического элемента 2И- -ИЛИ-НЕ данного разряда, отличающийся тем, что, с целью упрощения счетчика, к третьим и четвертым входам логических элементов 2И-ИЛИ-НЕ четных разрядов подключены соответствующие шины инверсного сигнала переноса в последующий разряд, а к пятым и шестым входам - соответственно шины прямого сигнала переноса в предыдущий разряд и прямой выход триггера предыдущего разряда.

Источники информации, принятые во внимание при экспертизе

1.Заявка ФРГ № 2217633, кл. 21 а 36/22, 1974.

2.Заявка № 2326734/21, кл. Н 03 К 23/02, 1976, по которой, принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик импульсов | 1976 |

|

SU571913A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Счетчик импульсов с контролем ошибок | 1974 |

|

SU661807A1 |

| КОДЕР БИПЛОСКОСТИ ОРТОГОНАЛЬНЫХ СИГНАЛОВ | 2001 |

|

RU2209509C2 |

| Устройство для подавления дребезга контактов @ выключателей | 1988 |

|

SU1621155A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

Авторы

Даты

1979-03-25—Публикация

1976-11-23—Подача