1

Изобретение относится к импульсной технике.

Известен счетчик импульсов, содержащий триггеры, связанные между собой через логические элементы И и блок контроля работы счетчика, в состав которого входят триггер, многовходовой одновибратор и счетHbie элементы I .

Однако точность работы такого счетчика недостаточна, а контроль за процессом работь невозможен.

Наиболее близким по технической сущности является счетчик, содержащий четыре //С-триггера, логические элементы И, включенные между //C-fpHrrepaMH, блок переноса, состоящий из логических элементов 2И-ИЛИ, между которыми включены логические элементы НЕ, причем входы логических элементов 2И-ИЛИ соединены с выходами соответствующих IK- триггеров, и блок индикации, состоящий из RS-триггера и индикатора 2.

Недостатками этого счетчика являются невысокие надежность и быстродействие.

С целью повышения надежности и быстродействия в счетчик импульсов, содержащий четыре //С-триггера, логические элементы И, включенные между выходами предыдущих и счетными входами последующих //(-триггеров, блок четности, состоящий из трех логических элементов 2И-ИЛИ, между которыми включены логические элементы НЕ, причем входы первого логического элемента 2И-ИЛИ соединены с прямым и инверсным выходами первого и второго /К-триггеров, входы второго логического элемента 2И-ИЛИ - с прямыми и инверсными выходами третьего и четвертого //(-триггеров, входы третьего логического элемента 2И-ИЛИ подключены к выходам предыдущих логических элементов 2И-ИЛИ и логических элементов НЕ блока четности, и блок индикации, состоящий из RS-триггера, выход которого подключен к индикатору, введены блок предсказания четности, состоящий из двух логических элементов 2И-ИЛИ и //(-тр,иггера, и блок отрицания равнозначности, состоящий из инвертора и логического элемента 2И-ИЛИ-НЕ, первый вход которого соединен с выходом -инвертора, второй вход - с прямым входом //(-триггера блока предсказания четности, третий вход - со входом инвертора и выходом третьего из логических элементов 2И-ИЛИ блока четности, четвертый

ВХОД подключен к инверсному выходу /Д-триггера блока предсказания четности, а выход логического элемента 2И-ИЛИ-НЕ соединен с S -входом R S -триггера блока индикации. С-вход //(-триггера блока пред- 5 сказания четности соединен с шиной входного сигнала, R и S-в ходь соединеныс аналогичными входами других //С-триггеров, а I и К-входы соединены с выходом первого логического элемента 2И-НЕ блока нредска- . зания четности, первый вход которого соединен с выходом второго логического элемента 2И-НЕ, первый вход котОрТ)го соединен с прямым выходом второго //С-триггера, второй вход с инверсным выходом третьего //С-триггера, а второй вход первого лОги- is ч ёского элемента 2И-НЕ - с инверсным выходом первого //(-триггера.;

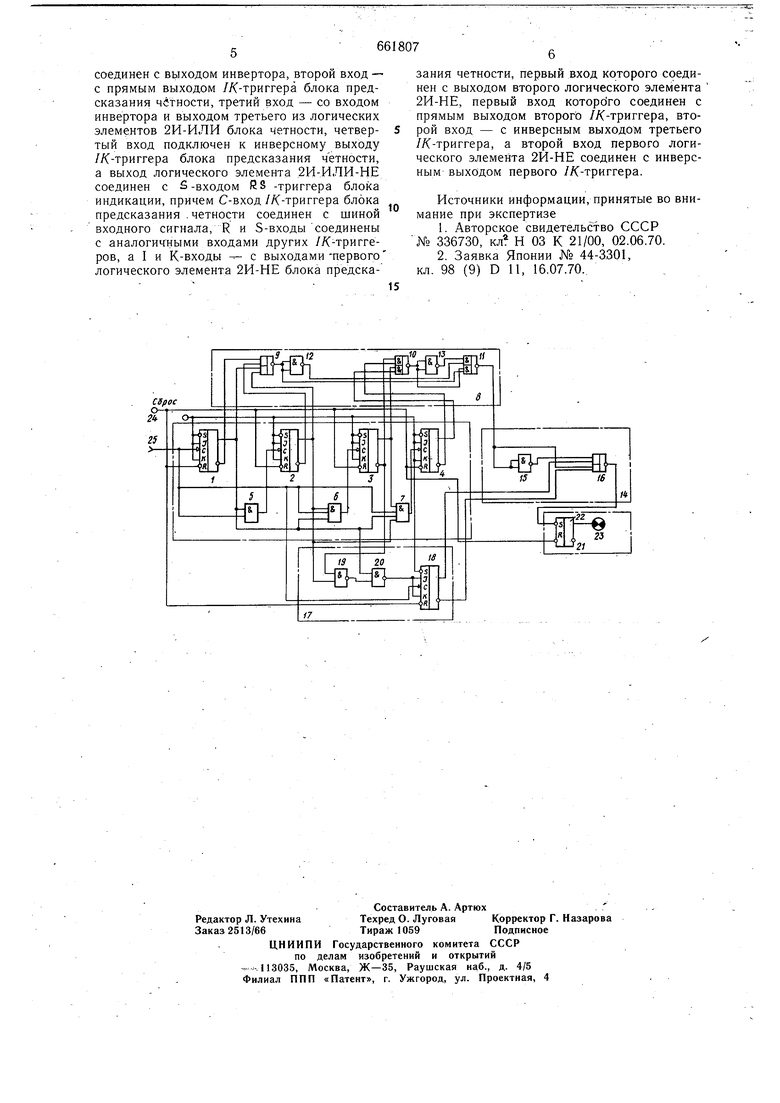

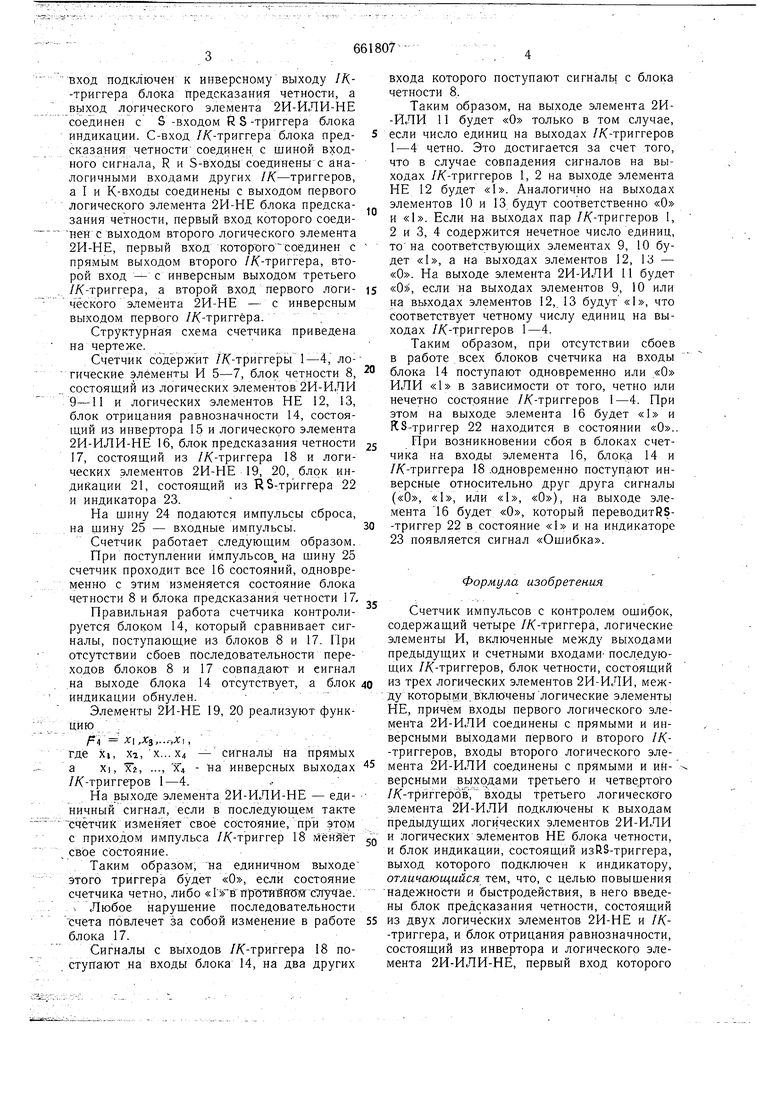

Структурная схема счетчика приведена на чертеже.

Счетчик сод,ёржит //(-триггеры 1-4, ло- гические элементы И 5-7, блок четности 8, состоящий из логических элементов 2И-ИЛИ 9-II и логических элементов НЕ 12, 13, блок отрицания равнозначности 14, состоящий из инвертора 15 и логического элемента 2И-ИЛИ-НЕ 16, блок предсказания четности 25 17, состоящий из //(-триггера 18 и логических элементов 2И-НЕ 19, 20, блок индикации 21, состоящий из RS-триггера 22 и индикатора 23.

На шину 24 подаются импульсы сброса, на щину 25 - входные импульсы.30

Счетчик работает следующим образом.

При поступлении импульсов на щину 25 счетчик проходит все 16 состояний, одновременно с этим изменяется состояние блока четности 8 и блока предсказания четности 17, ,

Правильная работа счетчика контролируется блоком 14, который сравнивает сигналы, поступающие из блоков 8 и 17. При отсутствии сбоев последовательности переходов блоков 8 и 17 совпадают и сигнал на выходе блока 14 отсутствует, а блок 40 индикации обнулен.

Элементы 2И-НЕ 19, 20 реализуют функцию

pit х ,х,..г,х,

где Х|, x:i,Х...Х4 сигналь на прямых а X), Х2, ..., Т - на инверсных выходах //(-триггеров 1-4.

На выходе элемента 2И-ИЛИ-НЕ - еди- ничный сигнал, если в последующем такте ;чётчик изменяет свое состояние,при этом с приходом импульса //(-триггер 18 меняет JQ свое состояние.

Таким образом, на единичном выходе этого триггера будет «О, если состояние счетчика четно, либо «ГГвПрОТй ЯОМхттучае. Любое нарущение последовательности ;чета повлечет за собой изменение в работе 55 блока 17.

Сигналы с выходов //(-триггера 18 поступают на входы блока 14, на два других

входа которого поступают сигнальг с блока четности 8.

Таким образом, на выходе элемента 2И-ЙЛИ 11 будет «О только в том случае, если число единиц на выходах //(-триггеров 1-4 четно. Это достигается за счет того, что в случае совпадения сигналов на выходах //(-триггеров I, 2 на выходе элемента НЕ 12 будет «1. Аналогично на выходах элементов 10 и 13 будут соответственно «О и «1. Если на выходах пар //(-триггеров 1, 2 и 3, 4 содержится нечетное число единиц, ТОна соответствующих элементах 9, 10 будет «I, а на выходах элементов 12, 13 - «О. На выходе элемента 2И-ИЛИ 11 будет , если на выходах элементов 9, 10 или на вы-ходах элементов 12, 13 будут «1, что соответствует четному числу единиц на выходах //(-триггеров 1-4.

Таким образом, при отсутствии сбоев в работе всех блоков счетчика на входы блока 14 поступают одновременно или «О ИЛИ «1 в зависимости от того, четно или нечетно состояние //(-триггеров 1-4. При этом на выходе элемента 16 будет «I и KS-триггер 22 находится в состоянии «О..

При возникновении сбоя в блоках счетчика на входы элемента 16, блока 14 и //(-триггера 18 .одновременно поступают инверсные относительно друг друга сигналы («О, «1, или «1, «О), на выходе элемента 16 будет «О, который переводитЙЗ-триггер 22 в состояние «1 и на индикаторе 23 появляется сигнал «Ошибка.

Формула изобретения

Счетчик импульсов с контролем ощибок, содержащий четыре //(-триггера, логические элементы И, включенные между выходами предыдущих и счетными входами- последующих //(-триггеров, блок четности, состоящий из трех логических элементов 2И-ИЛИ, между KOTOpbiivtH. включены логические элементы НЕ, причем входы первого логического элемента 2И-ИЛИ соединены с прямыми и инверсными выходами первого и второго //(-триггеров, входы второго логического элемента 2И-ИЛИ соединены с прямыми и инверсными вь1ходами третьего и четвертого //(-триггеров, входы третьего логического элемента 2И-ИЛИ подключены к выходам предыдущих логических элементов 2И-ИЛИ и Логических элементов НЕ блока четности, и блок индикации, состоящий изйЗ-триггера, выход которого подключен к индикатору, отличающийся тем, что, с целью повышения надежности и быстродействия, в него введены блок предсказания четности, состоящий из двух логических элементов 2И-НЕ и //(-триггера, и блок отрицания равнозначности, состоящий из инвертора и логического элемента 2И-ИЛИ-НЕ, первый вход которого

соединен с выходом инвертора, второй вход - с прямым выходом //(-триггера блока предсказания чётности, третий вход - со входом инвертора и выходом третьего из логических элементов 2И-ИЛИ блока четности, четвертый вход подключен к инверсному выходу //(-триггера блока предсказания четности, а выход логического элемента 2И-ИЛИ-НЕ соединен с -входом R8 -триггера блока индикации, причем С-вход//(-триггера блока предсказания .четности соединен с шиной входного сигнала, R и S-входы соединены с аналогич ными входами других //(-триггеров, а I и К-входы - с выходами первого логического элемента 2И-НЕ блока предсказания четности, первый вход которого соединен с выходом второго логического элемента 2И-НЕ, первый вход которого соединен с прямым выходом второго //(-триггера, второй вход - с инверсным выходом третьего //(-триггера, а второй вход первого логического элемента 2И-НЕ соединен с инверсным выходом первого //(-триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 336730, кл Н 03 К 21/00, 02.06.70.

2.Заявка Японии № 44-3301, кл. 98 (9) D 11, 16.07.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля неисправности механизма поворота лотков инкубаторов | 1987 |

|

SU1493211A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| Устройство для автоматической центрировки линз | 1982 |

|

SU1118882A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Устройство для сопряжения информационных каналов программно-коммутируемой логической сети | 1986 |

|

SU1322293A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Электронная игра | 1988 |

|

SU1523156A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1310755A1 |

Авторы

Даты

1979-05-05—Публикация

1974-12-31—Подача