1

Изобретение относится к импульсной технике.

Известен двоичный счетчик импульсов, содержащий триггерные ячейки, соединенные последовательно, входные логические эпемен-g ты и логические элементы, включенные между триггерными ячейками .

Однако такой счетчик не обеспечивает необходимого быстродействия.

Наиболее близким по технической сущ- JQ ности к изобретению является двоичный счетчик импульсов, содержащий триггеры с входными логическими элементами 2И-ИЛИ-НЕ, выходы которых соединены со входами триггеров, блок сквозного перекоса, состоящий jj из последовательно включенных логических элементов 2И-ИЛИ-НЕ и И-ИЕ, причем выходы логических элементов 2И-ИЛИ-НЕ блока соединены со входами входных логических элементов 2И-ИЛИ-НЕ четшлх раз- 20 рядов счетчика 2J.

Однако и этот счетчик не обеспечивает необходимого быстродействия.

Целью изобретения является увеличение быстродействия.25

Для этого в двоичный счетчик импульсов, содержащий триггеры с входными логическими элементами 2И-ИЛИ-НЕ, выходы которых соединены со входами триггеров, блок сквозного переноса, состоящий из последовательчо включенных логических элементов 2 И-И Л И-НЕ и И-НЕ, причем выходы логических элементов 2 И-ИЛ И-НЕ блока соединены со входами входных логических элементов 2 И-И Л И-НЕ четных разрядов счетчика, введен дополнительный логический элемент И-НЕ, вход которого соединен с источником сигналов Обнуление, а выходы подключены ло входамз триггеров четных разрядов и входам вхоан1:,1х логических элементов 2И-ИЛИ-ИЕ нечетных разрядов, при этом соответствующие выходы триггеров нечетных разрядов соединены со входами логических элементов И-НЕ блока сквозного переноса, а выходы триггеров четных разрядов соединетл со входами логических элементов 2И-ИЛИ-НЕ блока сквозного переноса.

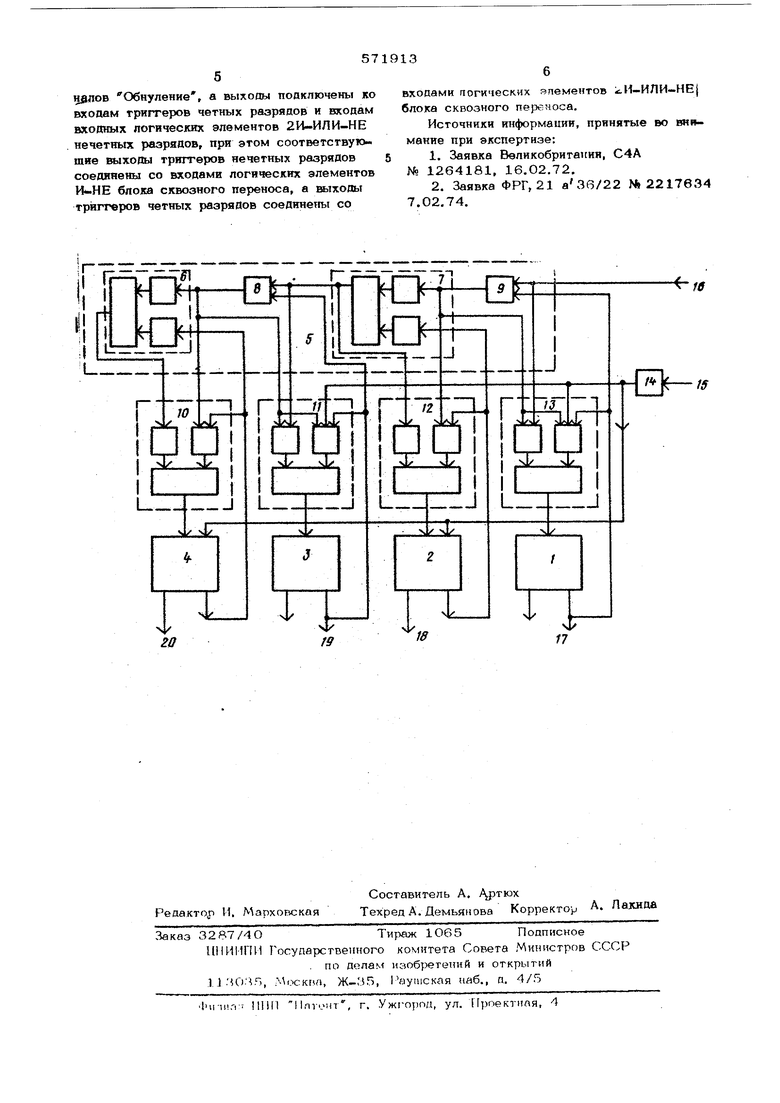

На чертеже приведена структуужая электрическая схема счетчика. Счетчик содержит функционально полные триггеры 1-4 (разряшя). Функционально по кый триггер состоит из вспомогательного и основного триггера (на чертеже не noKf- г ны) и представляет следующие свойства вс разрядов счетчика: сигнал, подаваемый на вход функционально полного триггера, яэме кяет его состояние на время следующего такта; после окончания такта триггер автс матически обнуляется, если на входе нет никаких управляющих сигналов, определяющих его состояние. В состав счетчика таюке входит блок 5 сквозного переноса, состоящий из логичесK Jx элементов 2И-ИЛИ-НЕ 6, 7 и логических элементов И-НЕ 8, 9, вхопные логичео гие элементы 2И-ИЛИ-НЕ , и дополнительный логический элемент И-НЕ 14, н сход 15 которого подан сигнал обнуления, а на вход 16 подаются входные импульсы. Вь ходные сигналы снимаются с выходов 17-2О. Принцип работы счетчика заключается в следующем. При обнуления двоичного счетчика 6 jerifbie разряды счетчика 2, 4 производится гфинудительнйя запись единицы, т.е. с fK прямых выходов снимается инверсное значение разряда. Съем информации со счетчика производит ел с выходов 17, 19 у нечетных разрядов 1, 3 н с инверсных выходов 18, 20 у четных разрядов 2, 4. При поступлении импульса ил источника сигналов Обнуление на вход логического элемента 14, на входах элементов 1О-13 запрещается регенерация содержимого нечег ных разрядов счетчика 1,3, а на входы триггеров 2,4 четных разрядов счетчика записывается единица (). Результируюшее состояние прямых выходов, счетчика - iOlO. Импульсы, поступающие на вход 16, суммируются в двоичном счегчике. При поступлении первого импульса на вход 16 через элемент 13 производится за пись единицы на триггер 1 первого разряда счетчика 2, а на остальных триггерах счет чика происходит рюгенерация содержимого Результирукшее состояние прямых выхо« ИОВ счетчика - 1О11. При поступлении второго импульса на вход 16 в блок 5 на входах элементов 10-13 запрещается регенерация содержимого триггеров первого и второго разряда счетчика 1,2, а на остальных триггерах счетчика происходит регенерация. Результирующее состояние выходов счетчика - 1000. При поступлении третьего импульса на вход 16 через элемент 13 производится запись единиць на триггер 1 первого разряда счетчика, а на остальных триггерах счетчика происходит генерация содержимого. Результирующее состояние №.гходов счетчика 10О1. При поступлении четвертого импульса на вход 16 через последовательно включенные логические элементы 2И-ИЛИ-НЕ и И-НЕ блока 5 н элементы 11,12 произвопится запись единицы на триггерк. 2,3 вто рого и третьего разряда счетчика, на входах элемента 13 запрещается генерация содержимого триггера 1 первого разряда счетчика, а на остальных триггерах счетчика происходит регенерация. Результируквдее состояние прямых выходов счетчика - 1110. При поступлении пятого импульса на вход 16 через элемент 13 производится запись единицы на триггер первого разряда счетчика 1, а на остальных триггерах счетчика происходит регенерация содержимого. Результирующее состояние прямых выходов счетчика - 1111. При поступлении последукяцих импульсов на вход 16 работа двоичного счётчика происходит аналогично. При групповом переносе на нечетное число разрядов ко входам элемент И-НЕ переноса в последукшую группу разрядов счетчика подключены прямой выход переноса из предыдущей группы, прямые выходь.1 нечетных разрядов группы и инверсные выходы четных разрядов группы счетчика. Это приводит к дальнейщему увеличению быстродействия счетчика без дополнительных затрат инверторов. Счетчик разбивается на группы с нечетным числом разрядов таким образом, что группа начинается и кончается нечетными разрядами счетчика. Формула изобретения Двоичный счетчик импульсов, содержащий триггеры с входными логическими элементами 2И-ИЛИ-НЕ, выходы которых соединены со входами триггеров, блок сквозного переноса, состоящий из последовательно включенных логических элементов 2И-ИЛИ- НЕ н И-НЕ, причем выходы логических элементов 2И-ИЛИ-НЕ блока- соединены со входами входных логических элементов 2И-ИЛИ-НЕ четных разрядов счетчика, о ъличаюшийся ,тем, что, с целью величения быстродействия, в него введен дополнительный логический элемент И-НЕ, ход которого соединен с источником сигналов Обнуление , а выходы подключены ко входам триггеров четных разрядов и входам входных погических элементов 2И-ИЛИ-НЕ нечетных разрядов, при этом соответствуюшие выходы триггеров нечетных разрядов соединены со входами логических элементов И.НЕ блока сквозного переноса, а выходы триггеров четных разрядов соединетты со

входами погических элементов IcM-ИЛИ-HEJ блока сквозного переноса,

Источники информации, принятые во внимание при экспертизе:

1.Заявка Великобритании, С4А № 1264181, 16,02.72.

2.Заявка ФРГ, 21 а36/22 N 2217634 7.02.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик импульсов | 1976 |

|

SU653746A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Устройство для формирования вычета по произвольному модулю от числа | 1989 |

|

SU1674379A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Двоичный счетчик импульсов | 1981 |

|

SU1001486A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

Авторы

Даты

1977-09-05—Публикация

1976-02-25—Подача