Указанные недостатки влекут за собой значительную потерю производит-ельности, а их устранение аппаратном путем приводит к существенному усложнению схемы.

Цель изобретения - повышение производительности канала ввода-вывода путем совмещения работы блока сопряжения с медленнодействующими внещними устройствами и обмена данными одного из блоков сопряжения с быстродействующими внешними устройствами, а также сокращение оборудования.

Цель достигается тем, что канал вводавывода содержит блок микропрограммного управления, первый-пятый входы-выходы; которого соединены соответственно с вторыми входами-выходами блока хранения управляющей информации и блока модификации управляющей информации, с третьим входом-выходом блока приоритетов, с четвертым входом-выходом блока сопряжения с медленнодействующими внещними устройствами, с щестым входомвыходом формирования управляющей информации, четвертые входы-выходы блоков ..сопряжения с быстродействующими устройствами соединены с шестым входом-выходом блока микропрограммного управления седьмой вход-выход которого является третьим входом-выходом канала ввода-вывода, а третий вход-выход блока хранения управляющей информации соединен с пятым входом-выходом блока сопряжения с медленнодействующими внешними устройствами.

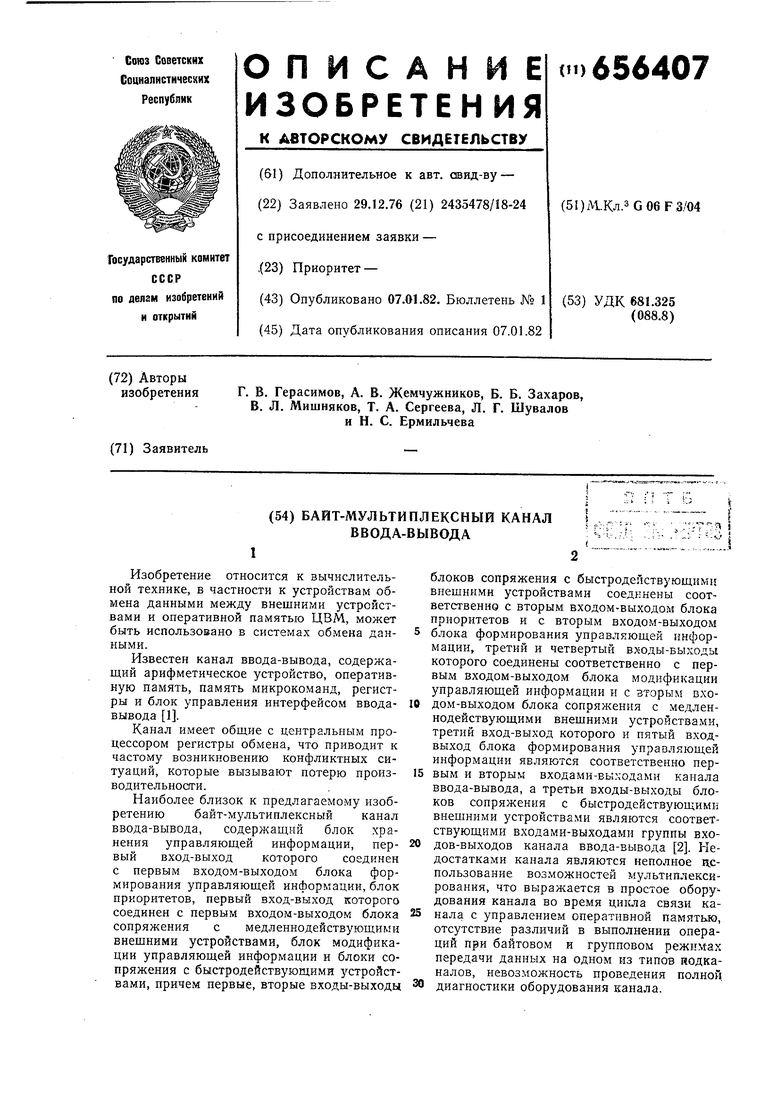

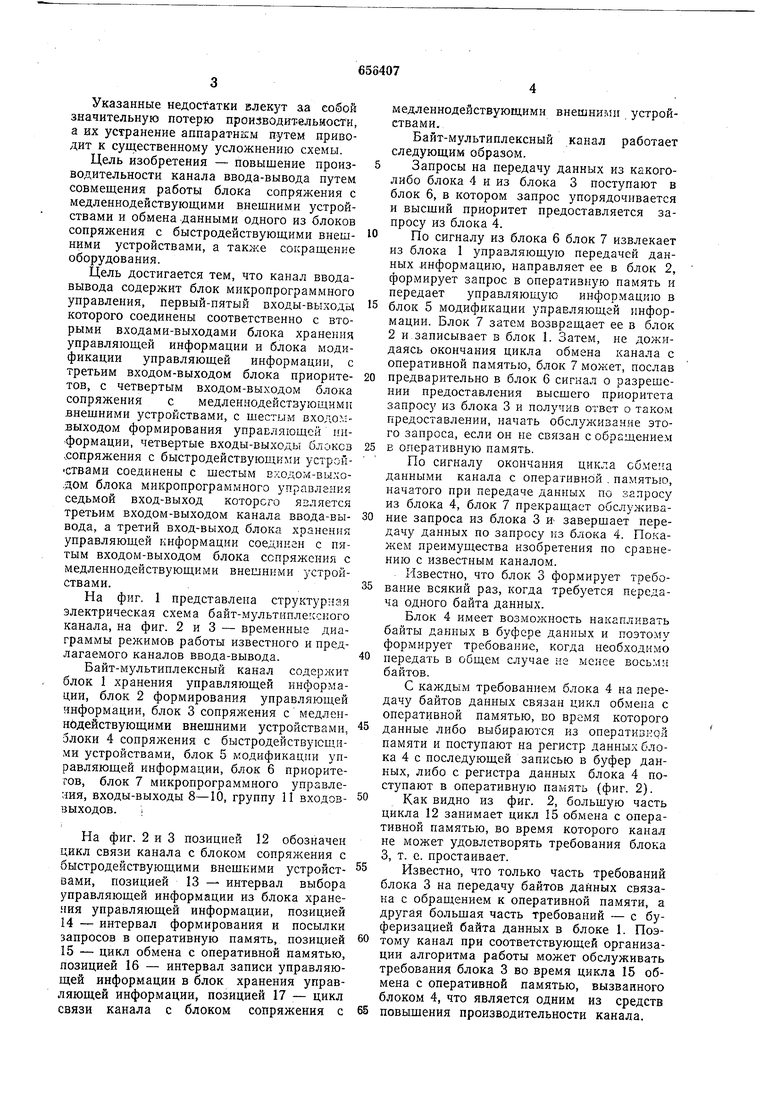

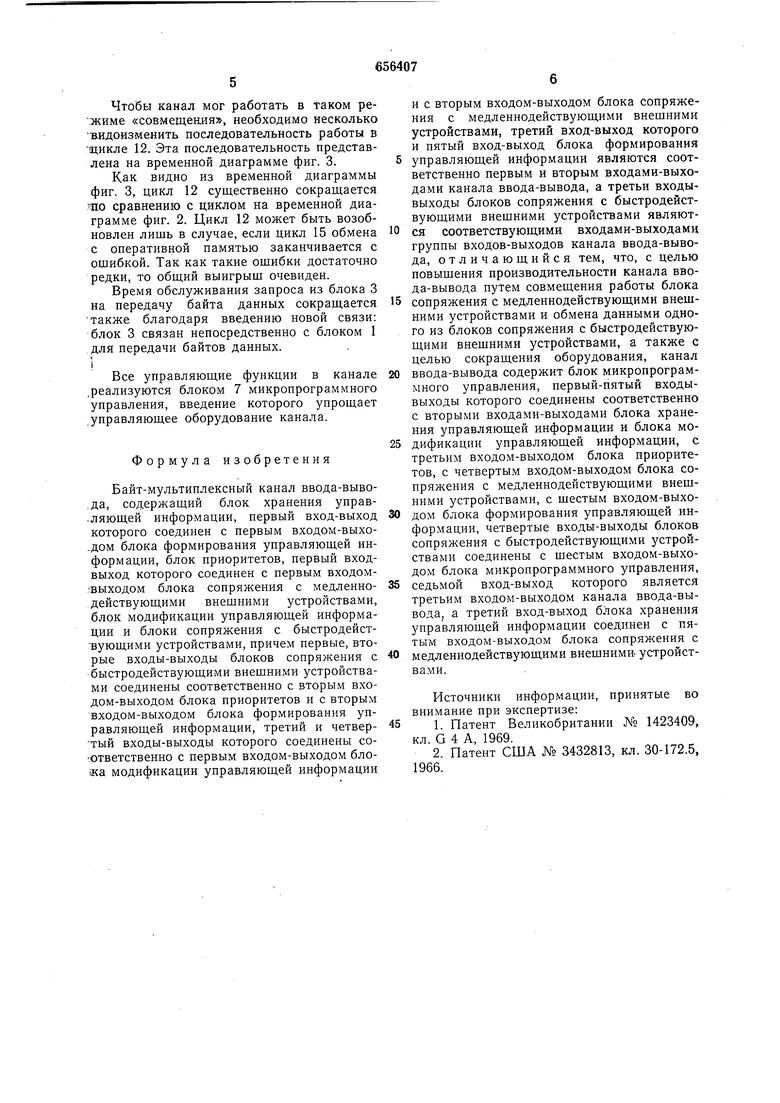

На фиг. 1 представлена структурная электрическая схема байт-мультиплексного канала, на фиг. 2 и 3 - временные диаграммы режимов работы известного и предлагаемого каналов ввода-вывода.

Байт-мультиплексный канал содержит блок 1 хранения управляющей информации, блок 2 формирования управляющей информации, блок 3 сопряжения с медленнодействующими внешними устройствами, Злоки 4 сопряжения с быстродействующими устройствами, блок 5 модификации управляющей информации, блок 6 приоритетов, блок 7 микропрограммного управления, входы-выходы 8-10, группу И входоввыходов, i

На фиг. 2 и 3 позицией 12 обозначен цикл связи канала с блоком сопряжения с быстродействующими внешними устройствами, позицией 13 - интервал выбора управляющей информации из блока хранения управляющей информации, позицией

14- интервал формирования и посылки запросов в оперативную память, позицией

15- цикл обмена с оперативной памятью, позицией 16 - интервал записи управляющей информации в блок хранения управляющей информации, позицией 17 - цикл связи канала с блоком сопряжения с

медленнодействующими внешними устройствами.

Байт-мультиплексный канал работает следующим образом.

Запросы на передачу данных из какоголибо блока 4 и из блока 3 поступают в блок 6, в котором запрос упорядочивается и высший приоритет предоставляется запросу из блока 4.

По сигналу из блока 6 блок 7 извлекает из блока 1 управляющую передачей данных .информацию, направляет ее в блок 2, формирует запрос в оперативную память и передает управляющую информацию в

блок 5 модификации управляющей информации. Блок 7 затем возвращает ее в блок 2 и записывает в блок 1. Затем, не дожидаясь окончания цикла обмена канала с оперативной памятью, блок 7 может, послав

предварительно в блок 6 сигнал о разрешении предоставления высшего приоритета запросу из блока 3 и получив ответ о таком предоставлении, начать обслуживание этого запроса, если он не связан с обращением

Е оперативную память.

По сигналу окончания цикла обмена данными канала с оперативной . памятью, начатого при передаче данных по запросу из блока 4, блок 7 прекращает обслуживание запроса из блока 3 и заверщает передачу данных по запросу из блока 4. Покал ем преимущества изобретения по сравнению с известным каналом.

Известно, что блок 3 формирует требование всякий раз, когда требуется передача одного байта данных.

Блок 4 имеет возможность накапливать байты данных в буфере данных и поэтому формирует требование, когда необходимо

передать в общем случае не менее восьми байтов.

С каждым требованием блока 4 на передачу байтов данных связан цикл обмена с оперативной памятью, во время которого

данные либо выбираются из оперативной памяти и поступают на регистр данных блока 4 с последующей записью в буфер данных, либо с регистра данных блока 4 поступают в оперативную память (фиг. 2).

Как видно из фиг. 2, большую часть цикла 12 занимает цикл 15 обмена с оперативной памятью, во время которого канал не может удовлетворять требования блока 3, т. е. простаивает.

Известно, что только часть требований блока 3 на передачу байтов данных связана с обращением к оперативной памяти, а другая большая часть требований - с буферизацией байта данных в блоке 1. Поэтому канал при соответствующей организации алгоритма работы может обслуживать требования блока 3 во время цикла 15 обмена с оперативной памятью, вызванного блоком 4, что является одним из средств

повышения производительности канала.

Чтобы канал мог работать в таком режиме «совмещенля, необходима несколько видоизменить последовательность работы в щикле 12. Эта последовательность представлена на временной диаграмме фиг. 3.

Как видно из временной диаграммы фиг. 3, цикл 12 существенно сокращается эдо сравнению с циклом на временной диаграмме фиг. 2. Цикл 12 может быть возобновлен лищь в случае, если цикл 15 обмена с оперативной памятью заканчивается с ощибкой. Так как такие ощибки достаточно редки, то общий выигрыщ очевиден.

Время обслуживания запроса из блока 3

на передачу байта данных сокращается

также благодаря введению новой связи:

блок 3 связан непосредственно с блоком 1

для передачи байтов данных.

Все управляющие функции в канале .реализуются блоком 7 микропрограммного управления, введение которого упрощает .управляющее оборудование канала.

Формула изобретения

Байт-мультиплексный канал ввода-выво,да, содержащий блок хранения управ-ляющей информации, первый вход-выход которого соединен с первым входом-выхо-Дом блока формирования управляющей информации, блок приоритетов, первый входвыход которого соединен с первым входомвыходом блока сопряжения с медленно.действующими внешними устройствами, блок модификации управляющей информации и блоки сопряжения с быстродействующими устройствами, причем первые, вторые входы-выходы блоков сопряжения с быстродействующими внешними устройствами соединены соответственно с вторым входом-выходом блока приоритетов и с вторым входом-выходом блока формирования управляющей информации, третий и четвертый входы-выходы которого соединены со-.ответственно с первым входом-выходом бложа модификации управляющей информации

и с вторым входом-выходом блока сопряжения с медленнодействующими внешними устройствами, третий вход-выход которого и пятый вход-выход блока формирования 5 управляющей информации являются соответственно первым и вторым входами-выходами канала ввода-вывода, а третьи входывыходы блоков сопряжения с быстродействующими внешними устройствами являются соответствующими входами-выходами группы входов-выходов канала ввода-вывода, отличающийся тем, что, с целью повышения производительности канала ввода-вывода путем совмещения работы блока

15 сопряжения с медленнодействующими внешними устройствами и обмена данными одного из блоков сопряжения с быстродействующими внещними устройствами, а также с целью сокращения оборудования, канал

0 ввода-вывода содержит блок микропрограммного управления, первый-пятый входывыходы которого соединены соответственно с вторыми входами-выходами блока хранения управляющей информации и блока модификации управляющей информации, с третьим входом-выходом блока приоритетов, с четвертым входом-выходом блока сопряжения с медленнодействующими внещними устройствами, с шестым входом-выхо0 дом блока формирования управляющей информации, четвертые входы-выходы блоков сопрял ения с быстродействующими устройствами соединены с шестым входом-выходом блока микропрограммного управления,

5 седьмой вход-выход которого является третьим входом-выходом канала ввода-вывода, а третий вход-выход блока хранения управляющей информации соединен с пятым входом-выходом блока сопряжения с

медленнодействующими внещними устройствами.

Источники информации, принятые во внимание при экспертизе:

5 1. Патент Великобритании N° 1423409, кл. G 4 А, 1969.

2. Патент США № 3432813, кл. 30-172.5, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Байт-мультиплексный канал | 1981 |

|

SU972496A1 |

| Байт-мультиплексный канал | 1979 |

|

SU803699A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Система обмена | 1978 |

|

SU809138A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| СШТШДА ОБРАБОТКИ ДАННЫХ1 Т Бii^f;'- ViJ- i^ О г^ ал | 1970 |

|

SU433484A1 |

Авторы

Даты

1982-01-07—Публикация

1976-12-29—Подача