(А) БАЙТ-МУЛЬТИПЛЕКСНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Байт-мультиплексный канал ввода-вывода | 1976 |

|

SU656407A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Байт-мультиплексный канал | 1979 |

|

SU803699A1 |

| Канал ввода-вывода информации | 1982 |

|

SU1049892A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

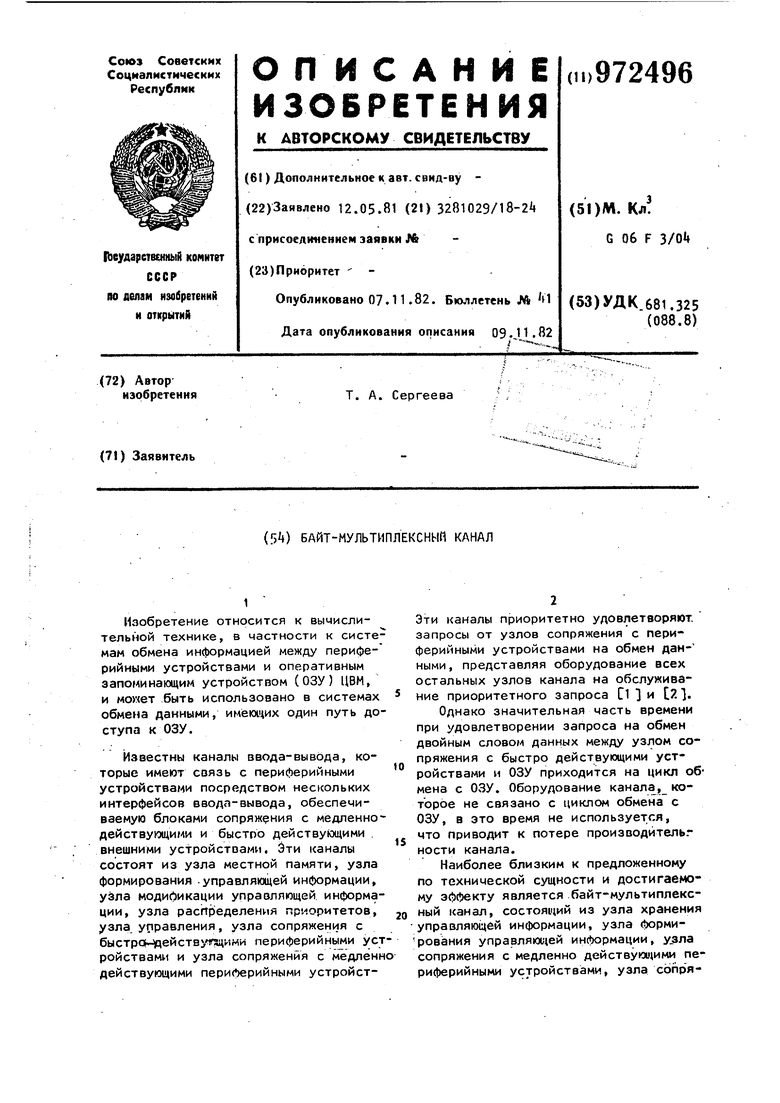

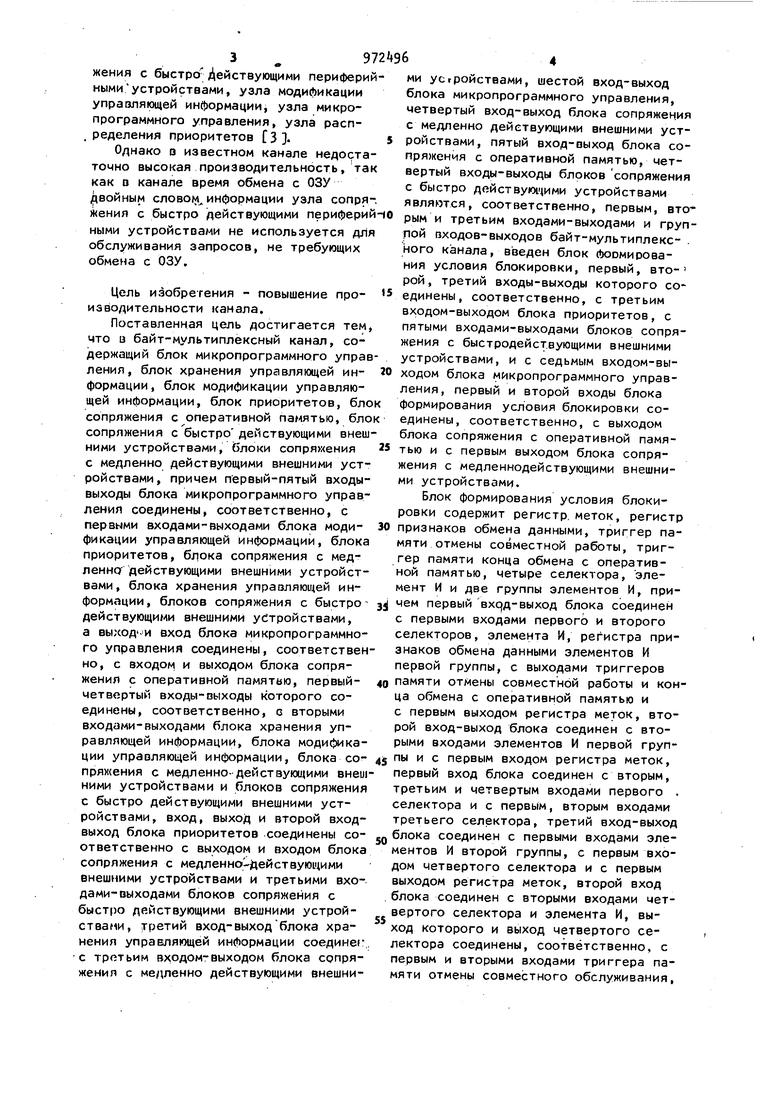

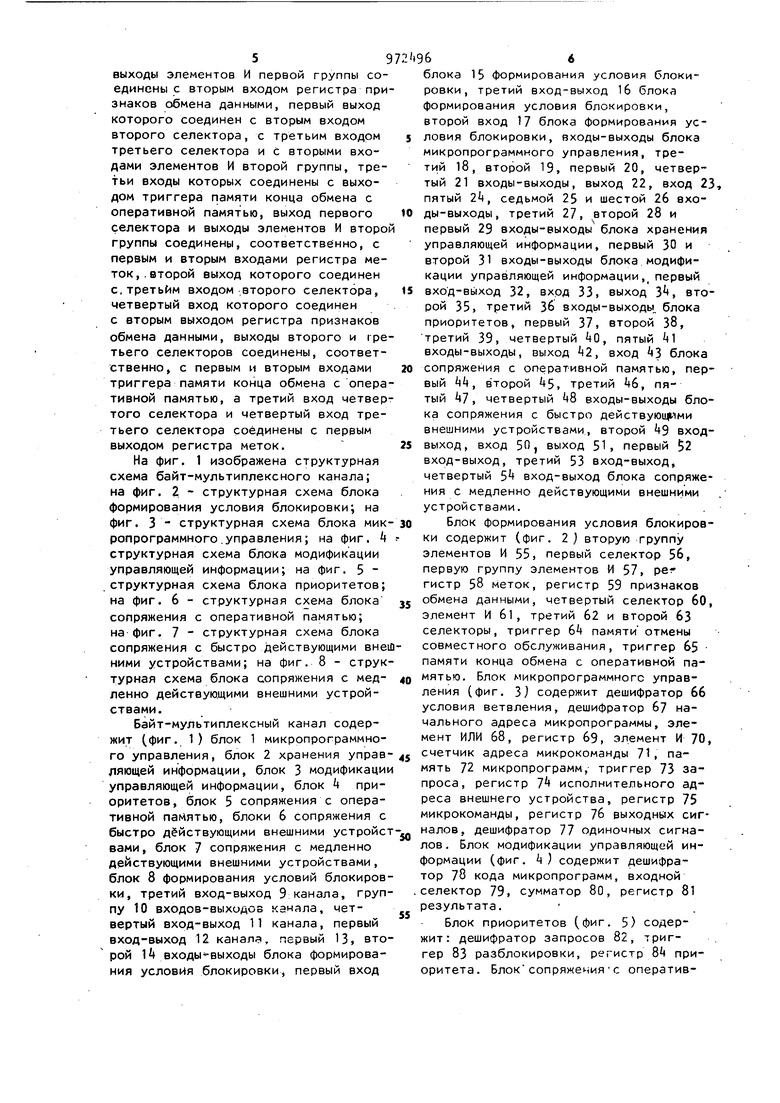

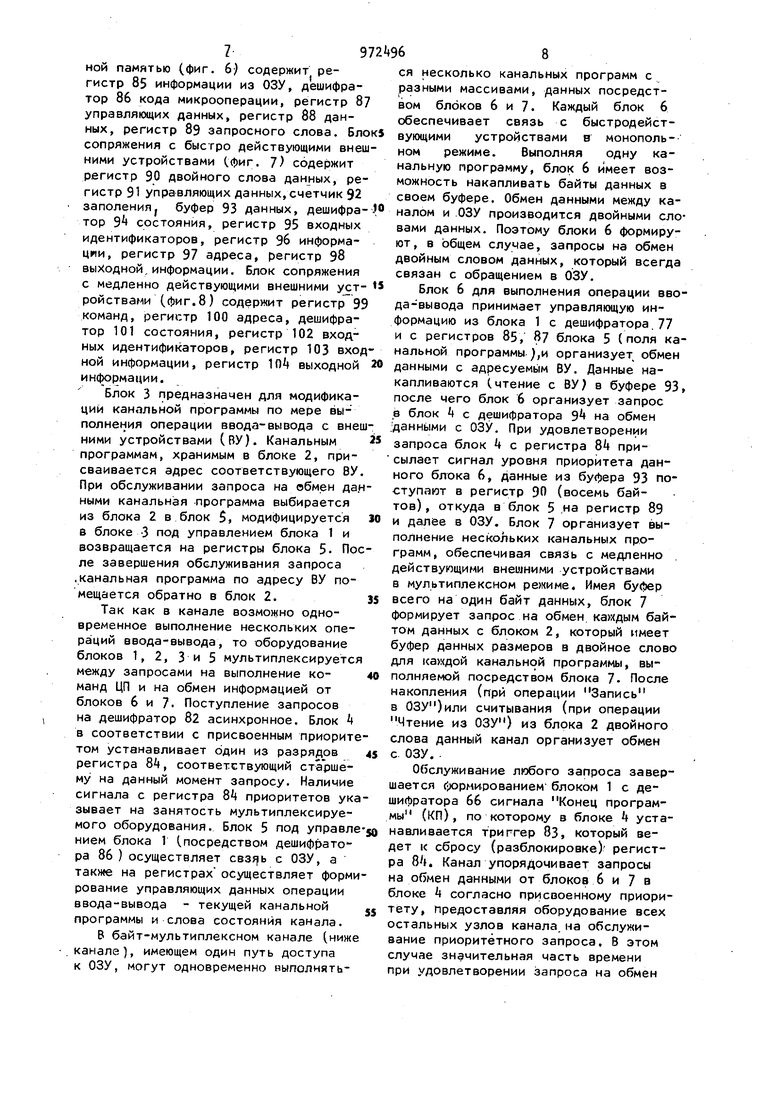

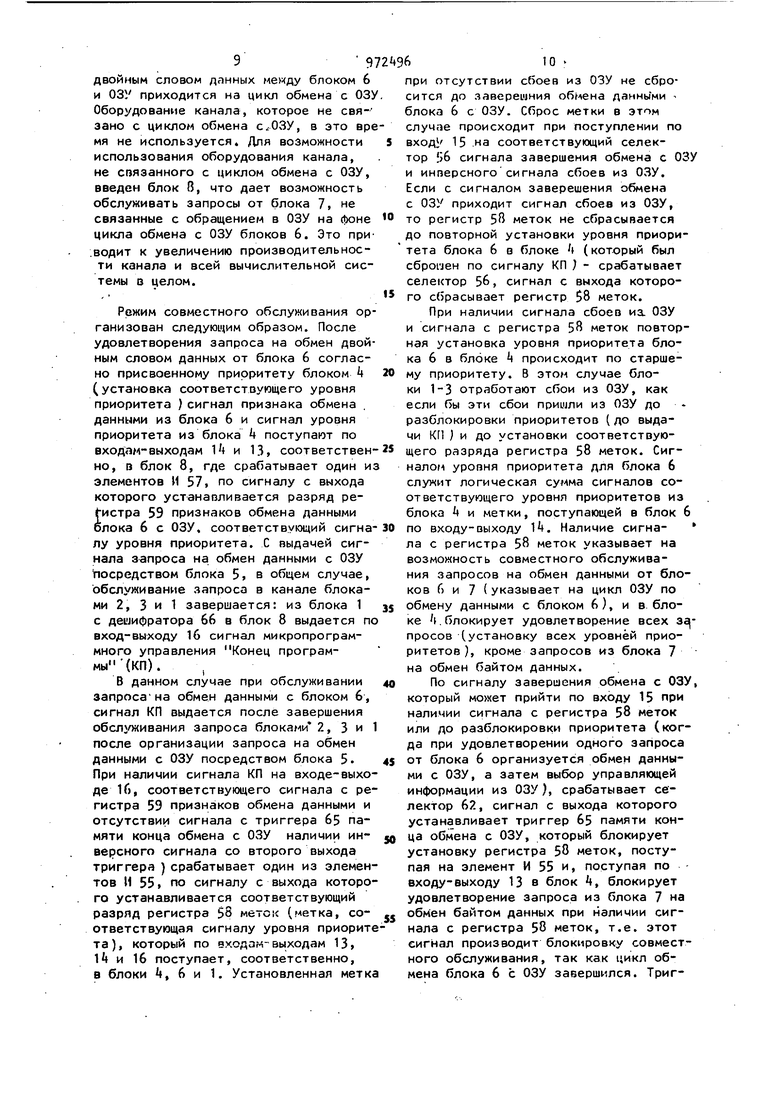

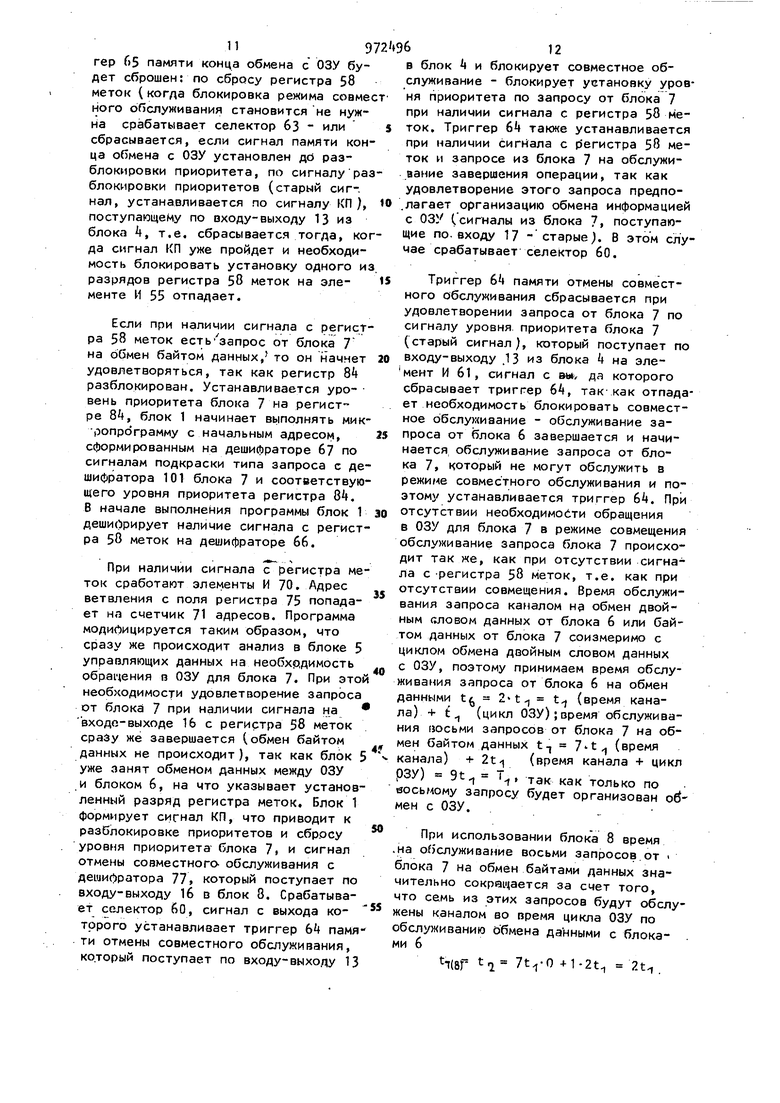

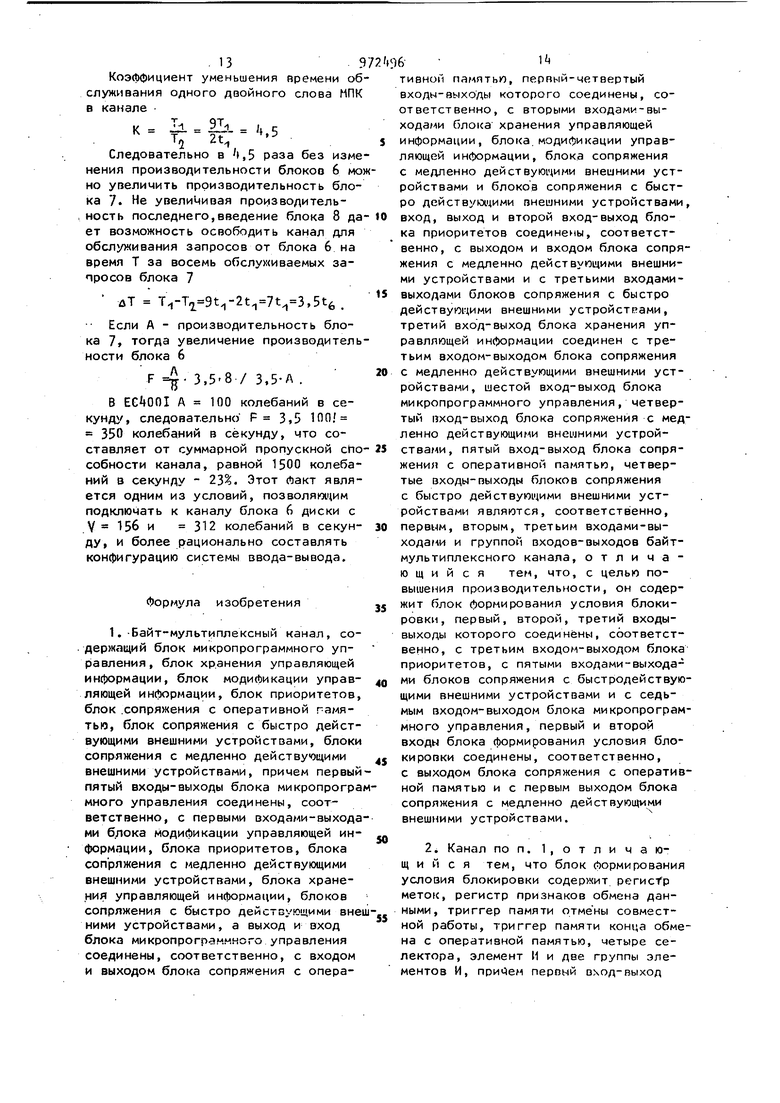

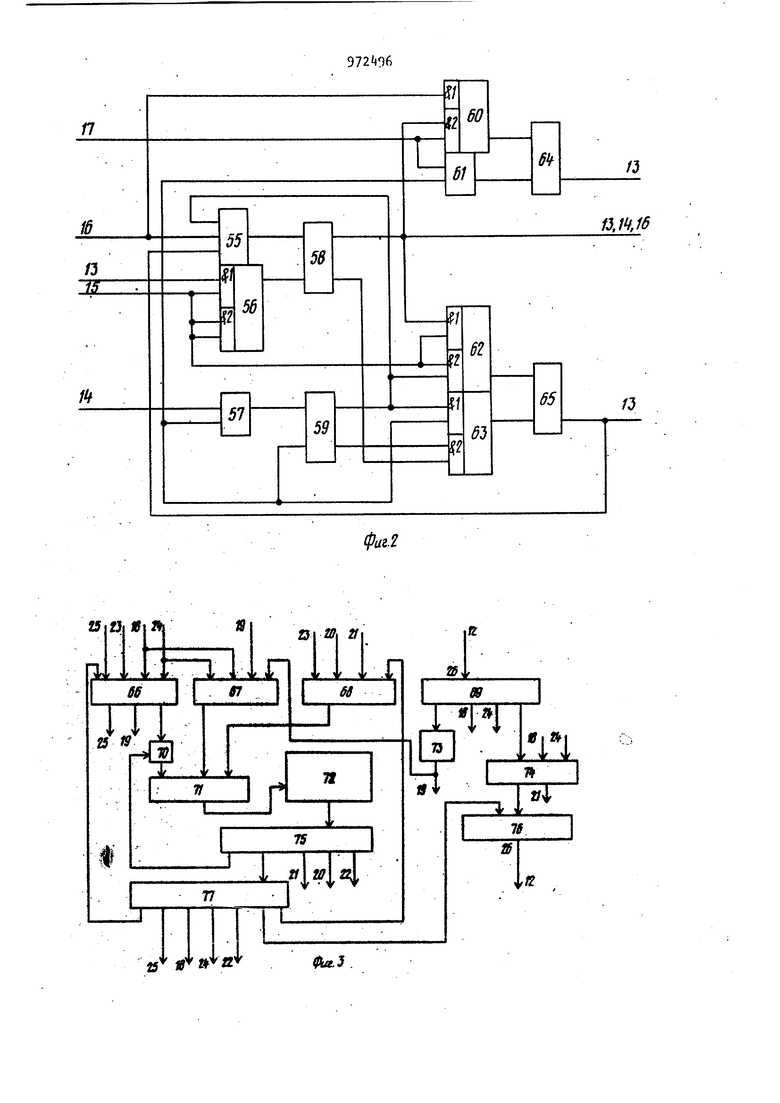

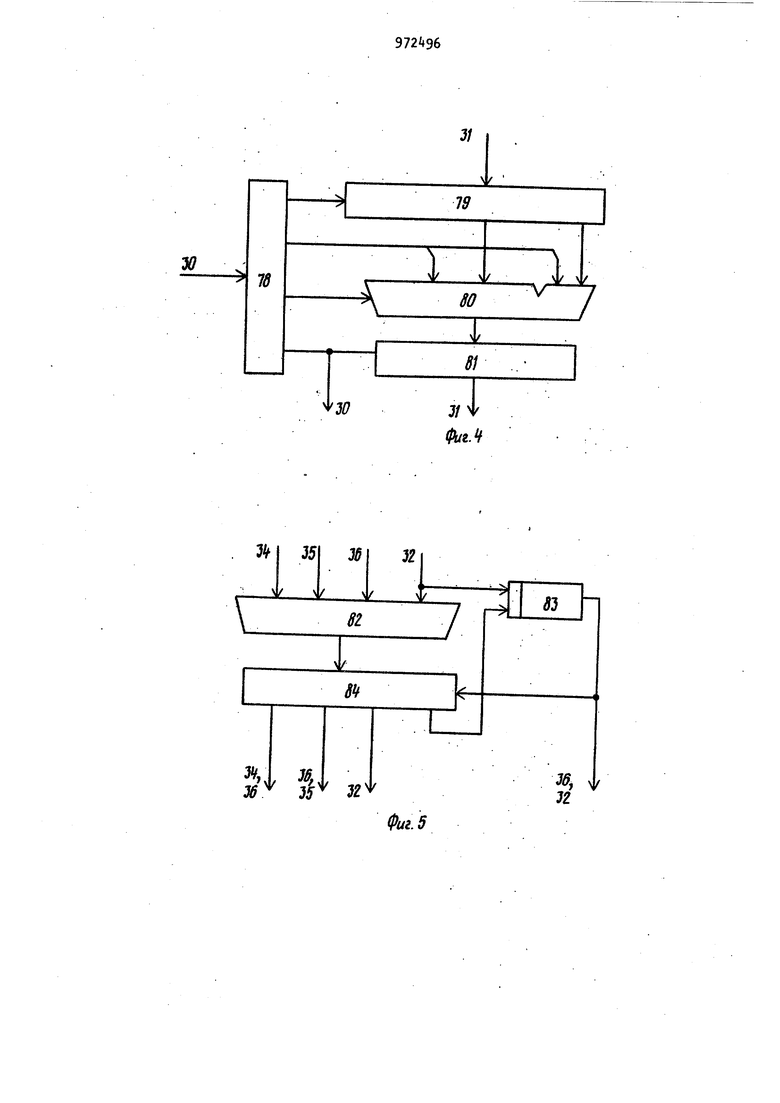

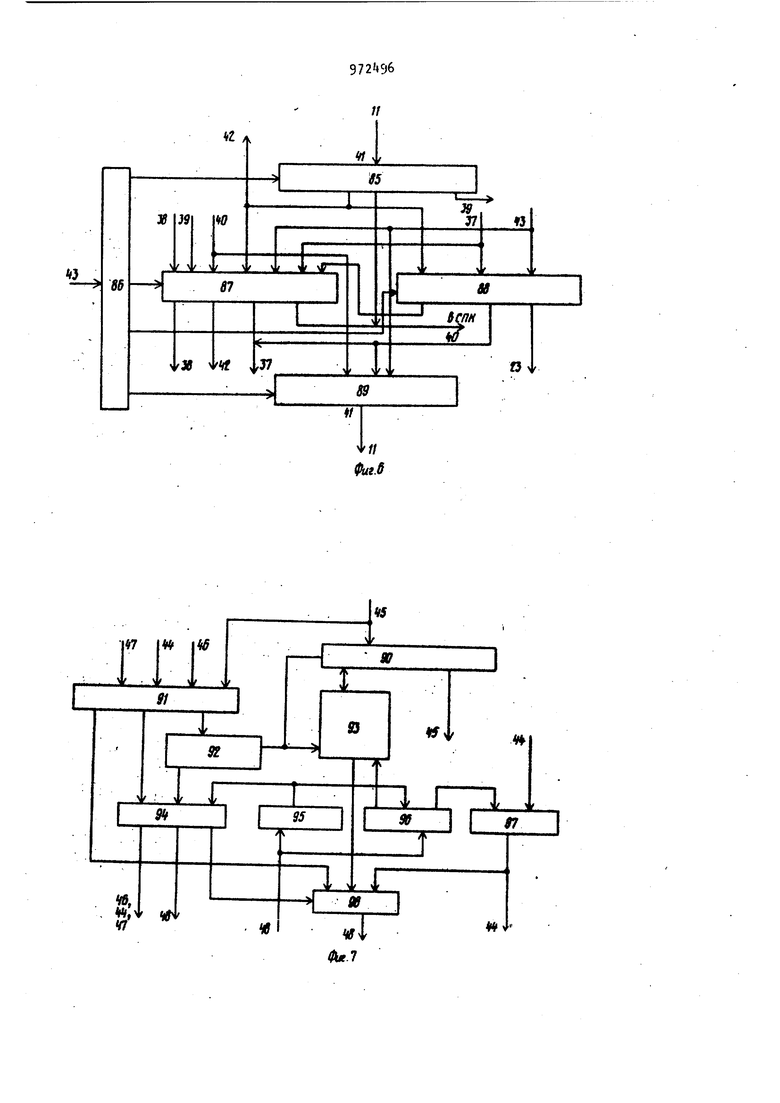

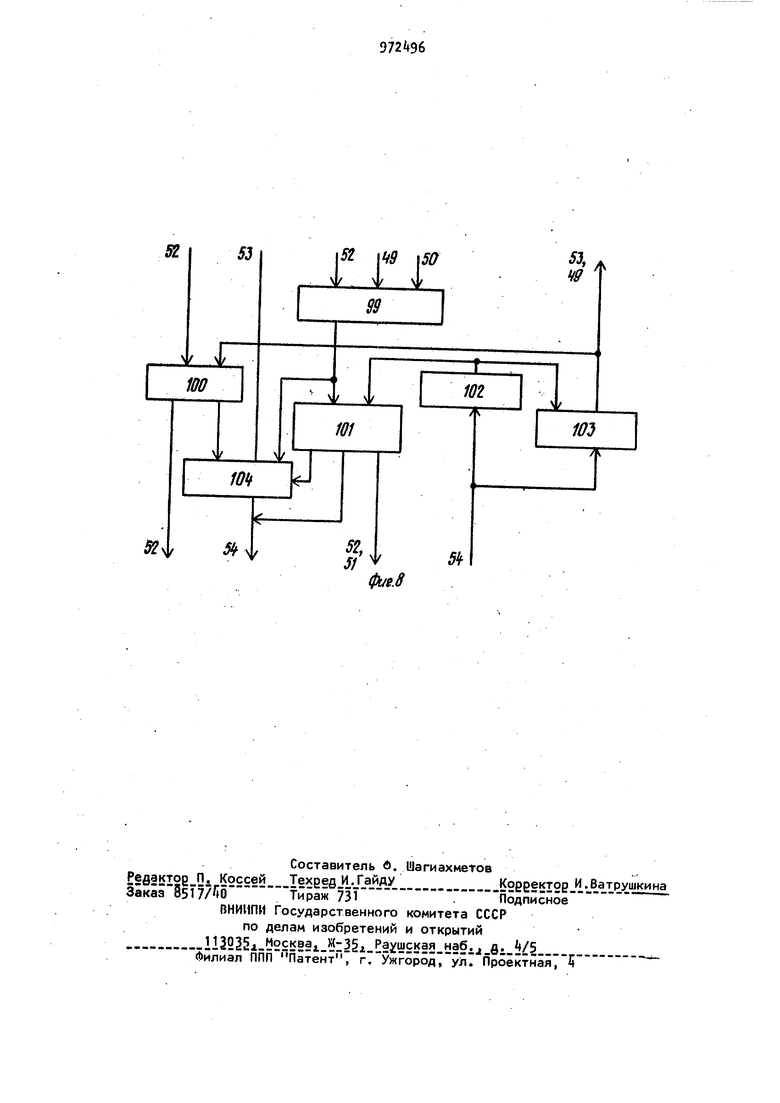

Изобретение относится к вычислительйой технике, в частности к систе мам обмена информацией между периферийными устройствами и оперативным запоминающим устройством (ОЗУ) ЦВМ, и быть использовано в системах обмена данными, имёщих один путь до ступа к ОЗУ. Известны каналы ввода-вывода, которые имеют связь с периферийными устройствами посредством нескольких интерфейсов ввода-вывода, обеспечиваемую блоками сопряжения с медленнодействущими и быстро действующими . внешними устройствами. Эти каналы состоят из узла местной памяти, узла формирования -управляющей информации, узла модификации управляющей информации, узла распределения приоритетов, узла управления, узла сопряжения с быстрончействууячими периферийными уст ройствами и узла сопряжения с медленн действующими периферийными устройстЭти каналы приоритетно удовлетворяют, запросы от узлов сопряжения с периферийными устройствами на обмен данными, представляя оборудование всех остальных узлов канала на обслуживание приоритетного запроса Cl 1 и С. . Однако значительная часть времени при удовлетворении запроса на обмен двойным словом данных между узлом сопряжения с быстро действующими устройствами и ОЗУ приходится на цикл обмена с ОЗУ. Оборудование канала, которое не связано с циклом обмена с ОЗУ, в это время не использует;ся, что приводит к потере производйтельг ности канала. Наиболее близким к предложенному по технической сущности и достигаемому эффекту является байт-мультиплексный канал, состоящий из узла хранения управляющей информации, узла (юрмирования управляюи(ей информации, у.зла сопряжения с медленно действуюи ими периферийными устройствами, узла сопря3 „ 97 жения с быстро Действующими периферий нымиустройствами, узла модификации управляющей информации, узла микропрограммного управления, узла расп, ределения приоритетов З. Однако 3 известном канале недостаточно высокая производительность, так как о канале время обмена с ОЗУ двойным слово 4 информации узла сопряления с быстро действующими периферий ными устройствами не используется для обслуживания запросов, не требующих обмена с ОЗУ. Цель изобретения - повышение производительности канала. Поставленная цель достигается тем, что и байт-мультиплексный канал, содержащий блок микропрограммного управ ления, блок хранения управляющей информации, блок модификации управляющей информации, блок приоритетов, бло сопряжения с оперативной памятью, бло сопряжения сбыстродействующими внешними устройствами, блоки сопря ; ения с медленно действующими внешними устройствами, причем первый-пятый входывыходы блока микропрограммного управления соединены, соответственно, с первыми входами-выходами блока модификации управляющей информации, блока приоритетов, блока сопряжения с медленно действующими внешними устройствами, блока хранения управляющей информации, блоков сопряжения с быстро действующими внешними устройствами, а выход .и вход блока микропрограммного управления соединены, соответствен но, с входом и выходом блока сопряжения с оперативной памятью, первыйчетвертый входы-выходы которого соединены, соответственно, с вторыми входами-выходами блока хранения управляющей информации, блока модификации управляющей информации, блока сопряжения с медленно-действующими внеш ними устройствами и блоков сопряжения с быстро действующими внешними устройствами, вход, выхо;ц и второй входвыход блока приоритетов соединены соответственно с выходом и входом блока сопряжения с медленно- ействующими внешними устройствами и третьими входами-выходами блоков сопряжения с быстро действующими внешними устройствами, третий вход-выходблока хранения управляющей информации соединес с третьим входом-выходом блока сопряжения с медленно действующими внешни6ми усгройствами, шестой вход-выход блока микропрограммного управления, четвертый вход-выход блока сопряжения с медленно действующими внешними устройствами, пятый вход-выход блока сопряжения с оперативной памятью, четвертый входы-выходы блоков сопряжения с быстро действуЮ1цими устройствами , соответственно, первым, вторым и третьим входами-выходами игрупрой входов-выходов байт-мультиплекс- . ного канала, введен блок (Ьоомирования условия блокировки, первый, второй, третий входы-выходы которого соединены, соответственно, с третьим входом-выходом блока приоритетов, с пятыми входами-выходами блоков сопряжения с быстродейст.вующими внешними устройствами, и с седьмым входом-выходом блока микропрограммного управления, первый и второй входы блока формирования условия блокировки соединены, соответственно, с выходом блока сопряжения с оперативной памятью и с первым выходом блока сопряжения с медленнодействующими внешними устройствами. Блок формирования условия блокировки содержит регистр, меток, регистр признаков обмена данными, триггер памяти отмены совместной работы, триггер памяти конца обмена с оперативной памятью, четыре селектора, элемент И и две группы элементов И, приii первый вхс д-выход блока соединен с первыми входами первого и второго селекторов, элемента И, регистра признаков обмена данными элементов И первой группы, с выходами триггеров 0 памяти отмены совместной работы и конца обмена с оперативной памятью и с первым выходом регистра меток, второй вход-выход блока соединен с вторыми входами элементов И первой груп ы и с первым входом регистра меток, первый вход блока соединен с вторым, третьим и четвертым входами первого . селектора и с первым, вторым входами третьего селектора, третий вход-выход блока соединен с первыми входами элементов И второй группы. с первым входом четвертого селектора и с первым выходом регистра меток, второй вход блока соединен с вторыми входами четвертого селектора и элемента И, выход которого и выход четвертого селектора соединены, соответственно, с первым и вторыми входами триггера памяти отмены совместного обслуживания, 59 выходы элементов И первой группы соединены с вторым входом регистра при знаков обмена данными, первый выход которого соединен с вторым входом второго селектора, с третьим входом третьего селектора и с вторыми входами элементов И второй группы, третьи входы которых соединены с выходом триггера памяти конца обмена с оперативной памятью, выход первого селектора и выходы элементов И второ группы соединены, соответственно, с первым и вторым входами регистра меток,, второй выход которого соединен с,третьим входом-второго селектора, четвертый вход которого соединен с вторым выходом регистра признаков обмена данными, выходы второго и тре тьего селекторов соединены, соответственно , с первым и вторым входами триггера памяти конца обмена с опера тивной памятью, а третий вход четвер того селектора и четвертый вход третьего селектора соединены с первым выходом регистра меток. На фиг. 1 изображена структурная схема байт-мультиплексного канала; на фиг. 2 - структурная схема блока формирования условия блокировки; на фиг. 3 - структурная схема блока мик ропрограммного.управления; на фиг. структурная схема блока модификации управляющей информации; на фиг. 5 структурная схема блока приоритетов; на фиг. 6 - структурная схема блока сопряжения с оперативной памятью; на фиг. 7 - структурная схема блока сопряжения с быстро действующими вне ними устройствами; на фиг. 8 - струк турная схема блока сопряжения с медленно действующими внешними устройствами. Байт-мультиплексный канал содержит (фиг. 1) блок 1 микропрограммного управления, блок 2 хранения управ ляющей информации, блок 3 модификаци управляющей информации, блок 4 приоритетов, блок 5 сопряжениях оперативной памятью, блоки 6 сопряжения с быстро действующими внешними устройс вами, блок 7 сопряжения с медленно действующими внешними устройствами , блок 8 формирования условий блокиров ки, третий вход-выход 9 канала, груп пу 10 входов-выхидов канала, четвертый вход-выход 11 канала, первый вход-выход 12 канала, первый 13, вто рой 1 входы выходы блока формирования условия блокировки, первый вход 66 блока 15 формирования условия блокировки, третий вход-выход 16 блока формирования условия блокировки, второй вход 17 блока формирования условия блокировки, входы-выходы блока микропрограммного управления, третий 18, второй 19, первый 20, четвертый 21 входы-выходы, выход 22, вход 23, пятый 2, седьмой 25 и шестой 26 входы-выходы, третий 27, второй 28 и первый 29 входы-выходы блока хранения управляющей информации, первый 30 и второй 31 входы-выходы блока модификации управляющей информации, первый вход-выход 32, вход 33, выход З, второй 35, третий Зб входы-выходы., блока приоритетов, первый 37, второй 38, третий 39, четвертый kQ, пятый 1 входы-выходы, выход 42, вход 3 блока сопряжения с оперативной памятью, первый k, второй tS, третий +6, пятый 47, четвертый 48 входы-выходы блока сопряжения с быстро действующими внешними устройствами, второй +9 входвыход, вход 50, выход 51, первый 52 вход-выход, третий 53 вход-выход, четвертый 5 вход-выход блока сопряжения с медленно действующими внешними устройствами. Блок формирования условия блокировки содержит (фиг. 2) вторую группу элементов И 55, первый селектор 56, первую группу элементов И 57, per гистр 5В меток, регистр 59 признаков обмена данными, четвертый селектор 60, элемент И 61, третий б2 и второй 63 селекторы, триггер 6 памяти отмены совместного обслуживания, триггер б5 памяти конца обмена с оперативной памятью. Блок микропрограммного управления (фиг. 3 содержит дешифратор 66 условия ветвления, дешифратор 67 начального адреса микропрограммы, элемент ИЛИ 68, регистр 69, элемент И 70, счетчик адреса микрокоманды 71, память 72 микропрограмм, триггер 73 запроса, регистр 7 исполнительного адреса внешнего устройства, регистр 75 микрокоманды, регистр 7б выходных сигналов, дешифратор 77 одиночных сигналов. Блок модификации управляющей информации (фиг. А) содержит дешифратор 78 кода микропрограмм, входной селектор 79, сумматор 80, регистр 81 результата. Блок приоритетов (фиг. 5) содержит: дешифратор запросов 82, триггер 83 разблокировки, регистр 8 приоритета. Блоксопряженияс оперативной памятью (фиг, 6) содержит регистр 85 информации из ОЗУ, дешифратор 86 кода микрооперации, регистр 8 управляющих данных, регистр 88 данных, регистр 89 запросного слова. Бло сопряжения с быстро действующими внеш ними устройствами Сфиг. 7) содержит регистр 90 двойного слова данных, регистр 91 управляющих данных, счетчик 92 заполенип, буфер 93 данных, дешифратор 9 состояния, регистр 95 входных идентификаторов, регистр 9б информации, регистр 97 адреса, регистр 98 выходной,информации. Блок сопряжения с медленно действующими внешними yjCTройствами (фиг.8) содержит регистр 99 команд, регистр 100 адреса, дешифратор 101 состояния, регистр 102 входных идентификаторов, регистр 103 вход ной информации, регистр 10 выходной информации. Блок 3 предназначен для модификации канальной программы по мере выполнения операции ввода-вывода с внеш ними устройствами (ВУ). Канальным программам, хранимым в блоке 2, присваивается адрес соответствующего ВУ. При обслуживании запроса на обмен да.н ными канальная программа выбирается из блока 2 в блок 5, модифицируется в блоке -3 под управлением блока 1 и возвращается на регистры блока 5. Пос ле завершения обслуживания запроса .канальная программа по адресу ВУ помещается обратно в блок 2. Так как в канале возможно одновременное выполнение нескольких операций ввода-вывода, то оборудование блоков 1, 2, 3 и 5 мультиплексируется между запросами на выполнение команд ЦП и на обмен информацией от блоков 6 и 7. Поступление запросов на дешифратор 82 асинхронное. Блок в соответствии с присвоенным приорите том устанавливает один из разрядов регистра 84, соответствующий старшему на данный момент запросу. Наличие сигнала с регистра 8 приоритетов ука зывает на занятость мультиплексируемого оборудования. Блок 5 под управле нием блока 1 {.посредством дешифратора 86 ) осуществляет свзщь с ОЗУ, а на регистрах осуществляет форми рование управляющих данных операции ввода-вывода - текущей канальной программы и слова состояния канала. В байт-мультиплексном канале (ниже канале), имеющем один путь доступа к ОЗУ, могут одновременно ныполняться несколько канальных программ с разными массивами, данных посредством блоков 6 и 7. Каждый блок 6 обеспечивает связь с быстродействующими устройствами в монопольном режиме. Выполняя одну канальную программу, блок 6 имеет возможность накапливать байты данных в своем буфере. Обмен данными между каналом и ОЗУ производится двойными словами данных. Поэтому блоки 6 формируют, в общем случае, запросы на обмен двойным словом данных, который всегда связан с обращением в ОЗУ. Блок 6 для выполнения операции ввода-вывода принимает управляющую информацию из блока 1 с дешифратора,77 и с регистров 85, 87 блока 5 (поля канальной программы ),и организует обмен данными с адресуемь1М ВУ. Данные накапливаются (чтение с ВУ) в буфере 93, после чего блок 6 организует запрос 8 блок 4 с дешифратора 9 на обмен данными с ОЗУ. При удовлетворении запроса блок с регистра 84 присылает сигнал уровня приоритета данного блока 6, данные из буфера 93 поступают в регистр 90 (восемь байтов) , откуда в блок 5 ,на регистр 89 и далее в ОЗУ. Блок 7 организует выполнение нескольких канальных программ, обеспечивая связь с медленно действующими внешними устройствами в мультиплексном режиме. Имея буфер всего на один байт данных, блок 7 формирует запрос на обмен байтом данных с блоком 2, который имеет буфер данных размеров в двойное слово для каждой канальной программы, выполняемой посредством блока 7- После накопления (при операции Запись в ОЗУ)или считывания (при операции Чтение из ОЗУ) из блока 2 двойного слова данный канал организует обмен с ОЗУ.. Обслуживание любого запроса завершается формированием блоком 1 с дешифратора 66 сигнала Конец программы (КП), по которому в блоке устанавливается триггер 83, который ведет к сбросу (разблокировке) регистра 84. Канал упорядочивает запросы на обмен данными от блоков 6 и 7 в блоке 4 согласно присвоенному приоритету, предоставляя оборудование всех остальных узлов канала на обслуживание приоритетного запроса. В этом случае значительная часть времени при удовлетворении запроса на обмен двойным словом данных блоком 6 и ОЗУ приходится на цикл обмена с ОЗУ Оборудование канала, которое не связано с циклом обмена , в это вре мя не используется. Для возможности использования оборудования канала, не связанного с циклом обмена с ОЗУ, введен блок 8, что дает возможность обслуживать запросы от блока 7, не связанные с обращением в ОЗУ на фоне цикла обмена с ОЗУ блоков 6. Это прИ .водит к увеличению производительности канала и всей вычислительной системы в целом. Режим совместного обслуживания организован следуюьцим образом. После удовлетворения запроса на обмен двойным словом данных от блока 6 согласно присвоенному приоритету блоком k (установка соответствующего уровня приоритета )сигнал признака обмена данными из блока 6 и сигнал уровня приоритета из блока k поступают по входам-выходам 1+ и 13, соответственно, в блок 8, где срабатывает один из элементов И 57, по сигналу с выхода которого устанавливается разряд ребистра 59 признаков обмена данными блока 6 с ОЗУ. соответствующий сигналу уровня приоритета. С выдачей сигнала запроса на обмен данными с ОЗУ посредством блока 5, в общем случае, обслуживание запроса в канале блоками 2, 3 и 1 завершается: из блока 1 с дешифратора 66 в блок 8 выдается п вход-выходу 16 сигнал микропрограммного управления Конец программы (КП). , В данном случае при обслуживании запросана обмен данными с блоком 6, сигнал КП выдается после завершения обсл /живания запроса блоками 2, 3 и после организации запроса на обмен данными с ОЗУ посредством блока 5. При наличии сигнала КП на входе-выхо де 16, соответствующего сигнала с ре гистра 59 признаков обмена данными и отсутствии сигнала с триггера 65 памяти конца обмена с ОЗУ наличии инверсного сигнала со второго выхода триггера ) срабатывает один из элемен тов И 55, по сигналу с выхода которо го устанавливается соответствующий разряд регистра $8 меток (.метка, соответствующая сигналу уровня приорит та), который по входам-выходам 13, 1 и 16 поступает, соответственно, в блоки , 6 и 1. Установленная метк при отсутствии сбоев из ОЗУ не сбросится до завере1чния обмена данными блока 6 с ОЗУ. Сброс метки в этом случае происходит при поступлении по входу 15 .на соответствующий селектор j6 сигнала завершения обмена с ОЗУ и инверсногосигнала сбоев из ОчЗУ. Если с сигналом заверешения обмена с ОЗУ приходит сигнал сбоев из ОЗУ, то регистр 5В меток не сбрасывается до повторной установки уровня приоритета блока 6 в блоке (который был сбропен по сигналу КП J - срабатывает селектор 5б, сигнал с выхода которого сбрасывает регистр 58 меток. При наличии сигнала сбоев иа ОЗУ и сигнала с регистра 5 меток повторная установка уровня приоритета блока 6 в блоке происходит по старшему приоритету. В этом случае блоки 1-3 отработают сбои из ОЗУ, как если бы эти сбои пришли из ОЗУ до разблокировки приоритетов (до выдачи Kfl ) и до установки соответствующего разряда регистра 58 меток. Сигналом уровня приоритета для блока 6 служит логическая сумма сигналов соответствующего уровня приоритетов из блока k и метки, поступающей в блок 6 по входу-выходу 1. Наличие сигнала с регистра 58 меток указывает на возможность совместного обслуживания запросов на обмен данными от блоков Г) и 7 {указывает на цикл ОЗУ по обмену данными с блоком 6 ), и в. блоке (.блокирует удовлетворение всех з просов (установку всех уровней приоритетов }, кроме запросов из блока 7 на обмен байтом данных. По сигналу завершения обмена с ОЗУ, который может прийти по входу 15 при наличии сигнала с регистра 58 меток или до разблокировки приоритета (когда при удовлетворении одного запроса от блока 6 организуется обмен данными с ОЗУ, а затем выбор управляющей информации из ОЗУ), срабатывает селектор б2, сигнал с выхода которого устанавливает триггер 65 памяти конца обмена с ОЗУ, который блокирует установку регистра 58 меток, поступая на элемент И 55 и, поступая по входу-выходу 13 в блок , блокирует удовлетворение запроса из блока 7 на обмен байтом данных при наличии сигнала с регистра 58 меток, т.е. этот сигнал производит блокировку совместного обслуживания, так как цикл обмена блока 6 с ОЗУ завершился. Три1- rep памяти конца обмена с ОЗУ будет сброшен: по сбросу регистра 58 меток {когда блокировка режима совмес ного обслуживания становится не нужна срабатывает селектор 63 или сбрасывается, если сигнал памяти конца обмена с ОЗУ установлен до разблокировки приоритета, по сигналураз блокировки приоритетов (старый сиг-, нал, устанавливается по сигналу КП ), поступающему по входу-выходу 13 из блока 4, т.е. сбрасывается тогда, ког да сигнал КП уже пройдет и необходимость блокировать установку одного из разрядов регистра 58 меток на элементе И 55 отпадает. Если при наличии сигнала с регистра 58 меток естьзапрос от блока 7 на обмен байтом данных, то он начнет удовлетворяться, так как регистр 8 разблокирован. Устанавливается уровень приоритета блока 7 на регист™ ре 8, блок 1 начинает вьюолнять микропрограмму с начальным адресом, сформированным на дешифраторе 67 по сигналам подкраски типа запроса с дешифратора 101 блока 7 и соответствующего уровня приоритета регистра 8. В начале выполнения программы блок 1 дешиОрирует наличие сигнала с регистра 50 меток на дешифраторе 66. При наличии сигнала с регистра меток сработают элементы И 70. Адрес ветвления с поля регистра 75 попадает на счетчик 71 адресов. Программа модифицируется таким образом, что сразу же происходит анализ в блоке 5 управляющих данных на необхр,димость обра1чения в ОЗУ для блока 7. При этой необходимости удовлетворение запроса от блока 7 при наличии сигнала на входе-выходе 16 с регистра 58 меток сразу же завершается (обмен байтом данных не происходит ), так как блок 5 уже занят обменом данных между ОЗУ и блоком 6, на что указывает установленный разряд регистра меток. Блок 1 формирует сигнал КП, что приводит к разблокировке приоритетов и сбросу уровня приоритета блока 7 и сигнал отмены совместного- обслуживания с дешифратора 77, который поступает по входу-выходу 16 в блок 8. Срабатывает селектор 60, сигнал с выхода котррого устанавлиаает триггер 6 памя ти отмены совместного обслуживания, который поступает по входу-выходу 13 В блок и блокирует совместное обслуживание - блокирует установку уровня приоритета по запросу от блока 7 при наличии сигнала с регистра 58 меток. Триггер 6 также устанавливается при наличии сигнала с регистра 58 меток и запросе из блока 7 на обслуживание завершения операции, так как удовлетворение этого запроса предполагает организацию обмена информацией с ОЗУ (.сигналы из блока 7 поступающие по. входу 17 -старые). В этом случае срабатывает селектор 60. Триггер б памяти отмены совместного обслуживания сбрасывается при удовлетворении запроса от блока 7 по сигналу уровня приоритета блока 7 (старый сигнал), который поступает по входу-выходу 13 из блока k на элемент И 61, сигнал с ш, да которого сбрасывает триггер 6, так как отпадает необходимость блокировать совместное обслуживание - обслуживание запроса от блока 6 завершается и начинается обслуживание запроса от блока 7, который не могут обслужить в режиме совместного обслуживания и поэтому устанавливается триггер 64. При отсутствии необходимобти обращения в ОЗУ для блока 7 в режиме совмещения обслуживание запроса блока 7 происходит так же, как при отсутствии сигнала с -регистра 58 меток, т.е. как при отсутствии совмещения. Время обслуживания запроса каналом нэ обмен двойным словом данных от блока 6 или байтом данных от блока 7 соизмеримо с циклом обмена двойным словом данных с ОЗУ, поэтому принимаем время обслуживания запроса от блока 6 на обмен данными t 2«t t (время канала) + t (цикл ОЗУ);время обслуживания (ВОСЬМИ запросов от блока 7 на обмен байтом данных t 7t (время канала) + 2t (время канала + цикл РЗУ) 9t Т, так как только по восьмому запросу будет организован обмен с ОЗУ.. При использовании блока 8 время .на о/)служивание восьми запросов от блока 7 на обмен байтами данных значительно сокращается за счет того, что семь из этих запросов будут обслужены каналом во время цикла ОЗУ по обслуживанию обмена данными с блоками 6 7(8Г Ч 7t,-0 -H-2ti 2t Коэффициент уменьшения времени об служивания одного двойного слова МПК в канале 1± 9Ь ,, 5 Т 2t, 5 Следовательно в (,5 раза без изме нения производительности блокоо 6 мо но увеличить производительность блока 7. Не увеличивая производительность последнего,введение блока 8 да ет возможность освободить канал для обслуживания запросов от блока 6 на время Т за восемь обслуживаемых запросов блока 7 дТ ,5t6 . Если А - производительность блока 7, тогда увеличение производитель ности блока 6 Л F JJ. 3,5-8 / 3.5-Л . В А 100 колебаний в секунд , следовательно F 3,5 1ПП. 350 колебаний в секунду, что составляет от суммарной пропускной cho собности канала, равной 1500 колебаний в секунду - 23. Этот йакт является одним из условий, позволящим подключать к каналу блока 6 диски с V 156 и 312 колебаний в секунду, и более рационально составлять конфигурацию системы ввода-вывода. Формула изобретения 1.-Байт-мультиплексный канал, со. держащий блок микропрограммного управления, блок хранения управляющей информации, блок модификации управляющей информации, блок приоритетов блок .сопряжения с оперативной памятью, блок сопряжения с быстро действующими внешними устройствами, блоки сопряжения с медленно действующими внешними устройствами, причем первый пятый входы-выходы блока микропрогра много управления соединены, соответственно, с первыми входами-выхода ми б.лска модификации управляющей информации, блока приоритетов, блока сопряжения с медленно действующими внешними устройствами, блока хранения управляющей информации, блоков сопряжения с быстро дейстнующими вне ними устройствами, а выход и вход блока микропрограммного управления соединены, соответственно, с входом и выходом блока сопряжения с оперативной памятью, перпый-четаертый входы-выходы которого соединены, соответственно, с вторыми входами-выходами блока хранения управляющей информации, блока.модификации управляющей информации, блока сопряжения с медленно действующими внешними устройствами и блоков сопряжения с быстро действующими внешними устройствами, вход, выход и второй вход-выход блока приоритетов соединены, соответственно, с выходом и входом блока сопряжения с медленно действующими внешними устройствами и с третьими входамивыходами блоков сопряжения с быстро действующими внешними устройстками, третий вход-выход блока хранения управляющей информации соединен с третьим входом-выходом блока сопряжения с медленно действующими внешними устройствами, шестой вход-выход блока микропрограммного управления, четвертый иход-выход блока сопряжения с медленно действующими внешними устройствами, пятый вход-выход блока сопряжения с оперативной памятью, четвертые входы-выходы блоков сопряжения с быстро действующими внешними устройствами являются, соответственно, первым, вторым, третьим входами-выходами и группой входов-выходов байтмультиплексного канала, отличающийся тем, что, с целью повышения производительности, он содержит блок формирования условия блокировки, первый, второй, третий входывыходы которого соединены, соответственно, с третьим входом-выходом блока приоритетов, с пятыми входами-выходами блоков сопряжения с быстродействующими внешними устройствами и с седьмым входом-выходом блока микропрограммного управления, первый и второй входы блока формирования условия блокировки соединены, соответственно, с выходом блока сопряжения с оперативной памятью и с первым выходом блока сопряжения с медленно действующими внешними устройствами. 2. Канал поп. 1,oтлицaющ и и с я тем, что блок формирования условия блокировки содержит peгиcfp меток, регистр признаков обмена данными, триггер памяти отмены совместной работы, триггер памяти конца обмена с оперативной памятью, четыре селектора, элемент И и две группы элементов И, при15ем первый вход-выход блока соединен с первыми входами первого и второго селекторов, элемента И регистра признаков обмена данными, элементов И первой группы, с выходами триггеров памяти отмены совместной работы и конца обмена с оперативной памятью и с первым выходом регистра меток, второй вход-выход блока соединен с вторыми входами элементов И первой группы и с первым выходом регистра меток, первый вход блока соеди нен с вторым, третьим и четвертым входами первого селектора и с первым, вторым входами третьего селектора, третий вход-выход блока соединен с первыми входами элементов И второй группы, с первым входом четвертого селектора и с первым выходом регист|эа меток, второй вход блока соединен с вторыми входами четвертого селектора и элемента И, выход которого и выход четвертого селектора соединены, соответственно, с первым и вторым входами триггера памяти отмены совместного обслуживания, выходы элементов И первой группы соединены с вторым входом регистра признаков обмена данными, первый выход которого соединен с вто;рым входом второго селектора, с третьим входом третьего селектора и с 9 б16 вторыми входами элементов И второй группы, третьи входы которых соединены с выходом триггера памяти конца обмена с оперативной памятью, выход первого селектора и выходы элементов И второй группы соединены соответственно, с первым и вторым входами регистра меток, второй выход которого соединен с третьим входом второго селектора, четвертый вход которого соединен с вторым выходом регистра признаков обмена данными, выходы второго и третьего селекторов соединены, соответственно, с первым и вторым входами триггера памяти конца обмена с оперативной памятью, а третий вход четвертого селектора и четвертый вход третьего селектора соединены с первым выходом регистра меток. I. Источники информации, принятые во внимание при экспертизе 1.Патент CfiJA , кл. 3 0-172.5, опублик. 19б9. 2.Канал мультиплексный ЕС-А012, Техническое описание U53.057.00i.70, 1973, , рис. 8. 3.Авторское свидетельство СССР № , кл. G 06 F З/0t, 1977 (прототип).

Ф// ФигЛ

f r f

Si

S3

f

100

Ly

т

Л

Л/

S3, 49

102

105

/

я

фие.д

Авторы

Даты

1982-11-07—Публикация

1981-05-12—Подача