(54) БАЙТ-МУЛЬТИПЛЕКСНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Байт-мультиплексный канал | 1981 |

|

SU972496A1 |

| Байт-мультиплексный канал ввода-вывода | 1976 |

|

SU656407A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Вычислительная система | 1977 |

|

SU670936A1 |

| Блок-мультиплексный канал | 1979 |

|

SU833076A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения каналов ввода-вывода с абонентом | 1983 |

|

SU1160422A1 |

| Устройство для контроля канала ввода-вы-ВОдА ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU840869A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

Изобретение относится к вычислительной технике, в чаетности к система.м обмена информацией между периферийными устройствами и оперативны.м запоминающим устройством (ОЗУ) ЦВМ, и может быть использовано в системах обмена данными.

Известны каналы ввода-вывода, которые имеют связь с периферийными устройствами посредством нескольких интерфейсов ввода-вывода, обеспечиваемую блоками сопряжения с медленнодействующими и быстродействующими устройствами. Эти каналы состоят из блока местной памяти, блока формирования управля:ои1,ей информации, блока сопряжения с .медленнодействующими периферийными устройствами, блоков сопряжения с быстроде1 1ствующими периферийными устройствами, блока модификации управляющей информацией, блока распределения приоритетов и блока управления.

Однако известные каналы из-за жесткого распределения приоритетов по удовлетворении запросов от блоков сопрял ения с периферийными устройствами иа обмеи информацией с ОЗУ не имеют возможиости обмениваться данны.ми с буфером каналов в управлении ОЗУ (а только непосредствеи110 с ОЗУ), цикл обращения к которому

значительно меньще цикла обращения к ОЗУ. Повыщение быстродействия канала в этом случае невозможно из-за увеличения числа обращения к ОЗУ от канала и, следовательно, увеличения числа конфликтных ситуаций между каналом и центральным процессором по обраи;ении к ОЗУ, что приводит к снижению нроизводительноети всей вычислительной системы в целом.

Наиболее близким по технической сущности и достигаемому эффекту к изобретению является байт-мультиплексный канал, состо иций из блока хранения управляющей )1нформац11и, блока формирования управляющей информации, блока сопряжения с медленнодействующими устройствами, блоков сопрял ения с быстродействующими ; стройствами, блока мо;и1фикации унрав.ijiioiueii информации, блока управления, блока расиределен;1Я приоритетов.

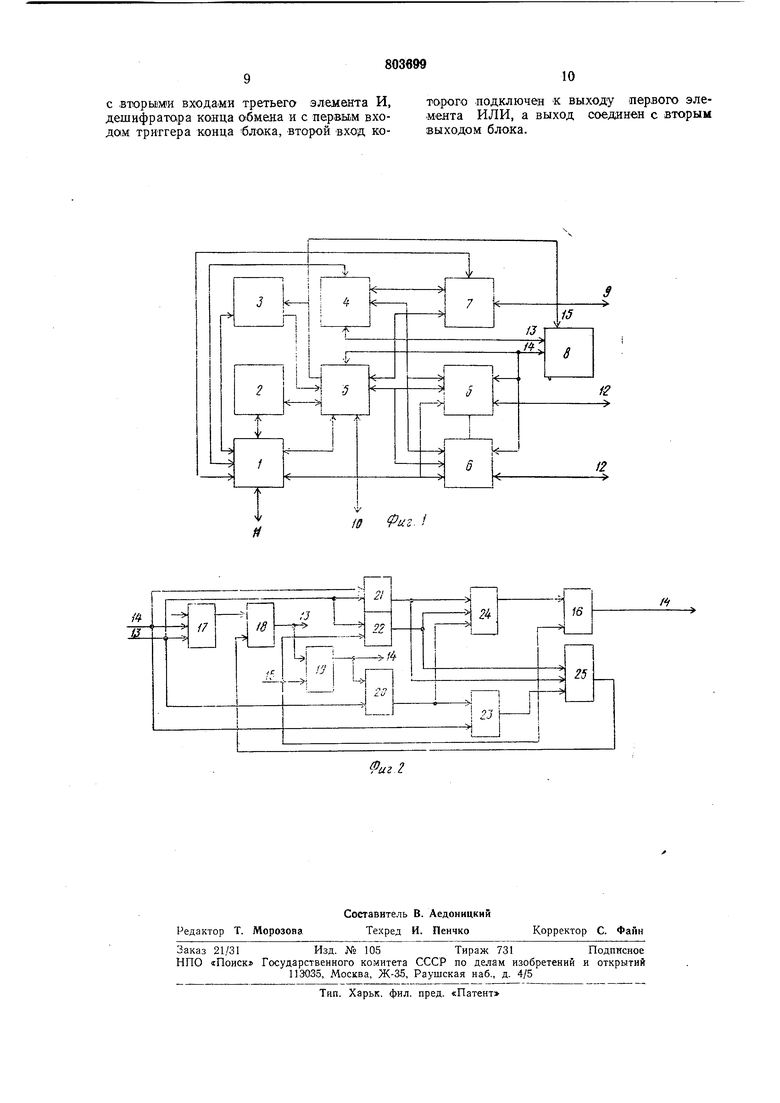

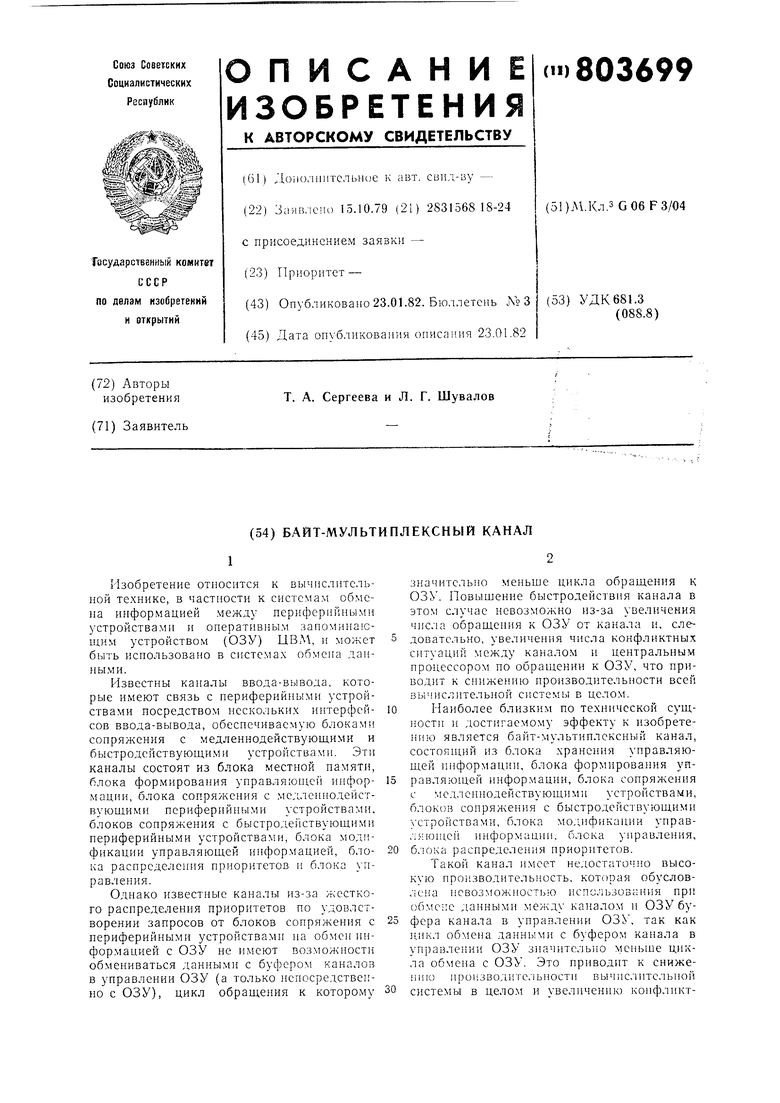

Такой канал имеет недостаточно высокую производительность, которая обуслов.;еиа невозможностью .1ьзования при обмене ;и1нными между каналом н ОЗУ буфера канала в управлении , так как цикл обмена данными с буфером канала в управлении ОЗУ значительно меньще цикла обмеиа с ОЗУ. Это приводит к снижению нрО1 звод гге;1Ыюсти вычис.ште.чьной системы в целом и увеличению коифликтиых ситуациП cждy каналами liB-j.in-iv вода и ucHTjia-ibUbiM процессором IKJ оора щснии к O3i. так как .5иач|1тел)11() воар.астает -iiic.io запросов к or ;-;aiia,-:a гьода-вы вода. Целью нзобретелия является iuMi; ,ение производительности канала. Дель Д Стнгается тем, что в байт-мультип.юксшмй канал, содержащий блок управления, блок хранения ун)а15; Я1ои1,ей иифор.мации, П.юк распре.че.теиия 1 риоритето15, бл-:).-: .o,iiiii.i: кацни уирав;1Я ощей liiKbopMaiur-i, б,,:.;.; форл iipOBaiiii) у правл ;1( .:аи1;:, 6.ТОКИ сопряжения с быстродснсипа ми:м устройствами, б;;ок соп)я 1ач111я с мед.К :нодействующими устройствами, нерв)1Й, второй, третий и четвертыГ 1.(). которого соединеи.. соопнчствеии;; спервыми входами-выходами канала, блока управления, блока распределения приоритетов, бстока фо.р-мирования хиравляю1дей ,И|Иформании, при это.м ВТорой. третий, )тый, пятый и икчтой ход1 1-ви1ходы б.юка ()ормироваиня управляющей инфор.мации соед 1нены соотиетствеиио с вторыми входа1ми-выходам1 ка.иала, блока xiipaB.ieiiiiH, с jiepBBiMn ;зходал111-;-и 1хода и блоков сопряжения с бв1стролейст; К) устройствами, блока .модиф.икапии уира ляюишй инфо рмапии и блоха хранеп.ия упра,вля1ОН1;ей .рмании, второй вход-1 ыход которого соединен с треть.им ()м-|вв ходом б.юка 1 равлеиия, четвертый, , шестой и седьмой вхоДВ1-1ВЫХО.ДЫ блока т1.равлепия .чодключенг. ссч)тветст;;снно к третьем} вход.-ныходу канала, к 1ггорым входам-выходам блоков сонря/ сепия с устройства .ми, б лежа модифика ;;: . яю1ней информации, блока laciM HpHopiiTciOB, трети; cf)e.TH4(4i с третьими и б;юкоз соиряжеиия с бьк устроаспшми, че;аирть;;. б;юк()П сопряжения с хстройствами соед;п ень; с дамилимходамн хана.ча, б.. ,тепия обмеиом, первыи j)Oio соедпнен с :егверт,:м .х б.юка распределения ириоритсТ); ВХОД-15ЫХОД соединен с се.IBM б::ока. (Ьормироваиия унра.нляк; мацией и е питыми входам а-вы ков ео11ря;кения г бь;е-:ч1оте стротсг:-;ам;, 1 nei i : Ч;а: тому выходу блока tj ч.:: 4i;Kiii.1яклней .;а1ЦИ 1. В;1ок управле П;я ,;: а;:: группу лемецтов И, н:)и.ч1аков, .Teujntpjiaroj) i( ooMeiia, : :р -.аи-аа га )i, Tpnrret) гсоица блока и jni. 11е)и1-:й 13КОД блока соединен с пер31 В И входами i vyiiiiN злемеитов м. in.nJiiiго, второго и трсльего элементов П. ) .ход п.юка соедчнеп с HeiiBijiM входом четBeDToro э.1е с-чта 11 pnio ;1ем(.чгга М и П)упп1)1 э.еменчов И, выход которой соедииеи с первым входом реlaKTpa иризнако, BT())iiiM вход(.)М подкла.-cHHoio к вых().ду второго элемеита ИЛИ, а В1яходд)1 к иервох;у (,.ту бл(.1ка и иер1.;)1у ixo. длЧ1Л фрат()ра кс,ч1иа об.мена, ()Д которого еоедннеи с вторг-:м выходом б,ока и вторь Л входом первого а,те.еита И. iii.ixo.T г.ервого элемеита И соединен с ia,-|Bb M вхо.том HCjJBOro э.ю.меьда ИЛИ и вторыл; вхо.чом четвертого И, выХ:)Д кото1)ого нодк;::очеи к первому вн. -:)лемента 11ЛИ, 1Д,1ХОД второго леMcHia И еоеднне с вторыми входами перlifjro и BTot)()r(j элементе 1ЛИ, вь:ход третьего элемента И соединен с третьими | ходал;н iiejJBtJio и второго элементов ИЛИ. Tpeiani вход блока еоедииен с вто)ым;| входами третве1о элеме1гга И, деи нфрато)а a.)iHU . и с нерв1;1м входо.м триггера K.aiaa блока. BTopoii вх(;; KOTopoio нод;s.:;oKii к ().чу 1е|)ь:ао элемента ИЛИ, а ;;ь:ход соедпне:; с вто)ым В)ходом блока. Иа фиг. 1 изображена б.чок-ехема байтм а1ьтин.и-ксного кана,1аа, iia фиг. 2 (ручкпиона.11)11ая i.ioKa унрав.чення обм(.ч;Ол. ЬаГгг-.,1ьтиилексиыП капал соде)Ж11Т n.K.iK Д1рал5.. блок 2 храненг:я унранляк.) ииформации, б.(;к о модификации ч:рар..1як) информад1.п1, блоь; 4 раснредг. 1, ндиорите roii, п.ия П (р()рмнр1Ч5аи1;я aipaB. иифор :аи.1П. б.чоки li еонря/ чс1;; я с быетр()дейст1пч(лицми устройства.ми, блок 7 соиряжения с медлеииодейс1и чо1пи.гн хстройетвами, блок 8 управлеиия ; бме1:к)м н имеет в.ходы-выход 9-12 и упразляюшие шины 13-15. B;ioK ун)ав;1ения (Ч)держит |)иггер И) 1().чца б,1ока. ;р) элементов 17, рсччкмч 8 HpH.iHaKOB, ден11 фратор 19 .а обмена, И 20-23, э,1емент) И.ЧИ 2-1 11 25. е ) канала в управлешп (;,. ре/)им б,10ковО Ч1 обмена, оргапиачякш с.1елу.он1нм образо :. Ипс.те удов.четво|)ечньч на об.ич1 г.юво.м ог блока I) еогласно нриевоенио у npnopj:-;ч б.током -1 (установка соответетпуоше ; хровня нрно;)ите: а., после чсчо оборудование 6:iOKOB 1-5 астраиваетея на (j6e4y ааначче а1о;5.1(творяел10го :ianpoea) снгна..; а:;чд|ака .:ом1,ч1а .чанн: мн ич блока G иеиг ;ал нрио|)итета из б,:к)ка 4 иостуН а io i cooTiicTCTBe Н1 JO но унрав,;:Я 01ННМ Н1Ич. 11 и 1о в б.иж управ.-ения обмено.:, i ч,- срабатывает один из э,чем(Ч1ТОВ И 17, по ач1а; е 5ыхо.;а кот(Ч1ого стана1;.11 вается аачьа регистра 1 нризчагдл б/юкового (Ч;а, сооТ1к-тст1 ч(линй сигналу ypOBiiH аритега, яр.ляется HpiiaiiaKOM блокоi (rpyiHioBoro) обмена .aainiiaMH б.юка ij е . Выходы е регистра 18 иостукиот ги) уиргл5ля1()иич( тине 13 в блок 4, управ.ляя установкой сигналов уровней приори-тета так, что до тех пор, пока установлен один из уровней регистра признаков, возможна при удовлетворении запроса уста:новка только соответствующего уровня приоритетов, удовлетворение всех остальных запросов, даже старших, т. е. установка всех остальных зфовней приоритетов согласно присвоенному приоритету, блокируется.

Таким образом, при «аличии сигнала с perHCTipa признаков организуется подряд несколькими словами данных блока 6 с ОЗУ, т. е. Производится обмен по одному .массиву данных, что дает .возможнОСть использовать буфер канала в ОЗУ.

Блок 6, имея буфер для вакоплвния да,н,ных, в общем случае первоначально уста,навл1И1вает запросы .на обмен дайными, когда заполнение буфера СПК 1поз1воляет принять (|П,ри операции считывания из ОЗУ) или выдать (При операции записи IB ОЗУ) количество слов данных яе меньшее полного объема буфера канала ОЗУ (.например, четыре).

При удовлетворении лервого запроса от блока 6 на обмен словом данных блоком 4 согласно присвоенному приоритету устанавли вается соответст1ву ощий разряд регистра 18 Признаков блокового обмена. Обмен словом данных с ОЗУ производится под управлением блока 5 1ПО шине 10. После заВершеНИя обслуж1И1ва,ния первого запроса от блока 6 (в общем случае завершения oi6мена с ОЗУ), для которого установленгарйзнак блокового обмена, сразу же формирук т новый запрос на обмен следующим словом данных, .который немедленно удовлетворяется независимо от наличия других запросов, даже тех, которые являют ся старшими при жестком удовлетворении запросов.

Следовательно, нарушается жесткое распределение IB удовлетворении запросов согласно присвоенному приоритету при .на.Л1ИЧ.ИИ сигнала с регистра 18 признаков и происходит обмен одним |М..м данных, что дает возможность обмениваться данными с (буфером каналов в удравлении ОЗУ. Такой обмен продолжается до тех пор, пока не сбросится указатель блокового обмена регистра приана;ков и не возникнет одно из условий на входе элемента ИЛИ 25, которого управлЯет сбросом регистра признаков.

Условия сброса регистра признаков возникают При )полном за:пол.нен1ии (рассасы вании) буфера канала в ОЗУ, по завершении обмена данными по инициативе канала ИЛ.И периферийно;го устройства, при Возник-новении экстрен.ны-х ситуаций (например, сбойных).

Заполнение (рассасывание) буфера канала в управлении ОЗУ оеределяется дешифратором 19 конца обмбна с буфером

канала: при .наличии признака блоков-ого Обмена, поступающего на дешифратор с выхода регистра 18 признаков, а,нал.изируется aaipec данных в момент формирования запроса на Обмен да:н ным1И в ОЗУ, поступающий по управляющим шинам 15 из блока 5.

При адресе данных, соответствующем полному заполнен1ию (рассасыванию) буфера ,канала в ОЗУ, происходит обращение в ОЗУ на освобождение (заполнение) буфера; на выходе дешифратора 19 возникают сигналы, поступающие по шине 14 в блок 6 и на элемент И 20, с выхода которого сигнал поступает на один из .входов элемента И 23 и на один из 1ВХОДОВ элемента ИЛИ 24, выход которого управляет установкой триггера 16 конца блока. Сипнал с трИггера конца блока по шине 14 поступает в соответствующий блок 6. Совокупность сигналов с двшифратора 19 и триггера 16 на шиле 14, указывающая на полное заполнение (рассасыванйе) б фера канала в управлен1ии ОЗУ, дает возможность, если исчезли условия первоначальной установки запросов на обмен данными, ирек;ратить серию заПросов на обмен данными из блока 6, который сбрасывает сигнал признака обмена данными.

При отсутствии признака обмена данными от соответствующего блока 6, поступающего по управляющей ШЕне 14 на элемент И 23, и наличии сигнала на выходе элемента И 20 возникает сигнал на выходе элемента И 23, который через элемент ИЛИ 25 сбрасывает .регистр 18 признаков. Блоковый обмен данными завершается. Вступает в силу удовлетворение зап.росов согласно присвоенному ттриор.итету. Если условия первоначальной установки заотросов не .исчезли в iблoкe 6 при поступлеяии сигналов по ш.ине 14, блок 6 не сбрасывает сигнал признака обмена данными, за1просы на обмен данными «е блокирует. В этом случае не срабатывает элемент И 23 и сброса регистра 18 признаков не П|р1оисходнт. Блоковый обмеи продолжается уже с обновленным буфером каналов в управлении ОЗУ.

Завершйние блокового обмена данными по инициативе канала (при отсутствии сбойных ситуа ций) происход ит при исчерпа.нии счета данных в текуШЬМ управляющем слове канала. Сигнал нулевого счета данных поступает из блока 5 по шине 15 на элемент И 22 при наличии сипнала уравил приоритета блока 6 из блока 4, поступающего по управляю1щей шине 13 яа другой вход элемента И 22, на выходе элемента И 22 возникает сигнал, поступаюший на входы элементов ИЛИ 24 и 25. Уста.навливается сигнал на выходе триггера 16 конца блока, который поступает по шине 14 В блок 6, где безусловно сбрасывается Сигнал признака обмена даннькми и блокируются запросы на обмен данными. Сигнал управления КОНЦО.М Масива по шине 14 П1роходит в

блок 5, формирующий сигнал КОНЕЦ МАССИВА .при поступлении которого в управление ОЗУ по шине 10 л;ри организации обращения в ОЗУ происходит освобождение буфера канала. Сигнал с выхода элемента ИЛИ 25 сбрасывает регистр 18 признаков. Блоковый обмен данными завершается. Таким о&разом, сигнал КОНЕЦ МАССИВА при бЛ|ОКО1ВО,м обмене выдается не при каждом обращении IB ОЗУ, а по завершении блокового Обмена.

Блоковый обмен даЕны,ми также прекращается по завершении обмена данными по инициативе периферийного устройства. В этом случае сигнал завершения операции периферийным устройством из блока i6 поступает по управляющей штине 14 ,на вход элемента И 21; ори «аличии сигнала уровня приоритета блока 6 из блока 4, посту.паю1щего по упр.авляющей |Щ:ине 13 на другой вход элемента И 31, воавикает сигнал, который отрабатывает так ж-е, как сигнал с выхода элемента И 22. Регистр 18 признаков сбрасывается. Блоковый обмен данными заве рщается. Вступает в силу удавлетворение запросов согласно присвоенН|0,му приоритету.

Выдача сигнала по щине 14 на формирование сигнала КОНЕЦ МАССИВА всегда производится пр1И наличии сигнала уровня приоритета блока 6, что дает возможность не оргайИ|Зовы1вать дополнительный запрос в ОЗУ на установление сигнала КОНЕЦ МАССИВА для освобождения буфера канала в управлении ОЗУ (при операции ЧТЕНИЕ буфер лереяисывается в ОЗУ, при операции ЗАПИСЬ сбрасываются признаки занятости буфера), а представлять сигнал КОНЕЦ МАССИВА во время организации запроса по обмену данными.

Введение узла блокового обмена позволяет повысить производительность канала в вычислительной системе при заданной пропускной спо.собности ОЗУ и вычлслительной системы в целом 3ia счет уменьшения числа 1непосредствбнных обменов данными с ОЗУ и снижения числа конфликтных ситуаций по обращению к ОЗУ канала и центрального процессора.

Формула изобретения

блока распределения приоритетов и блока формирования управляющей информации, второй, третий, четвертый, пятый и шестой входы-выходы которого соединены соответственно с вторыми входами-выходами канала, блока управления, с первыми входамивыходами блоков сопряжения с быстродействующими устройствами, блака модификации управЛЯющей информации и блока

хранения управляющей информации, второй вход-выход KOTOiporo соединен с третьим входом-выходО|М блока управления, четвертый, пятый, шестой и седьмой 1входывыходы которого соединены соответственно

с третьим входом-выходом канала, с вторыми-выходами блоков сопряжения с быстродействующими устройствами, блока мод ификации уп1ра1вляющей информа|Ции, блока р,ас/пределения приоритетов, третий входвыход которого соединен с третьими входами-выходами блоков сопряжения с быстродействующими устройствами, четве;ртые входьивыходы которых соединены с четвертыми входа ми-выходами канала, от лич а ю щ и и с я тем, что, с целью увеличения производительности канала, в него введен блок управления обменом, первый вход-йыход которого соединен с четвертым входомвыходом блока раопределен|ИЯ (приоритетов,

второй вход-выход соединен с седьмЫ|М входом блока форимир01вания управляющей информации и с пятыми входамичвыходами блоков сопряжения с быстродействующими устройствами, третий вход подключен к пятому выходу блока формирования управляющей информации.

1

Авторы

Даты

1982-01-23—Публикация

1979-10-15—Подача