2. Система по п.1, отлича ющ а я с я тем, что формирователь линейного цифрового сигнала содержит семь элементов запрета, четыре элемента ИЛИ, линип задержки, инвертор, элемент И И триггер, первый выход которого соединен с первым входе первого элемента запрета, первым входом второго элемента запрета и первым входом третьего элемента запрета, вто рой вход которого соединен с первьда входом четвертого элемента запрета и первым входом первого элемента ИЛИу второй, вход которого соединен с выходом пятого элемента запрета, первый вход которого соединен с вторалм выходом триггера, вторым входом четвертого элемента запрета и первым входом шестого элемента запрета, второй вход которого соединен с вто рым второго элемента запрета и первым входс второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента запрета, второй вход которого соединен с вторьм входом пятого элемента запрета, причем выход элемента запрета подключен к перв.сму входу элемента И, второй вход которого соединен с выходом линии задержки, вход которой соединен с выходом третьего элемента ИЛИ и входом инвертора, выход которого подключен к первому входу седьмого элемента запрета, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами третьего и. шестого элементов запрета, а выходы второго и четвертого элементов запрета подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход элемента И является выходом формирователя линейного цифрового сигнала, первьм входом КОТОРОГО является вход триггера, вторым входом - первый вход четвертого элемента запрета и второй вход шестого элемента запрета.

3. Система по п.1, отличающаяся тем, что, декодирукйций блок содержит пять элементов запрета, два элемента ИЛИ, инвертор, три элемента задержки, два элемента И, триггер, элемент памяти и. делитель частоты, выход которого соединен с первым входом элемента памяти, второй вход которого соединен с выходом первого элмента ИЛИ, первый вход которого соединен с третьим входом элемента памяти, с первыми вхсщами первого и второго элементов запрета, с выходом триггера, с выходом первого элемента И и входом первого элемента задержки, выход которого подключен к первому входу третьего элемента запрета, второй вход которого соединен с выходом второго элемента зад€гржки, вход которого соединен с .входом инвертора, входом третьего элетпента задержки, первым входом первого элемента И и выхо.дом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого, элемента запрета, первы вход которого соединен с первым выходом триггера, второй выход ко торого подключен к первому входу пятого элемента запрета, выход которого соединен с вторым входом второго элемента ИЛИ, выход инвертора соединен с первым входом второго элемента И, второй вход которого соэдинен с выходом третьего элемента запрета, второй вход первого элемента ИЛИ подключен к выходу второго элемента И, вторые входы четвертого и пятого элементов запрета соединены с вторыми входами соответственно первого и второго элементов запрета, выходы которых являются первым выходом декодирующего блока, .вторым выходом которого является выход элемента памяти, вторые входы первого и второго элементов запрета являются первым входом декодирующего блока, вторым входом которого является вход делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство для исправления ошибок | 1988 |

|

SU1547081A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство радиосвязи | 2019 |

|

RU2713921C1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство для передачи дополнительной низкоскоростной цифровой информации по каналу связи с дельта-модуляцией | 1987 |

|

SU1494245A1 |

1. СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВОЙ ИНФОРМАЦИИ, содержащая на передающей стороне источник основной информации, источник дополнительной информации, первый и второй выходы которого соединены соответственно с nepBtw и вторым входами блока памяти, а на приемной стороне преобразователь линейного цифрового сигнала, приемник основной информации и приемник дополнительной информации, отличающаяся тем, что, с целью повышения помехозащищенности, введены на передающей стороне формирователь линейного цифрового сигнала, выход которого соединен с треть им входом блока пагляти, выход которого соединен с первым входом формирователя линейного цифрового сигнала, второй вход- которого подключен к выходу источника основной информации, а на приемной стороне введен декодирующий блок, первый вход которого соединен с первым выходом преобразователя линейного цифрового сигнала, второй выход Которого соединен с вторым входсм декодирующего блока, первый и второй выходы j которого подключены соответственно у| к входам приемников основной и дополнительной информации. О1 СХ) о 00 . 1

Изобретение относится к электро связи и может быть использовано для передачи и приема цифровой информации.

Известно устройство для передачи и приема цифровой информации, содержащее на передаю цей стороне передатчик цифровой статистической системы

передачи, а па приемной стороне приемник цифровой статистической системы l .

Недостатком устройства является низкий коэффициент использования линейного цифрового видеотракта.

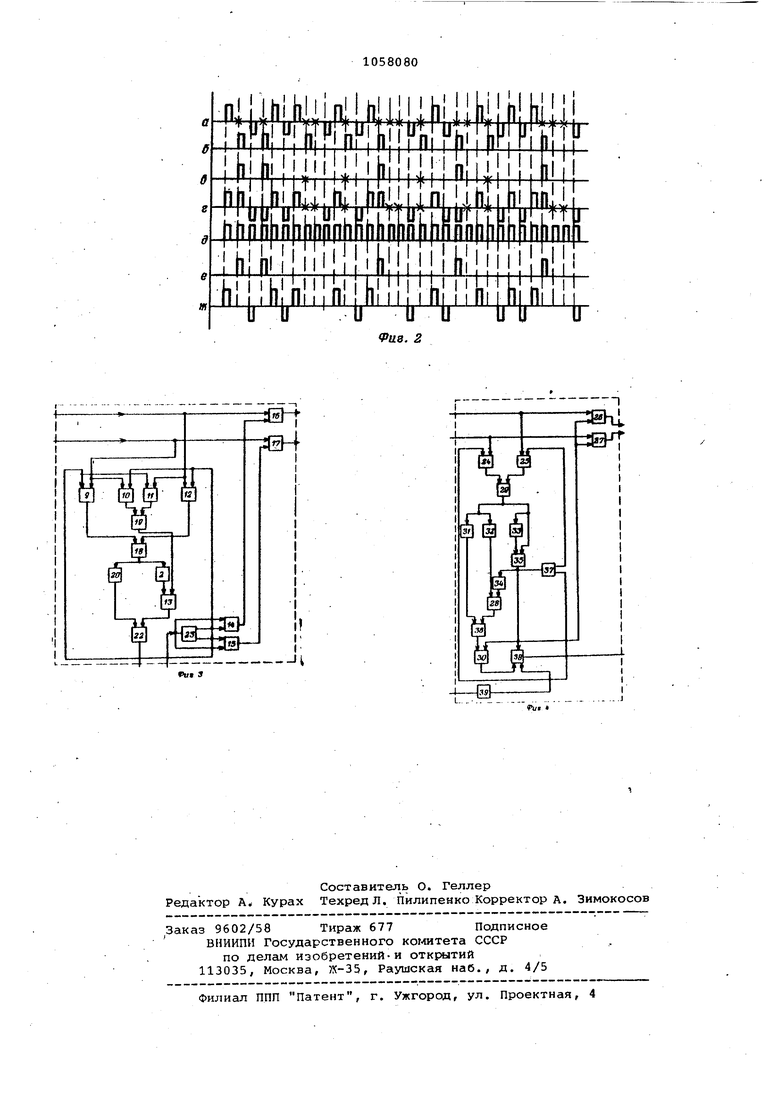

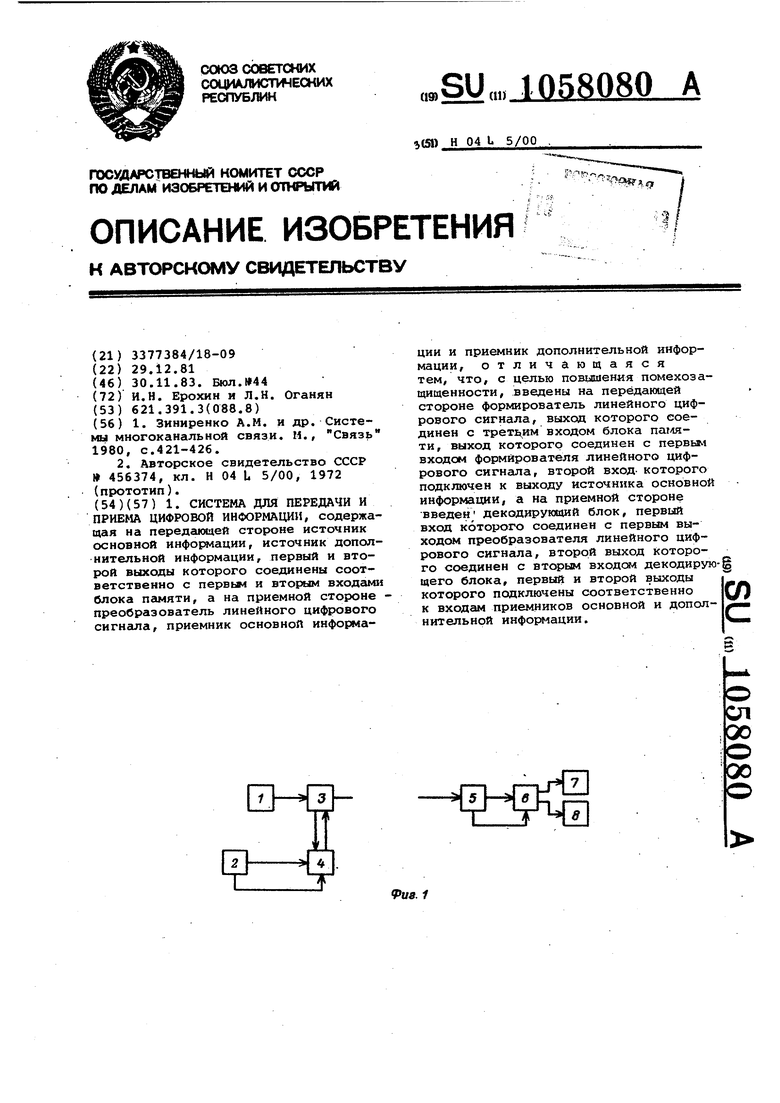

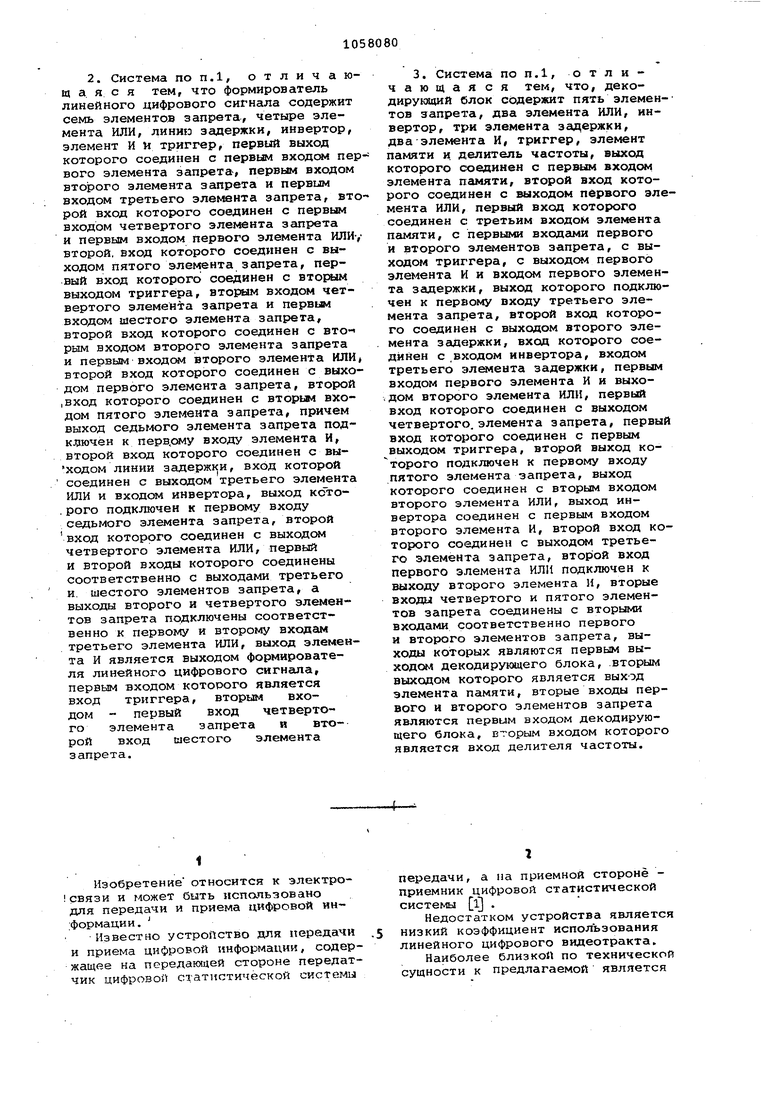

Наиболее близкой по технической сущности к предлагаемой является система, содержащая на передающей стороне источник основной информа- . ции, источник дополнительной информации, первьи и второй выходы которого соединены соответственно с первым и вторым входам блока памяти а на приемной стороне - преобразователь линейного цифрового сигнала,, приемник основной информации и прием ник дополнительной информации fZj . Однако известная система обладает низкой помехозащищенностью. Цель изобретения -. повышение помехозащищенности. Поставленная цель д 3стигается тем что в систему для передачи и приема цифровой информации, содержащую на передающей стороне источник основ ной информации, источник дополнитель ной информации, первый и второй выходы которого соединены соответственно с первым и вторым входами блока памяти, а на приемной,.стороне преобразователь линейного цифрового сигнала, приемник основной информации и приемник дополнительной информации , введены на передакнцей стороне формирователь линейного цифрово го сигнала, выход которого соединен с третьим входом блока памяти, выход которого соединен с первым входом формирователя линейного цифЕювого сигнала, второй вход которого подклю чен к выходу источника основной информации, а на приемной стороне введен декодирующий блок, первыйвход которого соединен с первым выходом преобразователя линейного цифрового сигнала, второй выход которого соединен с вторым входом декодирующего блока, первый и второй выходы которо го подключены соответственно к входам приемников основной и дополнител ной информации. При этом формирователь линейного цифрового сигнала содержит семь элементов запрета, четьяре элемента ИЛИ линию згшержки, инвертор, И и триггер, первый выход которого сое динен с первым входом первого элетлен та запрета, первым входом второго элемента запрета и первым вкоцсм тре тьего элемента запрета, второй вход которого соединен с первьал входом четвертого элемента запрета и первьм входом первого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента запрета, первый вход которого соединен с вторым выходом триггера, вторым входом четвертого элемента запрета и первым входо(4 шестого элемента запрета, второй вход которого соединен с вторлм входом второго элемента запрета и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента запрета, второй вход которого соединен с вто рым входом пятого, элемента запрета, причем выход,седьмого элемента запрета подключен к первому входу элемента И, второй вход которого соединен с выходом линии задержки, вход которой соединен с выходом третьего элемента ИЛИ и входом инвертора, выход которого подключен к первому входу седьмого элемента запрета, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами третьего и шестого элементов запрета, а выходы второго и четвертого элементов злпрета подключены соответственно к первому и второму входам третьего элемента ИЛИ., выход элемента И является выходом формирователя линейного цифрового сигнала, первый входом которого является вход триггера, вторым входом - первый вход четвертого элемента запрета и второй вход шестого элемента запрета. Кроме того, декодирующий блок содержит пять элементов запрета, два элемента ИЛИ, инвертор, три элемента задержки, два элемента И, триггер, элемент памяти и делитель частоты, выход которого соединен с первьпм входом элемента памяти, второй вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с третьим входом элемента памяти, с первыми входами перв.ого и второго элементов запрета, с выходом триггера, с выходом первого элемента И и входом первого-элемента задержки, выход которого подключен к первому ВХОДУ третьего элемента запрета, второй вход которого соединен с выходом второго элемента задержки, вход которого соединен с входим инвертора, входом третьего элемента задержки, первым входом первого элемента И и выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента запрета, первый вход которого соединен с первым выходом триггера, второй выход которого подключей к первому входу пятого элемента запрета, выход которого сое- ; динен с вторым входом второго элемента ИЛИ, выход инвертора соединен с первым входом второго элемента И, второй вход которого соединен с выходом тре.тьего элемента запрета, второй вход первого элемента ИЛИ подключен к выходу второго элемента И, вторые входы четвертого и пятого элементов запрета соединены с вторыми входами соотв€;тственно первого и второго элементов запрета, выходы которых являются первымвыходом декодирующего блока, вторым выходом которого является выход элемента памяти, втоцше входы первого и второго элементов запрета являются первьм входом декодирумцего блока, вторым входам которого является вход делителя частоты. На Фиг.1 изображена структурнгм электрическая схема предлагаемой системы; на Фиг.2 - временные лиагргтмы; на фиг.З - структурная элек рическая схема формирователя линейного цифрового сигнала; на фиг.4 то же, декодирукхцего блока. Система дЛя передачи и приема цифровой информации содержит источник 1 основной информации, источник 2 дополнительной инфор1- ации, формитрователь 3 линейного цифрового сигHEUia, блок 4 памяти, преобразовател 5 линейного цифрового сигнала, декодирующий блок б, приемник 7 основ ной информации и приемник 8 дополни тельной информации. Формирователь линейного цифровог сигнала содержит элементы 9-15 запр та, элементы ИЛИ 16-19, линию 20 задержки, .инвертор 21, элемент И 22, и триггер 23. Декодирующий блок содержит элеме ты 24-28 запрета, элементы ИЛИ 29 и 30, инвертор 31, элементы 32-34 з держки, элементы И 35 и 36, триггер 37, элемент 38 памяти, делитель 39 частоты. Система работает следующим образом. На передающей стороне на вход фо мирователя 3 линейного цифрЬвого сигнгша поступает сигнал фиг.2а) о источника 1 основной информации. Дл конкретности иллюстрации рассматривают случай передачи последовательности символов дополнительной двоич яоЛ информации 110010101..., поступающей на первый вход блока 4 памяти с тактовой частотой 1| от источ ника 2 дополнительной инфорг4сщии. Формирователь 3 линейного цифров го сигнала выбирает бестоковый такт вый интервсш, следующий первьй«1 за импульсом сигнала (фиг.2а), формирует сигнёш считывания (фиг.2б) в этот интервал времени, обеспй 1ивая считывание очередного символа дополнительного двоичного сигнала (фиг.2в) с блока 4 памяти на формирователь 3 линейного цифрового сигнала. Последний формирует импульс с по лярностью предшествующего ему импул са сигнала (фиг.2а) при передаче первого из возможных значений симво л а дополн«ПельноП двоичной информации (в предлагаемом варианте 1) , формирует бестоковую посылку при пе редаче второго из возможных значений символа дополнительной двоичн 1птформации (в предлагаемом варианте О) и обеспечивает передачу образованного линейного сигнала (фиг.2г) :в линейный цифровой тракт. Причем формироват 2ль 3 линейного цифрового сигнала для передачи каждого очередного символа дополнительной двоичной информации выбирает первый по счету бестоковый тактовый интервал В ближайшем временном отрезке, следующим за таким иглпульсом сигнала (фиг.2а), полярность которого противоположна полярности последнего предшествующего ему импульса, сформ{фованного при передаче первого из возможных значений символа дополнительной двоичной информации. На прие1 шой стороне линейный цифровой (фиг. 2г) поступает на преобразователь 5 линейного цифрового сигнала, с выходов кото1юго двоичная информация и сигнал тактовой частоты (фиг.2д) подаются на входы декодирующего бЛока 6. Последний в процессе последовательного ангшиза линейного сигнгша каждый импульс, полярность которого повторяет полярность непосредственно предшествующего ему И14пульса, опознает как символ дополнительной двоичной инфсчрмацни, имеющий первое из возможных значений (в предлагаемом варианте 1), а каждую бестоковую посылку, следующую первой по счету за шшульсом линейного сигнала с полярностью, противоположной полярности последнего предшествующего ему иМпульса;, опознанного при приеме как символ дополнительной двоичной информации, имеющий первое из возможных значений, опознает как символ дополнительной двоичной информации, иг еющйй второе из возможных значений (в предлагаемом ва:рианте О). Таким образом, на втором выходе декодирующего блока 6 получают последовательность (фиг.2е) аналогичную дополнительной двоичной информации 110010101..., считываемую с частотой i в приемник 8 дополнительной инфо :жации. Декодирующий блок 6 в процессе анализа принимаемого линейного сигнала вместо каждого импульса, полярность КОТО1ЭОГО повторяет полярность непосредственно предшествующего ему импульса, формирует бестокбвую посылку основной двоичной информации, остальные символы оставляя без изменений. Таким образом, на втором выходе декодирующего блока 6 получают основную двоичную информацию (фиг. 2ж) поступающую в приемник-7 основной информации. На местах определенных бестоковых тактовых интервалов основной двоичной информации передается дополнительная двоичная информация.

Формирователь линейного цифрового сигнаша работает следующим образом.

в исходном состоянии на входе триггера 23 сигнал отсутствует и с его второго выхода на первый вход элемента 15 запрета и на вторые входы элементов 9 и 11 запрета подается 1. Линейный сигнал поступает на первый вход элемента 11 запрета, на вторые входы элементов 10-12 запрета и на первые входы элементов ИЛИ 16 и 17 поступает 1.

1 сигнала поступает на первый вход элементачИЛИ 16 и одновременно на вторые входы элементов 11 и 12

запрета, вследствие чего

через

элемент 12 запрета и элемент ИЛИ 18 подается на линию 20 задержки, а через элемент 11 запрета и элемент ИЛИ 19 - на втор-ой вход элемента 13 запрета.

В следующем тактовом |1нтервале сигнала с частотой i следует О, который инвертируется в инверторе 21 в 1 и одновременно с 1, поступающей из линии 20 задержки, подается через элемент И 22 на третий вход блока 4 памяти, в котором с частотой i записывается дополнительная цифровая информация. Если в момент прихода считывающего импульса в блок 4 памяти записана 1, то последняя поступает на вход триггера 23 и через элемент 14 запрета и элемент ИЛИ 16 в линию. Триггер 23 переходит в другое состояние и 1 с его первого выхода поступает на первые входы элементов 10,12 и 14 запрета. В результате этого 1 сигнала проходит череэ элемент 9 запрета и элемент ИЛИ 18 на вход линии 20 задержки. В следующем тактовом интервале сигнала с частотой iт- следует О, который инвертируется в инверторе 21 в 1 и одновременно с 1, поступающей из линии 20 задержки, подается через элемент И 22 на третий вход блока 4 памяти. Если в момент прихода считывающего импульса в блок 4 памяти записана 1, то последняя поступает на вход триггера 23 и через элемент 15 запрета и элемент ИЛИ 17 в линию. Триггер 23 переходит в другое состояс его второго выхода постуние и

пает на первые входы элементов 11 и 15 запрета и на второй вход элемента 55 9 эгтрета. Если после 1 сигнала следует снова 1. сигнала, то последняя через открытый элемент 10 (И) запрета и элемент ИЛИ 19 поступаетна второй вход элемента 13 запрета, ,Q и 1 сигнала не поступает на третий вход блока 4 памяти через линию 20 задержки и элемент И 22.

Декодирующий блок работает следующим, обра зом.

В исходном ,состоянии на входе .триггера 37 сигнал отсутствует и 1 с его второго выхода подается на первый вход элемента 24 запрета. 1 через открытый элемент 25 запрета и элемент ИЛИ 29 поступает на элементы 32 и 33 задержки. Если в следующем тактовом интервале сигнала следует 1, то последняя вместе с задержанной 1 поступает через элемент И 35 на вход элемента 34 задержки, триггера 37, элемент 38 памяти и элемент ИЛИ 30 и элементы 26 и 27 запрета. Последовательность импульсов с выхода элемента И 35..является информационной. 1, задержанная в элементе 34 задержки на один такт частоты fтподается на первый вход элемента 28 запрета, чем предотвращает образование ложного импульса записи цепочкой выделения О дополнительной двоичной информации., поступающая с выхода элемента И 35 на первые входы элементов 26 и 27 запрета, исключает 1 дополнительной двоичнрй информации из последовательностей, и образуется последовательность, поступающая на приемник 7 основной двоичной информации,, поступившая На триггер 37, переводит последний в другое состояние. Если после 1 следует О, то последний выделяется инвертором 31, элементом 32 задержки, элементом 28 запрета и эле-, ментом И 36, ив элементе 38 памяти записывается О.

Следовательно, О дополнительной двоичной информации выделяются из последовательности до момента выделения 1 дополнительной-цифровой информации, после чего выделяются символы (О и 1) дополнительной двоичной информации из последовательности.

С элемента 38 памяти дополнительная двоичная информация считывается тактовой частотой i-J. , которая образуется делителем 39 частоты, на приемник 8 дополнительной двоичной ин формации.

Во избежание потерь дополнительной двоичной информации необходимо выполнять соотношение тактовых частот основного двоичного сигнала i|. и дополнительного IT s пределах

ч;41т,

где Ml - целые числа.

Таким образом, передача дополнительной двоичной информации в нулевы тактовых интервалах основной двоичной информации приводит к повышению среднего количества единпц в линейнсм цифровом сигнале, что вызывает снижение дисперсии фазовых дрожаний D (у импульсов линейнргс-) сигнала.

nlilliLh.

nl hi

tt

Wiift

w

&

1

1ТЖ

I I I и I I , I

11 hi I III I I ifiLTi Lti

ai

Ь

tr

П

Wyi

ihSinMir

I г I I т I I

irr

,1, MhiLiiiLi I,

Ml I I П| III 11 Hi I

11 th III I I III I Ml I I I

|j У b Ij

fftfn

Wr

i|| П h IH-I.1 I I L

li

in I n I

11

1

т4й1

шш

-i4iH

w

т

м1ф

ШЦ

1

1

ЙОг

PU8. 2

(Vi 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Зиниренко A.M | |||

| и др | |||

| Системы многоканальной связи | |||

| М., Связь 1980, с.421-426 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ передачи двоичной информации | 1972 |

|

SU456374A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-30—Публикация

1981-12-29—Подача