Изобретение относится к контрольно измерительной и вычислительной технике и может использоваться для функцио нально-динамического контроля инте.тральных логических структур. Известно устройство для контроля электронных схем цифровых вычислйтель HEJx машин, содержащее блок ввода, регистр задания, блок сравнения, анализируемую схему, блок управления, блок индикации, а также блоки преобразования, эталонов и компаратора - преобра зователя I . Недостатками устройства являются невозможность осуществления функционально-динамического контроля, т.е. контроля задержки распространения .сигналов в проверяемых узлах, отсутствие возможности проверки большого числа узлов ЦВМ или же больших интегральных схем (БИС), имеющих синхронную организацию, т.е. требующих подачи на свои входы одного или нескольких импульсных сигналов. Известно устройство для контроля амплитудно-временных параметров логических сигналов, содержащее блок ввода информации, блок управления, формирователь входных сигналов, блок сравнения, блок памяти, анализа и регистрации, блок считывания, линию задержки, генератор стробсигнала, блок установки onopHfcix напряжений, источ--. ник опорных напряжений 2. Недостатком устройства является отсутствие возможности контроля интегральных узлов с синхронной организацией, а также невозможность подачи импульсных сигналов (или серии им- пульсов) с максимальной рабочей частотой работы проверяемых блоков. С целью расширения функциональных возможностей в устройство для контроля логических блоков, содержащее блок ввода информации, соединенный с формирователем входных сигналов, который подключен к входным зажимам испытуемого блока, к выходным зажимам котопого подсоединен первый вход блока сравнения, соединенный с блоком памяти, анализа и регистрации, вход блока установки опорных напряжений соединен с источником опорных напряжений, а выход подключен к второму входу блока сравнения, к третьему входу которого подсоединен генератор стробсигнгша, связанный с линией задержки, и блок управления, вход которого связан с блоком ввода информации, а выходы - с линией задержки, генератором стробсигнала и блоком считьтания, соединенньп«1 с вторым входом формирователя входных сигналов, введены многоканальный генератор импульсов и блок запуска линии задержки, при этом входы многоканального генератора импульсов соединены с дополнительньоми выходами блока управления,одни из выходов - с входными зажимами испытуемого блока, а другие выходы - с одними из вколов блока запуска линии задержки,другой вход которого связан с блоком считывания, а выход - с линией задержки.

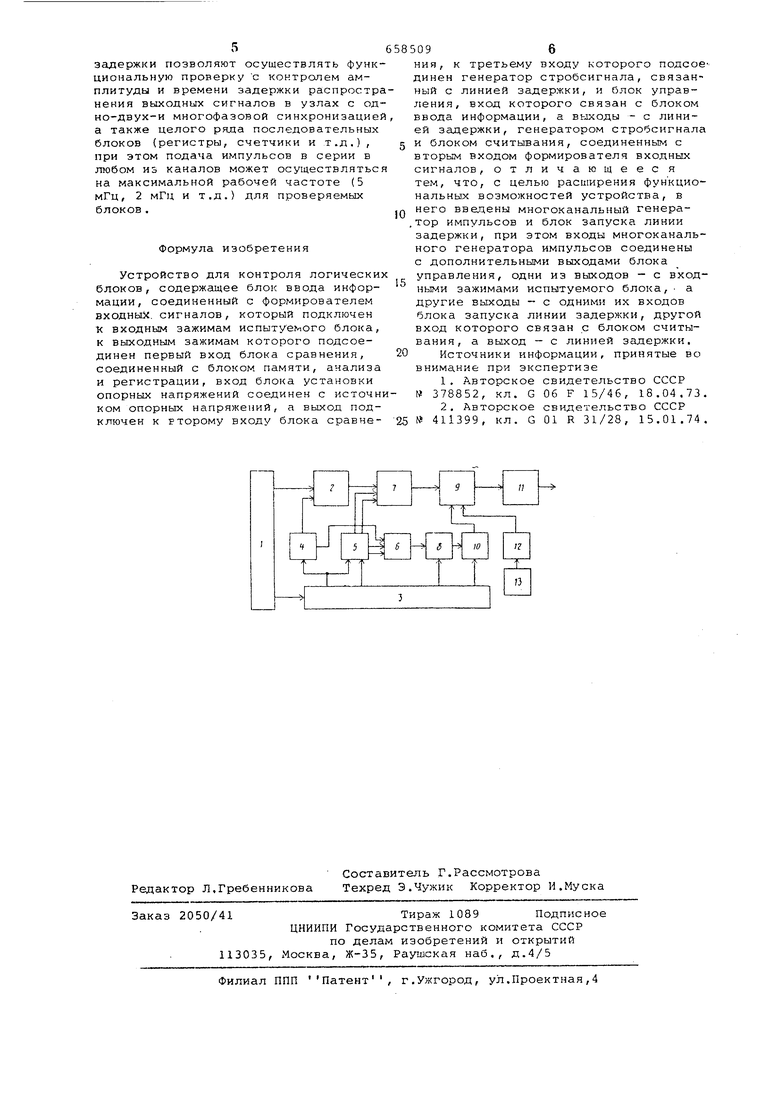

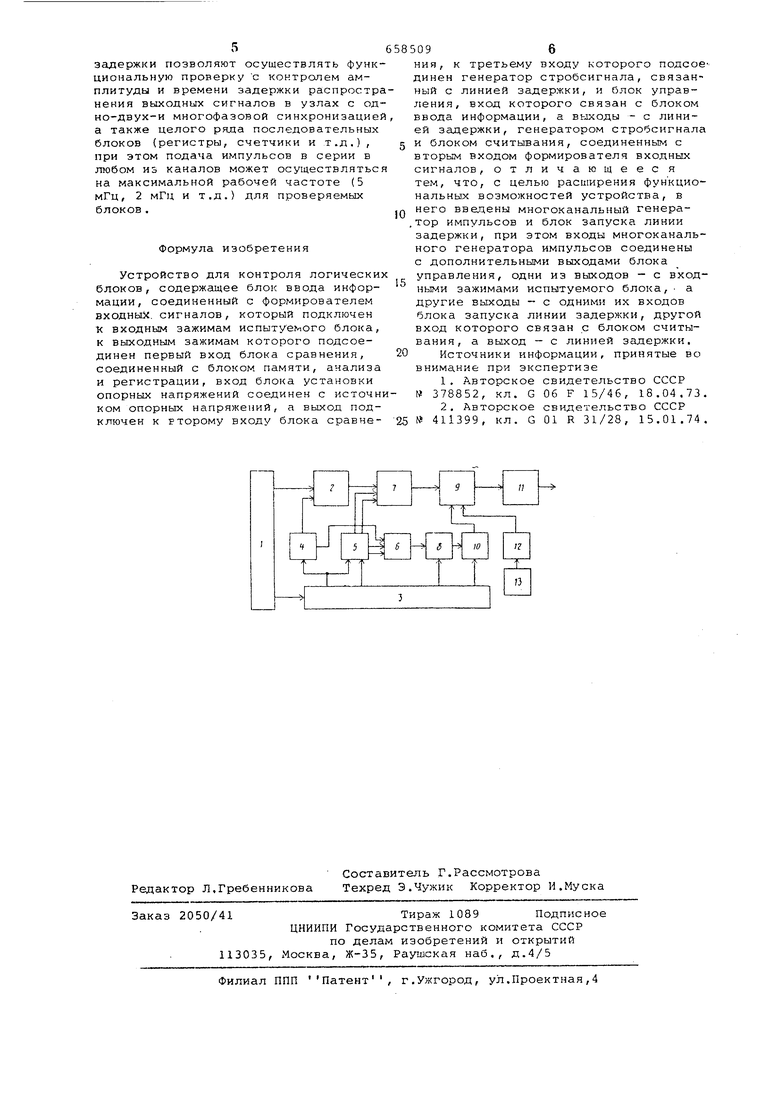

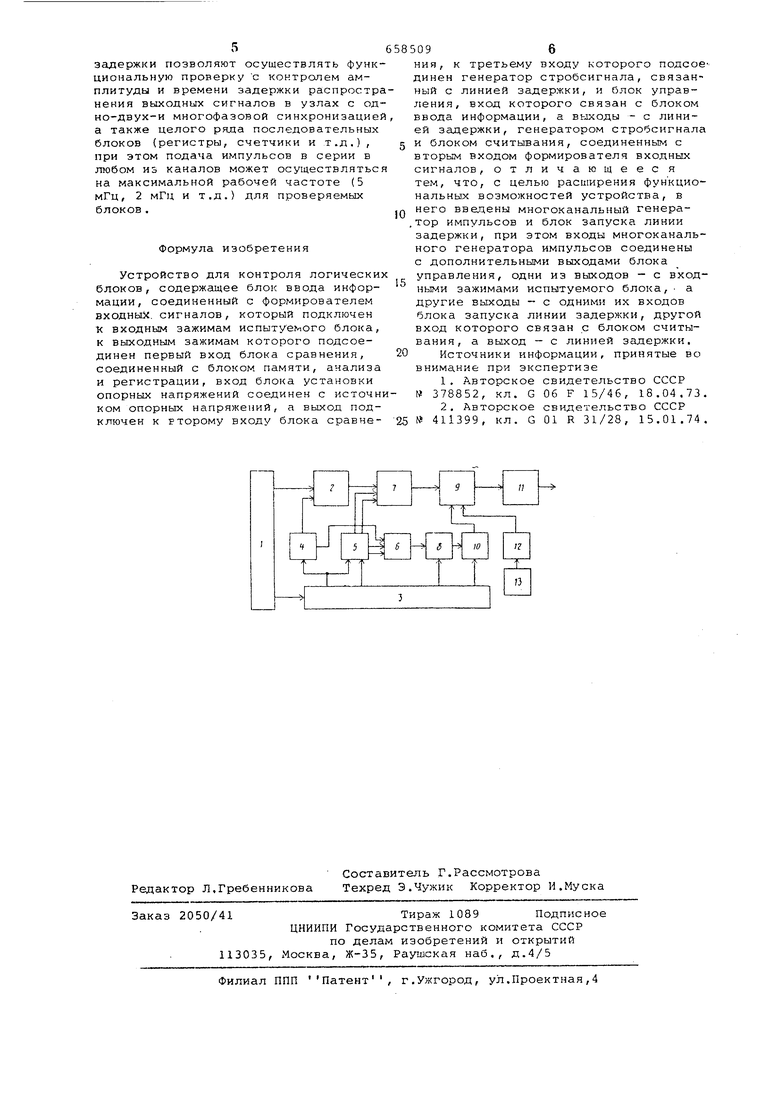

На чертеже приведена структурная электрическая схема устройства.

Устройство содержит блок 1 ввода информации, формирователь 2 входных сигналов, блок 3 управления, блок 4 считывания, многоканальный генератор 5 импульсов, блок 6 запуска линии задержки, испытуемый блок 7, линию 8 задержки, блок 9 сравнения,генератор 10 стробирующих сигналов, блок 11 памяти анализа и регистрации, блок 12 устаноки опорных напряжений и источник 13 опорньлх напряжений.

Програглма проверки, состоящая из тестовых и управляющих команд, поступает из блока 1 ввода информации на входы формирователя 2 и блока 3. Выходы блока 3 управления соединены с входами блока 4 считьшания, генератора 5 импульсов, линии 8 зад-эржки и генератора 10, С выхода формирователя 2 после прихода на его вход из блока 4 считьшания сигнала считывания на вход блока 7 подаются сигналы О и с заданными уровнями напряжения. Этот же сигнал считьюания с другого выхода блока 4 поступает на один из входоз блока 6.

Первая группа выходов генератора 5 импульсов соединена с входам 1 блока 7, а вторая группа выходов - с вxoдa IИ блока 6. Исследуемые сигналы с выхода испытуемого блока 7 подаются на один из входов блока 9 сравнег1ия, на другом входе которого устанавливается заранее необходимый уровень опорного напряжения U или U с блока 12, соединенного с источником 13. Задержанный сигнал с выхода линии 8 задержки подается на вход генератора 10,, с выхода которого сформированный стробсигнал подается на стробируемый вход блока 9 сравнения, выход последнего соединен с входом блока 11 памяти, анализа и регистрации.

Устройство работает следующиг« образом,

Программа проверки испытуемого бло ка 7; состоящая из тестовых- наборов, последовательно вводи ся в формирова тель 2 из блока 1.

После записи одного тестового набора из блока 3 на вход блока 4 поступает команда, в результате чего по сигналу считьтания с выхода блока 4 считывания на входы испытуемого блока

7 подается записанный в формирователе 2 тестовый набор. Та же команда, которая подается в блок считывания, запускает генератор 5 импульсов. Характерной особенностью генератора 5 является возможность регулируемого фазового сдвига импульсов в каналах, длительность, полярность, количество и частота следования которых также может Г1рограмл/1иров аться. В частном случае может быть использован гене- ,ратор импульсов с одним выходом. Импульсные сигналы с определенным фазовым сдвигом и задержкой по отношению к поданному тестовому набору, имеющие заданную амплитуду, длительность и полярность, с выходов генератора 5 поступают на импульсные входы испытуемого блока 7 с частотой следования, определяемой пpoгpaмJvioй, которая много выше частоты смены тестовых наборов, поступающих через формирователь 2 на испытуемый блок-7, Запуск линии 8 задержки и формирование стробсигнала в генераторе 10 для стробирования блока 9 сравнения, на входы которого с выходов блока 7 подаются сигналы реакции в ответ на потенциальные и импульсные воздействия с выходов формирователя 2 и генератора 5 импульсов и соответствующие уровни опорного напряжения, осуществляется сигналом с выхода блока б запуска линии задержки, которая срабатывает от последнего импульса любого выбранного выхода ( - п ) ге-кератора 5. После подачи стробсигнала н блок 9 в последнем осуществляется амп;7итудно временная селекция. Ин4|Ормация о годности или негодности исследуемых логических сигналов по уровню (амплитудная селекция) и задержке распространения в испытуемом узле (временная селекция) регистрируется блоком 11 памяти, анализа и регистрации ,

Аналогично происходит работа при считывании последующих тестовых наборов. Если после какого-либо тестового набора не требуется подача импульсных сигналов с многоканального генератора 5 импульсов, то в соответствии с проrpaivff/ioA проверки происходит блокировка генератора импульсов сигналом с блока 3, а запуск линии 8 задержки и формирование стробсигнала осуществляется в этом случае с выхода блока 6 запуска линии Эсщержки от сигнала счиRтывания из блока 4. При необходимости после любого тестового набора блокировка с генератора 5 может быть снята и его запуск осуществляется командой считывания из блока управления.

Таким образом, предлагаемое устройciBO реализует проверку значительно больших разнов15дкостей испытуемых логических блоков, так как введенные дополнительно многоканальный генератор импульсов и блок запуска линии S задержки позволяют осуществлять функ циональную проверку с контролем амплитуды и времени задержки распростр нения выходных сигналов в узлах с од но-двух-и многофазовой синхронизацие а также целого ряда последовательных блоков (регистры, счетчики и т.д.), при этом подача импульсов в серии в любом из каналов может осуществлятьс на максимальной рабочей частоте (5 МГц, 2 МГц и т.д.) для проверяемых блоков. Формула изобретения Устройство для контроля логически блоков, содержащее блок ввода информации, соединенный с формирователем входных, сигналов, который подключен К входным зажимам испытуемого блока, к выходным зажимам которого подсоединен первый вход блока сравнения, соединенный с блоком памяти, анализа и регистрации, вход блока установки опорных напряжений соединен с источн ком опорных напряжений, а выход подключен к второму входу блока сравне096ния, к третьему входу которого подсоединен генератор стробсигнала, связанный с линией задержки, и блок управления, вход которого связан с блоком ввода информации, а выходы - с линией задержки, генератором стробсигнала и блоком считывания, соединенным с вторым входом формирователя входных сигналов, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него вве.цены многоканальный генератор импульсов и блок запуска линии задержки, при этом входы многоканального генератора импульсов соединены с дополнительными выходами блока управления, одни из выходов - с входными зажимами испытуемого блока, а другие выходы - с одними их входов блока запуска линии задержки, другой вход которого связан с блоком считывания, а вЕЛход - с линией задержки. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 378852, кл. G Об F 15/46, 18.04.73. 2.Авторское свидетельство СССР 411399, кл. G 01 R 31/28, 15.01.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| УСТРОЙСТВО для КОНТРОЛЯ МИКРОЭЛЕКТРОННЫХ ЛОГИЧЕСКИХ СХЕМ | 1970 |

|

SU273342A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| СИСТЕМА УЧЕТА РАСХОДА ГАЗА ИЛИ ЖИДКОСТИ | 2004 |

|

RU2276776C1 |

Авторы

Даты

1979-04-25—Публикация

1976-08-03—Подача