со

00 00

;о со

t7ZJ...21

Изобретение относится к вычисли- |тельной технике, предназначено для преобразования кода из системы оста- iточных классов в позиционный код и может быть использовано в ци фровых системах автоматики и телемеханики.

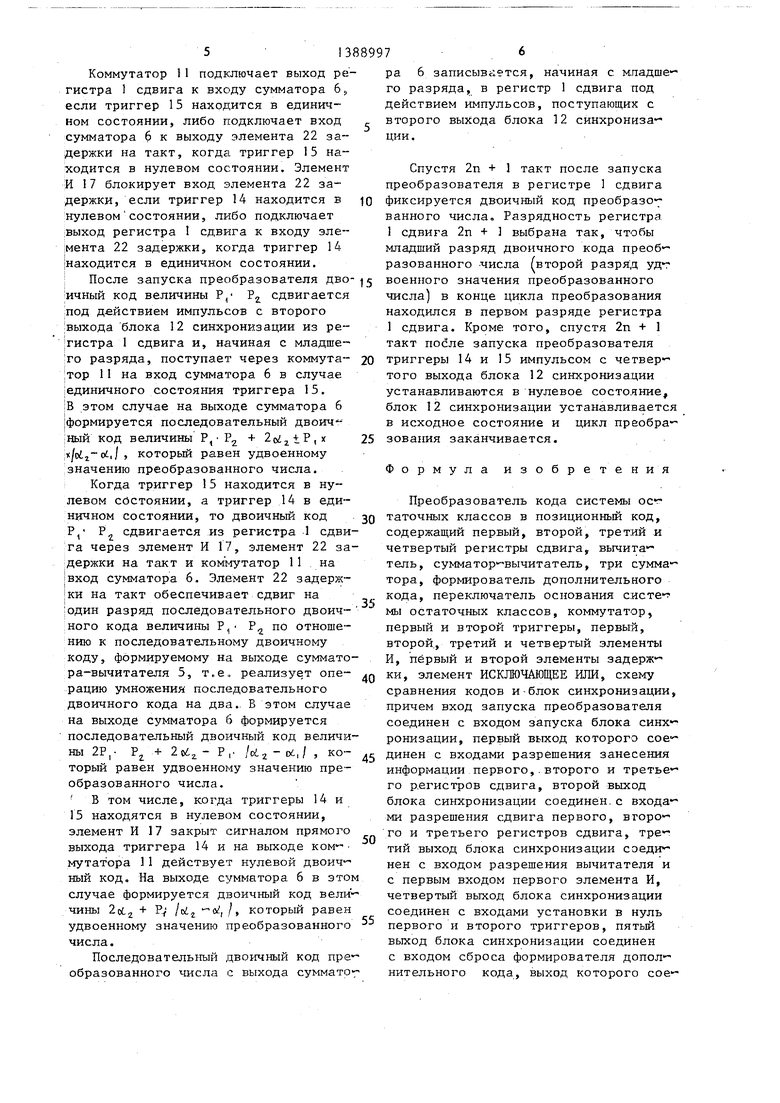

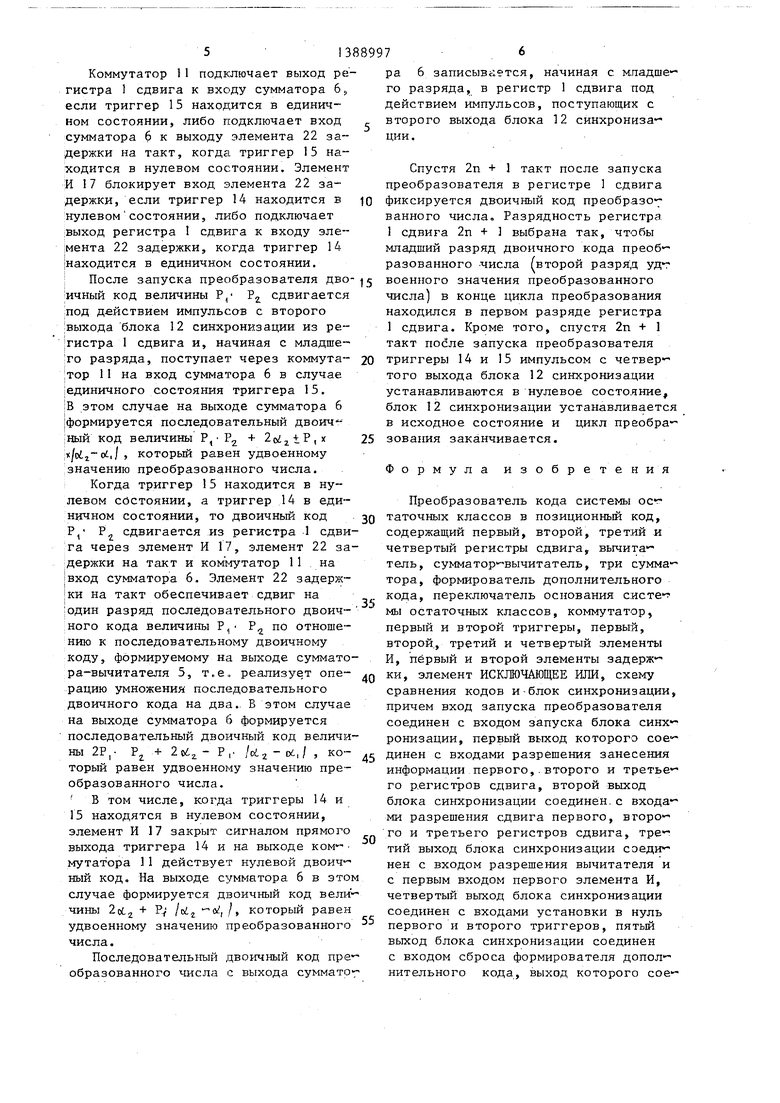

Целью изобретения является сокращение аппаратурных затрат. : На чертеже представлена схема |преобразователя кода системы остаточ- |ных классов в позиционный код.

Преобразователь кода системы остаточных классов в позицонный код со

рует последовательность синхроимпульсов на своих выходах. Синхроимпульс с первого выхода блока 12 синхронизации поступает на входь управления занесением информации регистров 1-3 сдвига, а также на входы элементов И 18 и 19. По этому сигналу,в реггист- ры 1,2 и 3 сдвига вводится исходная информация в виде параллельных двоичных кодов, а триггеры 14 и 15 устанавливаются в состояния, определяющие режим работы преобразователя. Регистр 1 сдвига содержит 2п + 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования кода из системы остаточных классов в позиционный код. Цель изобретения состоит в сокращении аппаратурных затрат. Поставленная цель достигается тем, что преобразователь кода системы остаточных классов в позиционный код, содержащий четыре регистра 1-4 сдвига, вы- читатель 7, сумматор-вычитатель 5, три сумматора 6,24,25, формирователь 8 дополнительного кода, переключатель 9 основания системы остаточных классов, коммутатор II, блок 12 синхронизации, схему 13 сравнения кодов, два триггера .14,15, четыре элемента И 16-19, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, два элемента 21,22 задержки, содержит третий элемент задержки 23 с соответствующими связями. 1 шт. с S (Л

держит регистры 1-4 сдвига, сумматор-15 разряд, а регистры 2 и 3 сдвига п

вычитатель 5, сумматор 6, вычитатель

I 7, фбрмирователь 8 дополнительного

кода, переключатель 9 основания сис|темы остаточных классов, вход 10 раI Дания диапазона представления чисел 20

{преобразователя, коммутатор 11, блок

|12 синхронизации, схему 13 сравнения

кодов, триггеры 14 и 15, элементы

IИ 16-19, элемент ИСЮПОЧАТЭДЕЕ ИЛИ 20,

;элементы 21-23 задержки, сумматоры 25

;24 и 25, группы информационных входов 26 и 27 преобразователя, вход 28

: запуска преобразователя,

Блок 12 синхронизации, схема 13

разрядов, где п - количество разрядов представления остатков об, и в по основаниям Р и Р, системы остаточных классов.

Регистр 4 сдвига содержит m раз рядов , где m п.

Параллельные п-разрядные двоичны коды остатков oi, и oi считываются с ответственно с информационных входо 26 и 27 и записываются в регистры 2 и 3 сдвига соответственно. Параллел ный 2п-разрядный двоичный код Р,,- Р диапазона представления чисел считы вается с входа 10 и записывается в

сравнения кодов и формирователь 8 до-30 регистр 1 сдвига, старший 2п + 1-й полнительного кода реализованы и функционируют идентично прототипу.

Преобразователь .кода системы остаточных классов в позиционный код работает следующим образом. 35

В исходном состоянии триггеры 14, 15 находятся в нулевом состоянии, в которое они устанавливаются в результате предыдущего цикла преобразования .40

С помощью переключателя 9 устанавливается двоичный код основания Р, системы остаточных классов, а на входе 10 устанавливают диапазон предразряд которого находится в нулевом состоянии.

Схема 13 сравнения кодов вает два п-разрядных параллельных двоичных кода остатков, действующих на информационных входах 26 и 27 ус ройства соответственно, и вырабатывает на выходе сигнал 1 при

Сигнал 1 на выходе схемы 13 сравнения кодов открывает элемент И 18, через который проходит импуль с первого выхода блока 12 синхрониз ции и устанавливает триггер 14 в единичное состояние.

J .,

Р Р

1 2

системы остаточных классов

Pj 6N - 1; N 2S m - натуральньй ряд чичисел, равный v , где

Переключатель 9 основания системы остаточных классов подключает один из выходов разрядов регистра 4 сдвига к входу элемента 23 задержки на такт и к первому входу сумматора 24.

За.пуск преобразователя осуществляется путем подачи сигнала 1 на вход 28 запуска преобразователя, по которому блок 12 синхронизации формиразрядов, где п - количество разрядов представления остатков об, и в по основаниям Р и Р, системы остаточных классов.

Регистр 4 сдвига содержит m разрядов , где m п.

Параллельные п-разрядные двоичные коды остатков oi, и oi считываются соответственно с информационных входов 26 и 27 и записываются в регистры 2. и 3 сдвига соответственно. Параллельный 2п-разрядный двоичный код Р,,- Р диапазона представления чисел считывается с входа 10 и записывается в

регистр 1 сдвига, старший 2п + 1-й

разряд которого находится в нулевом состоянии.

Схема 13 сравнения кодов вает два п-разрядных параллельных двоичных кода остатков, действующих . на информационных входах 26 и 27 устройства соответственно, и вырабатывает на выходе сигнал 1 при ,.

Сигнал 1 на выходе схемы 13 сравнения кодов открывает элемент И 18, через который проходит импульс с первого выхода блока 12 синхронизации и устанавливает триггер 14 в единичное состояние.

Элемент ИСЮТЮЧАЮЩЕЕ ИЛИ 20 сравнивает младшие разряды двоичных кодов остатков oi, и Ы, действующих на первых информационных входах 26 и 27 соответственно. Когда в младших разрядах двоичных кодов остатков действуют различные сигналы, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 формируется сигнал 1 который открывает элемент И 19. Импульс с первого выхода блока 12 синхронизации проходит через элемент И 19 и устанавливает триггер 15 в единичное состояние.

Под воздействием синхроимпульсов с второго выхода блока 12 синхронизации двоичные коды остатков сдвигаются, начиная с младшего разряда, с выходов регистров 2 и 3 сдвига соответственно. Вычитатель 7 вьтолняет последовательное вычитание из последовательного двоичного кода остатка oij последовательного двоичного кода остатка oi, , а на выходе вычитателя 7 формируется последовательный двоичный код разности остатков, который, начиная с младшего разряда, поступает на информационный вход формирователя- 8 дополнительного кода.

Формирователь 8 дополнительного кода преобразует дополнительный код разности остатков oi.. - (v, в прямой код, если на его управляющий вход поступает сигнал I с нулевого выхода триггера 14, или пропускает без изменения прямой код разности остатков, когда триггер 14 находится в единичном состоянии. Таким образом на выходе формирователя .8 дополнительного кода формируется прямой код абсолютной величины разности остатков /oij. - oi, / , который через элемент И 16 поступает, начиная с млад- шего разряда, на информационный вход регистра 4 сдвига. Спустя один, два,...,т тактов на выходах соответственно первого,- второго,... ,т-го разрядов регистра 4 сдвига под действием импульсов с второго выхода блока 12 синхронизации сдвигается, начиная с младших разрядов, последовательный двоичный код разности остатков. Поскольку задержка последова- тельного кода на один такт эквивалентна умножению на два, то на выходах первого, второго,...,т-го разрядов регистра 4 сдвига формируются соответственно последовательные дво- ичные коды величин 2 joi - oi i /,..., 2 /cij - oi, / . Выбор одной из этих величин осуществляют переключателем 9 основания системы остаточных классов Например, если основание системы ос- таточных классов P-f 6N + 1 , то выход i + 1-го разряда регистра 4 сдвига подключают переключателем 9 к входу элемента 23 задержки и первому входу сумматора 24. В этом случае на выходе переключателя 9 формируется .последовательный двоичный код величины -oi,/, который задерживается элементом 23 задержки на такт.

0 5 о « с

5

что эквивалентно умножению этой величины на два. Таким .образом, на выходе элемента 23 задержки формируется последовательный двоичный код величины 2 oil/ 5 который суммируется , начиная с младших разрядов, в сумматоре 24 с последовательным двоичным кодом величины , -о,/ , формируемым на выходе переключателя 9 основания системы остаточных классов . На выходе сумматора 24 формируется последовательный двоичный код величины б-2 joly oi,t , который суммируется, начиная с младших разрядов, в сумматоре 25 с последовательным двоичным кодом величины/6i -oi,/, формируемым на выходе элемента И 16. На выходе сумматора 25 формируется пос- ледовательный двоичный код произведения основания системы остаточных классов на абсолютизме величину разности остатков P./oi, -об,/ . Спустя -п тактов, после запуска преобразователя на третьем выходе блока 12 синхронизации вырабатывается нулевой сигнал, блокирующий Вычитатель 7, а на пятом выходе блока 12 синхронизации формируется сигнал 1, устанавливающий по входу . сброса формирователь 8 дополнительного кода в исходное состояние. С выхода сумматора 25 последовательный двоичный код произведения поступает, начиная с младшего разряда, на первый вход сумматора-вычитателя 5. Сум- матор-вычитатель 5 устанавливается в режим суммирования, если триггер 14 находится в нулевом состоянии, либо в режим вычитания, когда триггер 14 находится в единичном состоянии. Последовательный двоичный код остатка сдвигается, начиная с младшего разряда, под действием импульсов с второго выхода блока 12 синхронизации на вкод элемента 21 задержки на такт. Элемент 21 задержки обеспечивает сдвиг на один разряд последовательного двоичного кода остатка об по отношению к последовательному двоичному коду произведения . а,/ , т.е. реализует операцию умножения двоичного кода остатка на два. Последовательный двоичный код величины 2oi2 поступает с выхода элемента 21 задержки на второй вход сумматора- вычитателя 5, который в зависимости от режима суммирования или вычитания формирует последовательный двоичный код величины i l

5 13 Коммутатор 1 1 подключает выход регистра 1 сдвига к входу сумматора 6,, если триггер 15 находится в единичном состоянии, либо подключает вход сумматора 6 к выходу элемента 22 задержки на такт, когда триггер 15 находится в нулевом состоянии. Элемент И 17 блокирует вход, элемента 22 задержки, если триггер 14 находится в нулевом состоянии, либо подключает :выход регистра I сдвига к входу элемента 22 задержки, когда триггер 14 Находится в единичном состоянии.

После запуска преобразователя дно

ичный код величины Pj, сдвигается под действием импульсов с второго |выхода блока 12 синхронизации из ре- :гистра 1 сдвига и, начиная с младше- го разряда, поступает через коммута- ;тор 11 на вход сумматора 6 в случае ;единичного состояния триггера 15. |В этом случае на выходе сумматора 6 |формируется последовательный двоич 1НЫЙ код величины Р, Р + 2ы t Р , х :n/oii oi,/, который равен удвоенному значению преобразованного числа.

Когда триггер 15 находится в нулевом состоянии, а триггер 14 в единичном состоянии, то двоичный код Р,- Р сдвигается из регистра 1 сдви га через элемент И 17, элемент 22 задержки на такт и коммутатор 11 на |вход сумматора 6. Элемент 22 задерж- |ки на такт обеспечивает сдвиг на ОДИН разряд последовательного двоич ного кода величины Р, Р по отношению к последовательному двоичному коду, формируемому на выходе суммато ра-вычитателя 5, т..е„ реализует операцию умножения последовательного двоичного кода на два.. В этом случае на выходе сумматора 6 формируется последовательный двоичный код величины 2Р,- Р + 2ci,, - Р,. ., , который равен удвоенному значению преобразованного числа. В том числе, когда триггеры 14 и 15 находятся в нулевом состоянии, элемент И 17 закрыт сигналом прямого выхода триггера 14 и на выходе ком-- мутат ора 1 1 действует нулевой двоич ный код. На выходе сумматора 6 в это случае формируется двоичный код вели чины 2о(,2 + PV /oi If который равен удвоенному значению преобразованного числа.

Последовательный двоичный код пре образованного числа с выхода суммато

7

ра 6 записывается, начиная с младше го разряда, в регистр 1 сдвига под действием импульсов, поступаюш,их с второго выхода блока 12 синхрониза- ции.

Спустя 2п + 1 такт после запуска преобразователя в регистре 1 сдвига фиксируется двоичный код преобразо- ванного числа. Разрядность регистра 1 сдвига 2п + выбрана так, чтобы

„ Q

д

0 5

30

35

40

45

50

55

младший разряд двоичного кода преоб- разованного -числа (второй разряд удг военного значения преобразованного числа) в конце цикла преобразования находился в первом разряде регистра 1 сдвига. Кроме того, спустя 2п + 1 такт после запуска преобразователя триггеры 14 и 15 импульсом с четвер- того выхода блока 12 синхронизации устанавливаются в нулевое состояние, блок 12 синхронизации устанавливается в исходное состояние и цикл преобразования заканчивается.

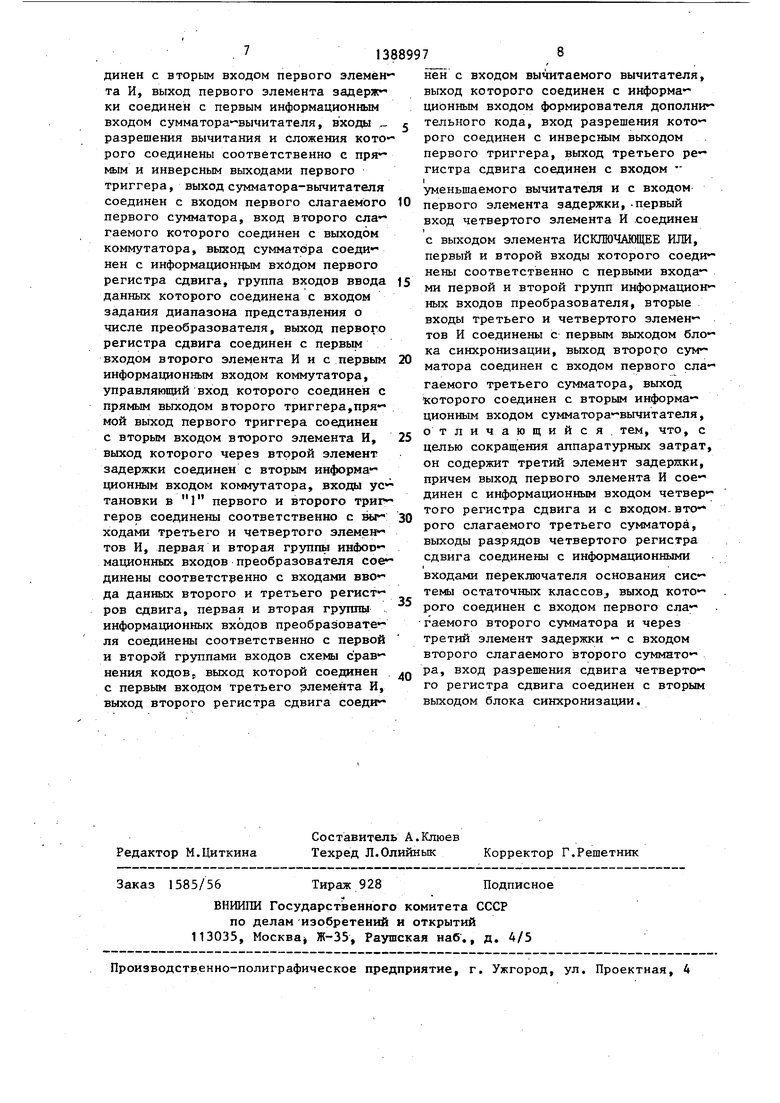

Формула изобретения

Преобразователь кода системы ос таточных классов в позиционный код, содержаш;ий первый, второй, третий и четвертый регистры сдвига, вычита тель, сумматор вычитатель, три сумма- тора, формирователь дополнительного кода, переключатель основания систе- мы остаточных классов, коммутатор, первый и второй триггеры, первый, второй., третий и четвертый элементы И, первый и второй элементы задерж ки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, схему сравнения кодов и-блок синхронизации, причем вход запуска преобразователя соединен с входом запуска блока синх- ронизации, первый выход которого сое- динен с входами разрешения занесения информации первого,.второго и третьего регистров сдвига, второй выход блока синхронизации соединен.с входами разрешения сдвига первого, второго и третьего регистров сдвига, третий выход блока синхронизации соединен с входом разрешения вычитателя и с первым входом первого элемента И, четвертый выход блока Синхронизации соединен с входами установки в нуль первого и второго триггеров, пятый выход блока синхронизации соединен с входом сброса формирователя дополнительного кода, выход которого сое-

динен с вторым входом первого элемён та И, выход первого элемента задерж ки соединен с первым информационным входом сумматора- вычитателя, входы разрешения вычитания и сложения которого соединены соответственно с пря мым и инверсным выходами первого триггера, выход сумматора-вычитателя соединён с входом первого слагаемого первого сумматора, вход второго ела гаемого которого соединен с выходом коммутатора, выход сумматора соеди нен с информационным вхйдом первого регистра сдвига, группа входов ввода данных которого соединена с входом задания диапазона представления о числе преобразователя, выход первого регистра сдвига соединен с первым входом второго элемента И и с первым информационным входом коммутатора, управляющий вход которого соединен с прямым выходом второго триггера,пря мой выход первого триггера соединен с вторым входом второго элемента И, выход которого через второй элемент задержки соединен с вторым ииформа ционным входом коммутатора, входы ус тановки в 1 первого и второго триг геров соединены соответственно с вы ходами третьего и четвертого элемен тов И, первая и вторая группь ин(Ьоо«- мационных входов преобразователя сое динены соответственно с входами да данных второго и третьего регистров сдвига, первая и вторая группы информационных входов преобразователя соединены соответственно с первой и второй группами входов схемы сравнения кодов, выход которой соединен с первым входом третьего элемента И, выход второго регистра сдвига соеди-

нен с входом вычитаемого вычитателя, выход которого соединен с информационным входом формирователя дополнительного кода, вход разрешения которого соединен с инверсным выходом первого триггера, выход третьего регистра сдвига соединен с входом I уменьшаемого вычитателя и с входомпервого элемента задержки,-первый вход четвертого элемента И .соединен

с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с первыми входами первой и второй групп информационных входов преобразователя, вторые входы третьего и четвертого элементов И соединены с первым выходом блока синхронизации, выход второго сумматора соединен с входом первого слагаемого третьего сумматора, выход которого соединен с вторым информационным входом сумматора-вычитателя, отличающийся, тем, что, с целью сокращения аппаратурных затрат, он содержит третий элемент задержки, причем выход первого элемента И соединен с информационным входом четвертого регистра сдвига и с входом-второго слагаемого третьего сумматора, выходы разрядов четвертого регистра сдвига соединены с информационными

входами переключателя основания системы остаточных клaccoвJ выход которого соединен с входом первого слагаемого второго сумматора и через третий элемент задержки - с входом второго слагаемого второго сумматора, вход разрешения сдвига четвертого регистра сдвига соединен с вторым выходом блока синхронизации.

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU924695A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для умножения на коэффициент | 1975 |

|

SU557363A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-07-22—Подача