1

Изобретение относится к области вычислительной техники и может быть использовано для проверки работоспособности и программного обеспечения микропроцессоров.

Известны устройства для контроля систем обработки информации, содержащие .блоки регистров, блок памяти, блок преобразователей кода, блоки совпадения кодов, блок адресного опроса и логический блок управления, и выполняющие функции формирования кодов адресов и данных для ввода в контрольную систему и последующего анализа правильности ее реакций 1.

Недостаток этих устройств заключен в их сложности, обусловленной большим объемом памяти, необходимой для хранения всех исполненных команд проверки.

Наиболее близким к данному по сзщности технического решения является зстройство для контроля, содержащее блок индикации, блок управления, первый выход которого подключен к управляющим входам блока формирования адресов и блока формирования данных, управляющие выходы которых соединены с соответствующими входами блока управления, соединенного вторым выходом с блоком ввода, выход которого и информационный выход блока формирования адресов подключены

к соответствующим входам блока буферной памяти, первый выход которого подключен к первому входу блока формирования данных, второй вход и выход которого являются первым входом и выходом устройства 2.

Недостаток этого устройства состоит в том, что определение неисправности требует большого интервала времени. Это обусловлено тем, что индикация осуществляется только для последнего временного такта. Поскольку специфика микропроцессора требует для анализа места и характера неисправности знания состояния объекта

контроля на предшествующих тактах, а иногда оказывается полезным и состояние на нескольких последующих тактах, то реализация этих условий требует больших затрат времени.

Целью изобретения является сокращение времени определения неисправностей.

Поставленная задача достигается тем, что в устройство введены блок памяти, блок регистров условий запуска и схема

сравнения зсловий запуска, причем входы схемы сравнения условий запуска подключены соответственно к выходу блока регистров условий запуска, входом соединенного с третьим выходом блока управления,

и выходу блока формирования данных, выход схемы сравнения условий запуске, подключен к уиравляющему входу блока индикации, информационпый вход которого соединси с выходом блока памяти, 1зходы которого подключены соответственно ко второму выходу блока буферной памяти, выходу блока формпроваппя данпых и второму входу устройства.

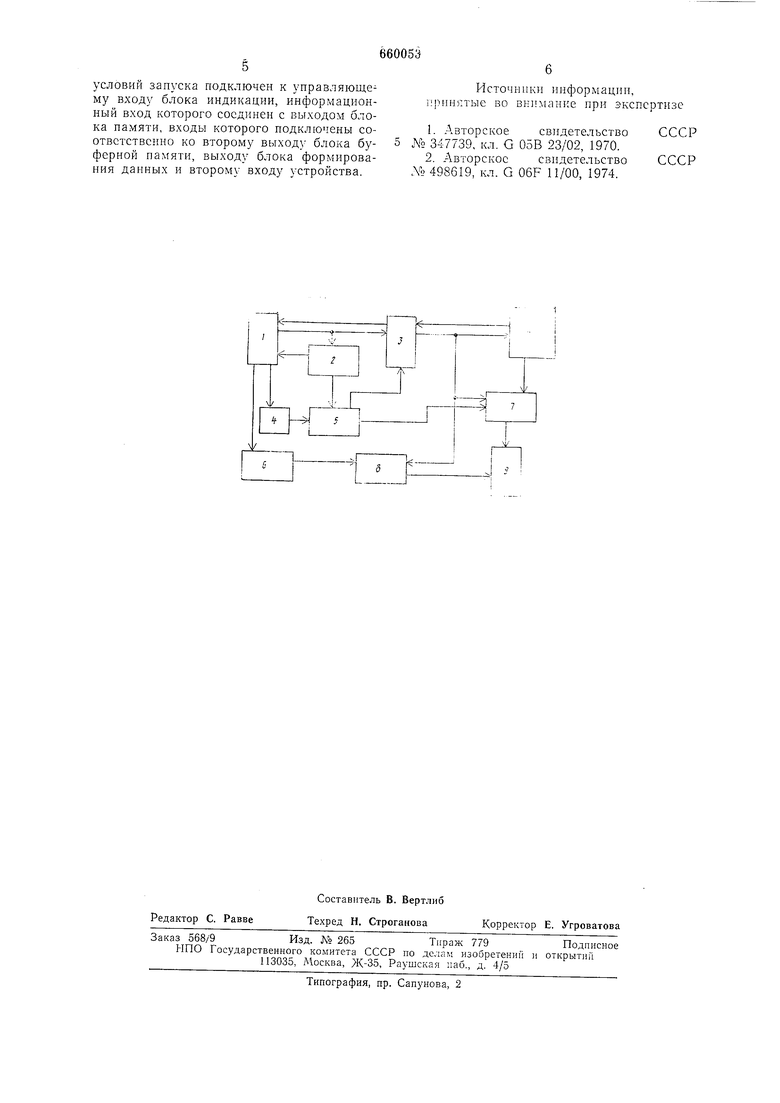

На чертеже представлена блок-схема устройства, содержащая блок 1 управления, блок 2 формирования адресов, блок 3 формпровапия даппых, блок 4 ввода, блок 5 буферной памяти, блок 6 регистров условий запуска, блок 7 памяти, cxeivia сравнения 8 условий запуска, блок индикации 9 и контролируемый микропроцессор 10.

Блок 1 управления служит для хранения и отработки программы испытаний и выполняет функции синхронизации п управления по отноп1еппю к другим блокам устройства. Блок 2 формирования адресов содержит регистры и схемы сравнения и служит для формирования адреса быстродействующего блока 5 буферной памяти, где хранятся тесты и ответные реакцип коптролируемого микропроцессора 10. По командам, выдаваемым из блока 1, содержимое адресного регистра блока 2 может быть уменьшено, увеличено, сдвинуто на 1 разряд или изменено другим образом. Блок 3 формирования данных содержит регистры п схемы сравнения и служит для выдачи входных последовательностей {инструкций и онерандов) в контролируемый микропроцессор 10, полученных пз блока 5 и (или) модифицированных в соответствии с командами из блока 1. Блок 3, кроме того, анализирует реакции контролируемого микропроцессора 10 с эталонными реакциями и при обнаружении расхождений выдает сигналы в блок 1. Блок 4 ввода служит для ввода информации в блок 5 буферной памяти. Блок памяти служит буферным накопптелем для блока индикации 9, который индицирует информацию, содержащуюся в блоке 7. Эта память может быть организована, например, в виде массива сдвиговых регистров, разрядность которых соответствует максимальному числу слов, индицируемых в блоке 9.

Устройство работает следующим образом.

Блок 2 формирует адрес ячейки блока 5, содержимое которой через блок 3 поступает в контролируемый микропроцессор 10. Ответные реакции поступают обратно в блок 3. Одновременно информация из блока 5, а также информация, поступающая в микропроцессор 10 и выдаваемая им, фиксируется в блоке 7 памяти п выдается на

индикацию в блок 9. При этом, поскольку скорость выдачи слои в микропроцессор 10 достаточио высока, па блоке 9 организуется так называемый «плывущий кадр, обеспечнвающ.ий послсдоватсльпый сдвиг индицируемых слов, например, снизу вверх при появлении па входе каждого нового слова. В регистры условий блока 6 из блока 1 введены условия, при которых производится

блокировка ввода информации в блок 7 памяти, после чего сдвиг строк прекращается и на экране блока 9 оказывается доступным для визуального контроля все мнол ;ество слов, непосредственно предществовавших выдаче сигнала блокировки, включая слово, на котором блокировка произошла.

Аналогично, если блок 3 зафиксирует нарушение в работе микропроцессора 10, сообщит об этом в блок 1, который примет решение об остановке испытаний, то на вход блока 7 перестанут поступать данные, а на экране блока 9 будет представлено последнее введенное слово вместе с набором предшествующих ему слов в норядке их поступления в микропроцессор.

Таким образом, устройство обеспечивает вывод заданного множества слов контро.тьного теста, обеспечивающих возможцость проведения а)1ализа состояния микроироцессора п определения характера его неисправности.

Формула изобретения

Устройство для контроля микропроцессора, содержащее блок индикации, блок управления, первый выход которого нодключен к унравляющим входам блока формирования адресов и блока формирования

данных, управляющие выходы которых соединены с соответствующими входами блока управления, соединенного вторым выходом с блоком ввода, выход которого и информационный выход блока формирования адресов подключены к соответствующим входам блока буферной памяти, первый выход которого подк,:1ючен к первому входу блока формирования данных, второй вход и выход которого являются первым входом и выходом устройства, от л и ч а ю п; е ее я тем, что, с целью сокращения времени определения неисправностей, в устройство введены блок памяти, блок регистров условий запуска н схема сравнения условий запуска, причем входы схемы сравнения условий запуска подключены соответственно к выходу блока регистров условий запуска, входом соединенного с третьим выходом блока управления н выходу блока формирования данных, выход схемы сравнения условий запуска подключен к управляющему входу блока индикации, информационный вход которого соединен с выходом блока памяти, входы которого подключены соответственно ко второму выходу блока буферной памяти, выходу блока формирования данных и второму входу устройства. Источники информации, 1 ринятые во внимание при экспертизе 1.Авторское свидетельство СССР № 347739, кл. G 05В 23/02, 1970. 2.Авторское евидетельство СССР .YO 498619, кл. G 06F 11/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и управленияАВТОТРАНСпОРТНыМ пАРКОМ | 1979 |

|

SU815735A1 |

| Устройство отображения графической информации | 1982 |

|

SU1111197A1 |

| Устройство для контроля импульсных параметров магнитных сердечников | 1981 |

|

SU981908A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Имитатор канала | 1987 |

|

SU1467555A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Имитатор локальной шины микропроцессора | 1987 |

|

SU1644144A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

Авторы

Даты

1979-04-30—Публикация

1977-01-17—Подача