(21)4332551/24

(22)09.10.87

(46) 23.04.91. Бол. № 15

(72) О.Ю.Гудзенко, Л.М.Кельнер,

Н.Я.Смовженко, А.А.Тибулевич

и А.А.Юрасов

(53) 681.3(088.8)

(56) Авторское свидетельство СССР

№ 642703, кл. G 06 F 11/26, 1977.

Авторское свидетельство СССР № 1381514, кл. G 06 F 11/00, 1986.

(54) ИМИТАТОР ЛОКАЛЬНОЙ ШИНЫ МИКРОПРОЦЕССОРА

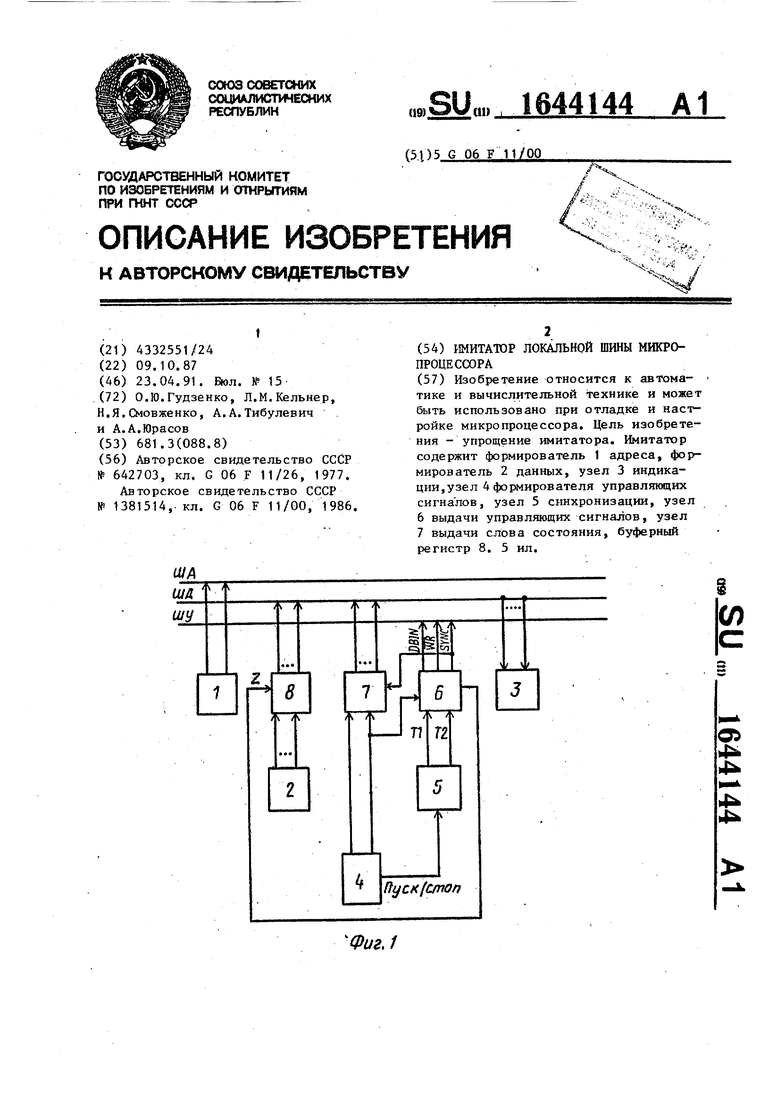

(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при отладке и настройке микропроцессора. Цель изобретения - упрощение имитатора. Имитатор содержит формирователь 1 адреса, формирователь 2 данных, узел 3 индикации, узе л 4 формирователя управляющих сигналов, узел 5 синхронизации, узел

6выдачи управляющих сигналов, узел

7выдачи слова состояния, буферный регистр 8. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

Фиг. 1

О

Јь

Јь

Ј Ј

Изобретение относится к автоматике и вычислительной технике и может быть использовано при отладке и настройке микропроцессора.

Цель изобретения - упрощение ими™ татора.

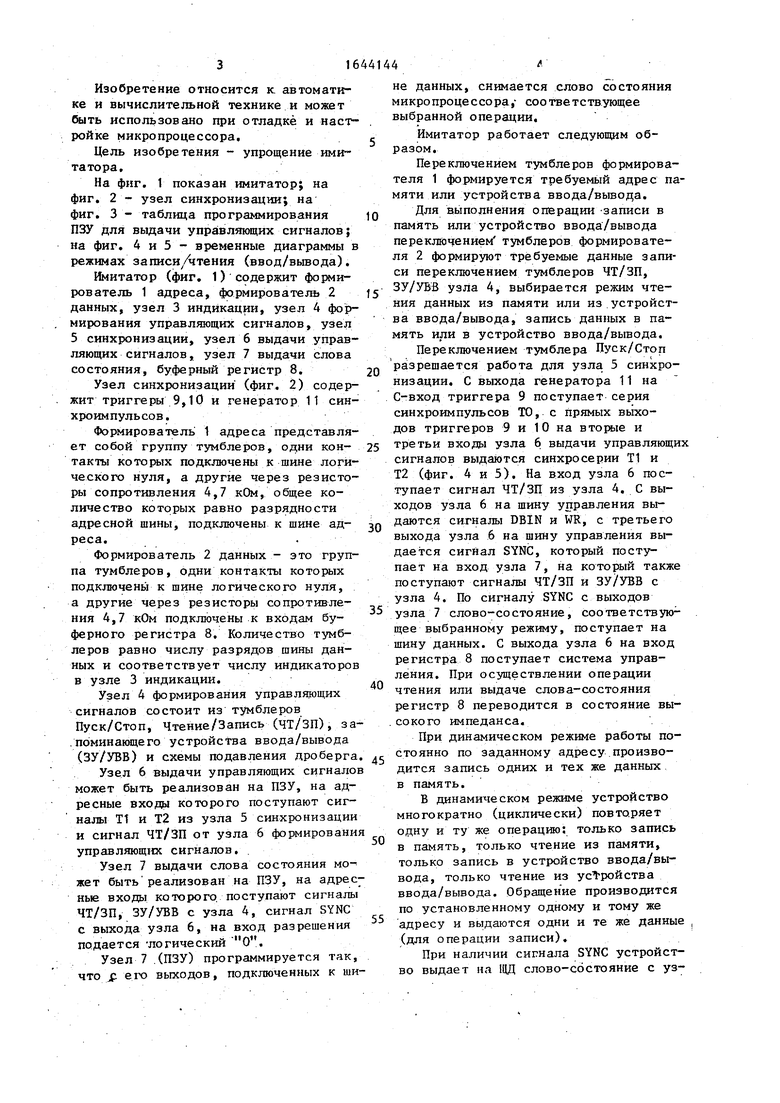

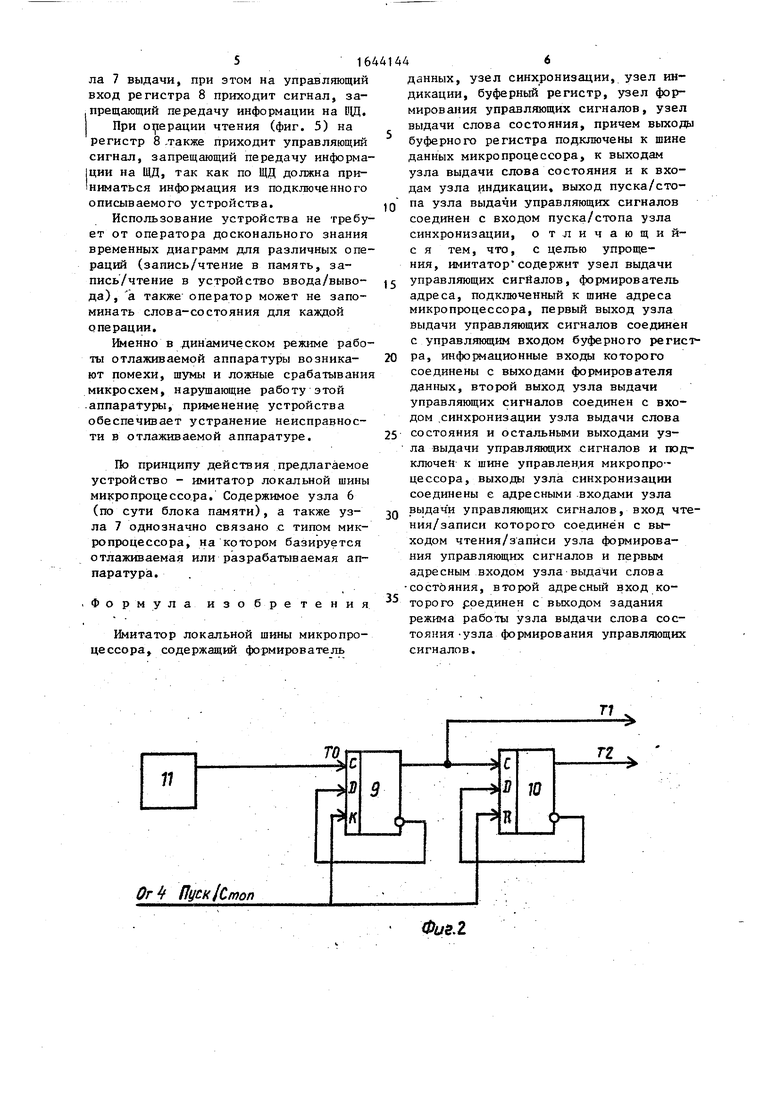

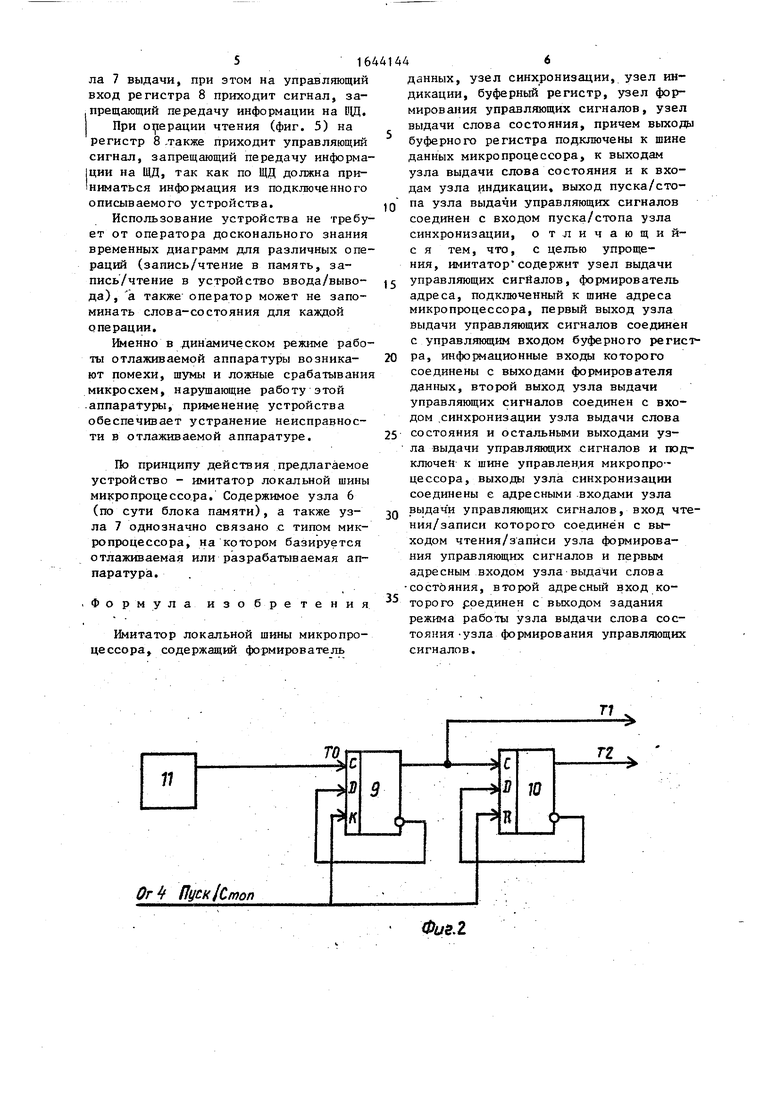

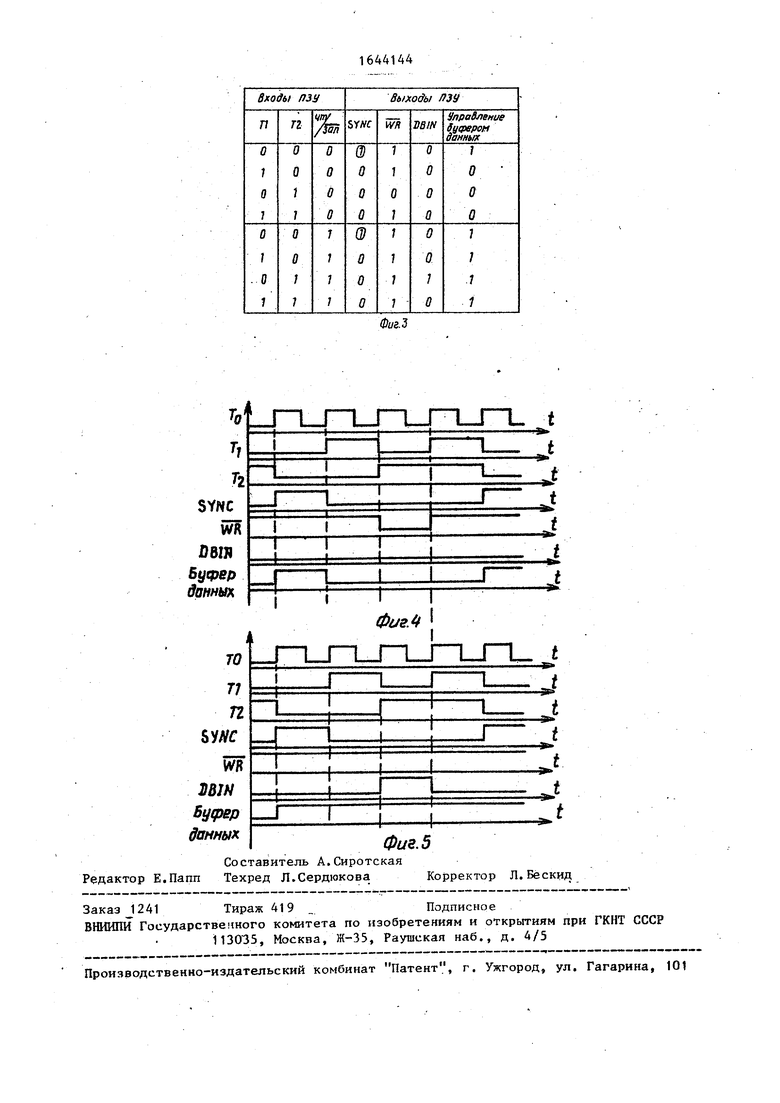

На фиг. 1 показан имитатор; на фиг. 2 - узел синхронизации; на фиг. 3 - таблица программирования

ПЗУ для выдачи управляющих сигналов; на фиг. 4 и 5 - временные диаграммы в режимах записи/чтения (ввод/вывода). Имитатор (фиг. 1) содержит формирователь 1 адреса, формирователь 2 данных, узел 3 индикации, узел 4 формирования управляющих сигналов, узел 5 синхронизации, узел 6 выдачи управляющих сигналов, узел 7 выдачи слова состояния, буферный регистр 8.

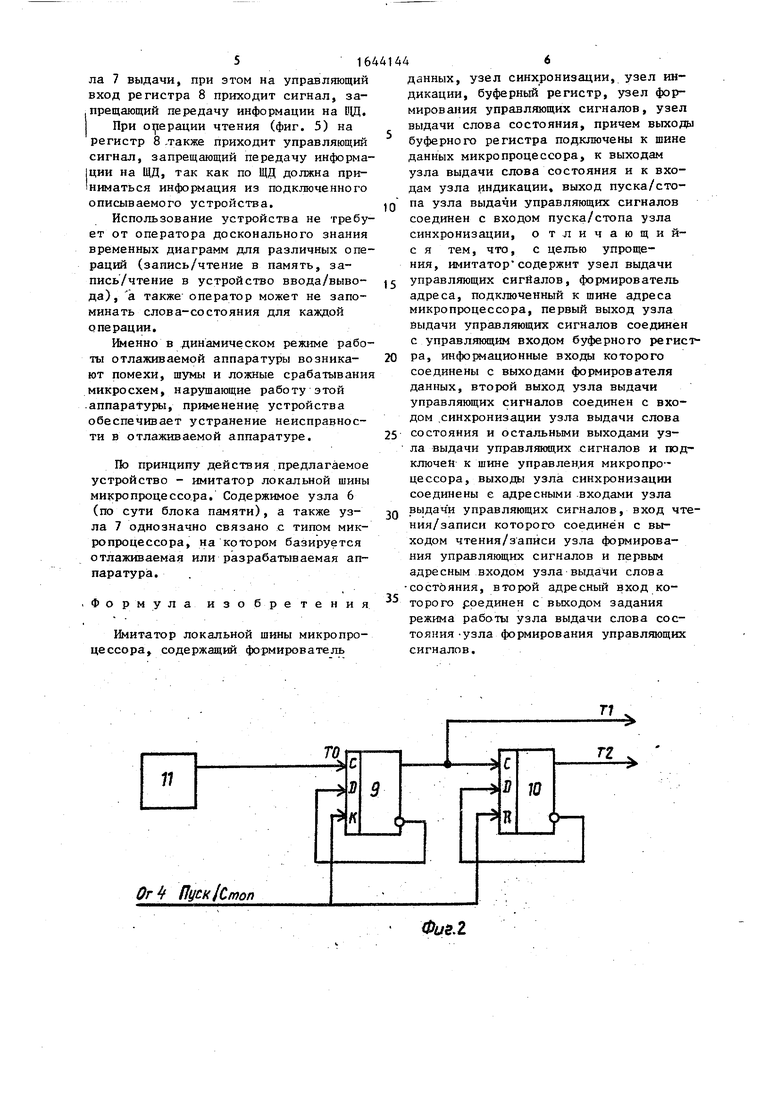

Узел синхронизации (фиг. 2) содержит триггеры 9,10 и генератор 11 синхроимпульсов .

Формирователь 1 адреса представляет собой группу тумблеров, одни кон- такты которых подключены к шине логического нуля, а другие через резисторы сопротивления 4,7 кОм, общее количество которых равно разрядности адресной шины, подключены к шине ад- реса.

Формирователь 2 данных - это группа тумблеров, одни контакты которых подключены к шине логического нуля, а другие через резисторы сопротивления 4,7 кОм подключены к входам буферного регистра 8. Количество тумблеров равно числу разрядов шины данных и соответствует числу индикаторов в узле 3 индикации.

Узел 4 формирования управляющих сигналов состоит из тумблеров Пуск/Стоп, Чтение/Запись (ЧТ/ЗП), запоминающего устройства ввода/вывода (ЗУ/УВВ) и схемы подавления дроберга.

Узел 6 выдачи управляющих сигналов может быть реализован на ПЗУ, на адресные входы которого поступают сигналы ТТ и Т2 из узла 5 синхронизации и сигнал ЧТ/ЗП от узла 6 формирования упр ав ляющих с и гн ало в.

Узел 7 выдачи слова состояния может быть реализован на ПЗУ, на адресные входы которого поступают сигналы ЧТ/ЗП, ЗУ/УВВ с узла 4, сигнал SYNC с выхода узла 6, на вход разрешения подается -логический О.

Узел 7 (ПЗУ) программируется так, что Ј его выходов, подключенных к ши

0

5

0

не данных, снимается слово состояния микропроцессора,- соответствующее выбранной операции.

Имитатор работает следующим образом.

Переключением тумблеров формирователя 1 формируется требуемый адрес памяти или устройства ввода/вывода.

Для выполнения операции записи в память или устройство ввода/вывода переключением тумблеров формирователя 2 формируют требуемые данные записи переключением тумблеров ЧТ/ЗП, ЗУ/УБВ узла 4, выбирается режим чтения данных из памяти или из устройства ввода/вывода, запись данных в память или в устройство ввода/вывода.

Переключением тумблера Пуск/Стоп разрешается работа для узла 5 синхронизации. С выхода генератора 11 на С-вход триггера 9 поступает серия синхроимпульсов ТО, с прямых выходов триггеров 9 и 10 на вторые и третьи входы узла 6 выдачи управляющих сигналов выдаются синхросерии Т1 и Т2 (фиг. 4 и 5). На вход узла 6 поступает сигнал ЧТ/ЗП из узла 4. С выходов узла 6 на шину управления выдаются сигналы DBIN и WR, с третьего выхода узла 6 на шину управления выдается сигнал SYNC, который поступает на вход узла 7, на который также поступают сигналы ЧТ/ЗП и ЗУ/УВВ с узла 4. По сигналу SYNC с выходов узла 7 слово-состояние, соответствующее выбранному режиму, поступает на шину данных. С выхода узла 6 на вход регистра 8 поступает система управления. При осуществлении операции чтения или выдаче слова-состояния регистр 8 переводится в состояние высокого импеданса.

При динамическом режиме работы постоянно по заданному адресу производится запись одних и тех же данных в память.

В динамическом режиме устройство многократно (циклически) повторяет одну и ту же операцию; только запись в память, только чтение из памяти, только запись в устройство ввода/вывода, только чтение из устройства ввода/вывода. Обращение производится по установленному одному и тому же адресу и выдаются одни и те же данные , (для операции записи).

При наличии сигнала SYNC устройство выдает на ЩД слово-состояние с узла 7 выдачи, при этом на управляющий вход регистра 8 приходит сигнал, запрещающий передачу информации на ПЩ.

При операции чтения (фиг. 5) на регистр 8 ,также приходит управляющий сигнал, запрещающий передачу информации на ЩД, так как по ЩД должна приниматься информация из подключенного описываемого устройства.

Использование устройства не требует от оператора досконального знания временных диаграмм для различных операций (запись/чтение в память, запись/чтение в устройство ввода/вывода), а. также оператор может не запоминать слова-состояния для каждой операции.

Именно в динамическом режиме работы отлаживаемой аппаратуры возникают помехи, шумы и ложные срабатывания микросхем, нарушающие работу этой аппаратуры, применение устройства обеспечивает устранение неисправности в отлаживаемой аппаратуре.

По принципу действия предлагаемое устройство - имитатор локальной шины микропроцессора. Содержимое узла 6 (по сути блока памяти), а также узла 7 однозначно связано с типом микропроцессора, на котором базируется отлаживаемая или разрабатываемая аппаратура.

Формула изобретения

Имитатор локальной шины микропроцессора, содержащий формирователь

5

5

0

5

данных, узел синхронизации, узел индикации, буферный регистр, узел формирования управляющих сигналов, узел выдачи слова состояния, причем выходы буферного регистра подключены к шине данных микропроцессора, к выходам узла выдачи слова состояния и к входам узла индикации, выход пуска/стопа узла выдачи управляющих сигналов соединен с входом пуска/стопа узла синхронизации, о тличающий- с я тем, что, с целью упрощения, имитатор содержит узел выдачи управляющих сигйалов, формирователь адреса, подключенный к шине адреса микропроцессора, первый выход узла выдачи управляющих сигналов соединен с управляющим входом буферного регистра, информационные входы которого соединены с выходами формирователя данных, второй выход узла выдачи управляющих сигналов соединен с входом синхронизации узла выдачи слова состояния и остальными выходами узла выдачи управляющих сигналов и подключен к шине управления микропроцессора, выходы узла синхронизации соединены с адресными входами узла выдачи управляющих сигналов, вход чтения/записи которого соединен с выходом чтения/записи узла формирования управляющих сигналов и первым адресным входом узла выдачи слова состояния, второй адресный вход которого роединен с выходом задания режима работы узла выдачи слова состояния -узла формирования управляющих сигналов,

Авторы

Даты

1991-04-23—Публикация

1987-10-09—Подача