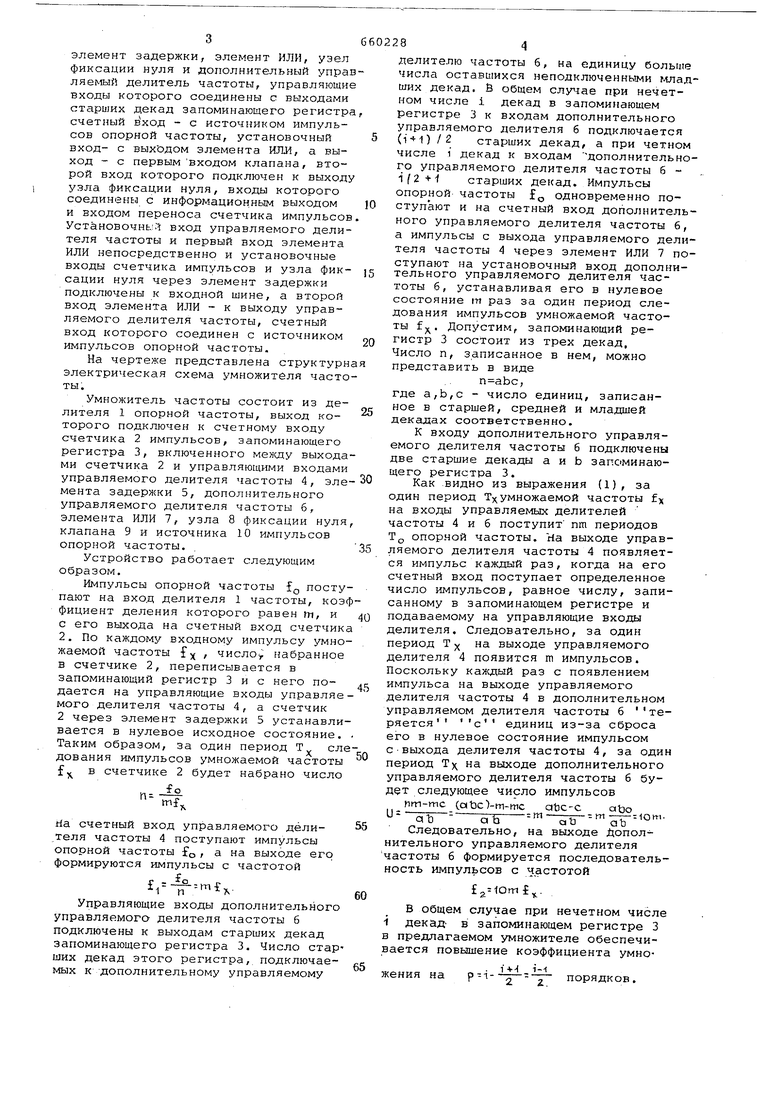

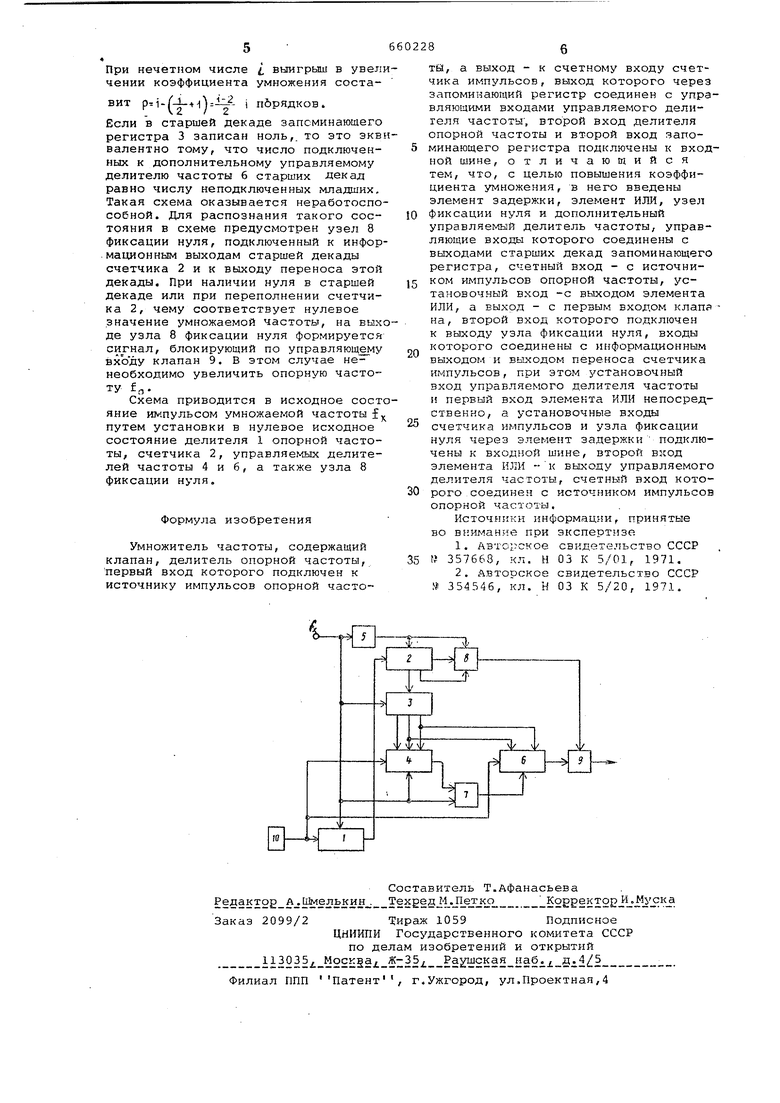

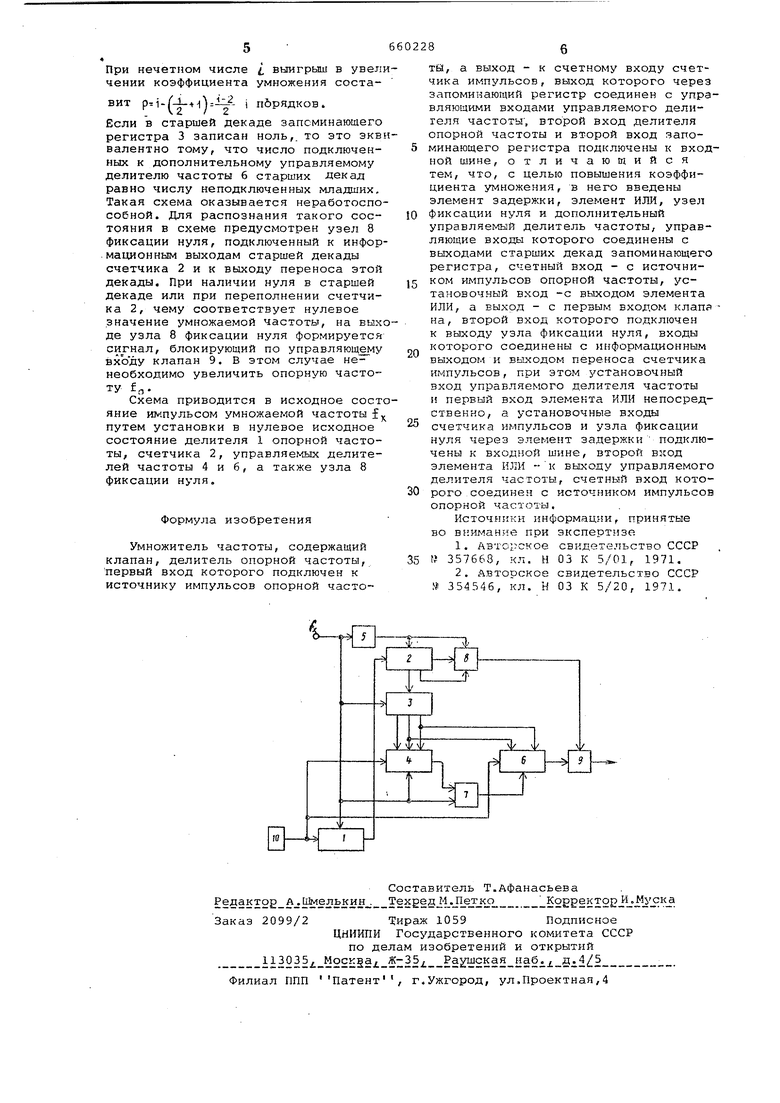

Изобретение относится к импульсной технике и может быть использова но для получения высоких значений коэффициента умножения частоты. Известен умножитель частоты разомкнутого типа, осуществляющий умножение частоты следования периодических импульсов и построенный на .базе генераторов импульсов образцовой частоты, делителей частоты, счетчиков импульсов и запоминающих регистров l . Принцип действия этого умножителя частоты состоит в выполнении сче но-импульсным методом операций деле ния текущего периода следования импульсов на результат и измерения предыдущего периода следования импульсов входной частоты. Умножение входной частоты в W раз достигаетс тем, что частота заполнения периода входной частоты при выполнении опер ции деления в m раз больше частоты заполнения, используемой при измере нии временного интервала. Однако это устройство имеет огра .ниченную величину коэффициента.умно жения. Наиболее близким по технической сущности к предложенному является устройство, содержащее счетчик, запоминающий регистр, управляемый делитель частоты, делитель опорной частоты и клапан. Коэффициент умножения в этом устройстве равен коэффициенту деления делителя опорной частоты 2. Недостатком этого умножителя частоты при заданной точности умно- жения, определяемой точностью измерения периода умножаемой частоты, является то, что коэффициент умножения ограничен максимально допустимым значением образцовой частоты. Последняя, в свою очередь, огранич ивается быстродействием элементов устройства. Цель .«3:Обр етения - поншиен ие коэффициента умножения. Это достигается тем, что в умножитель частоты, содержащий клапан, делитель опорной частоты, первый вход которого подключен к источнику импульсов опорной частоты, а выходк счетному входу счетчика импульсов, выход которого через запоминающий регистр соединен с управляющими входами управляемого делителя частоты, второй вход делителя опорной частоты и второй вход запоминакмцего регистра подключены к входной шине, введены 3 элемент задержки, элемент ИЛИ, узел фиксации нуля и дополнительнь-ай упра делитель частоты, управляющи входы которого соединены с выходами старших декад запоминающего регистр счетный вход - с источником импульсов опорной частоты, установочный вход- с выходом элемента ИЛИ, а выход - с первым входом клапана, второй вход которого подключен к выход узла фиксации нуля, входы которого соединены с информационным выходом и входом переноса счетчика импульсо Установочны. вход управляемого дели теля частоты и первый вход элемента ИЛИ непосредственно и установочные входы счетчика импульсов и узла фик сации нуля через элемент задержки подключены к входной шине, а второй вход элемента ИЛИ - к выходу управляемого делителя частоты, счетный вход которого соединен с источником импульсов опорной частоты. На чертеже представлена структур электрическая схема умножителя част ты. Умножитель частоты состоит из де лителя 1 опорной частоты, выход которого подключен к счетному входу счетчика 2 импульсов, запоминающего регистра 3, включенного ме-ящу выхода ми счетчика 2 и управляющими входами управляемого делителя частоты 4, эле мента задержки 5, дополнительного управляемого делителя частоты б, элемента ИЛИ 7, узла 8 фиксации нуля клапана 9 и источника 10 импульсов опорной частоты. . Устройство работает следующим образом. Импульсы опорной частоты f посту пают на вход делителя 1 частоты, коэ фициент деления которого равен гп, и с его выхода на счетный вход счетчик 2. По каждому входному импульсу умно жаемой частоты f , числоу набранное в счетчике 2, переписывается в запоминающий регистр 3 и с него подается на управляющие входы управляе мого делителя частоты 4, а счетчик 2 через элемент задержки 5 устанавли вается в нулевое исходное состояние Таким образом, за один период Т сл дования импульсов умножаемой частоты f в счетчике 2 будет набрано число На счетный вход управляемого делителя частоты 4 поступают импульсы опорной частоты а на выходе его формируются импульсы с частотой - fa n -- лУправляющие входы дополнительного управляемого делителя частоты б подключены к выходам старших декад запоминающего регистра 3. Число стар ших декад этого регистра,, подключаемых к дополнительному управляемому 8 делителю частоты б, на единицу больше числа оставшихся неподключенными младших декад. В общем случае при нечетном числе i декад в запоминающем регистре 3 к входам дополнительного управляемого делителя б подключается () /2 старших декад, а при четном числе 1 декад к входам дополнительного управляемого делителя частоты б if2- / старших декад. Импульсы опорной частоты Q одновременно поступают и на счетный вход дополнительного управляемого делителя частоты б, а импульсы с выхода управляемого делителя частоты 4 через элемент ИЛИ 7 поступают на установочный вход дополнительного управляемого делителя частоты б, устанавливая его в нулевое состояние IT) раз за один период следования импульсов умножаемой частоты f. Допустим, запоминающий регистр 3 состоит из трех декад, Число п, записанное в нем, можно представить в виде , где а,Ь,с - число единиц, записанное в старшей, средней и младшей декадах соответственно. К входу дополнительного управляемого делителя частоты б подключены две старшие декады а и b запоминающего регистра 3. Как видно из выражения (1), за один период TXумножаемой частоты fx на входы управляемых делителей частоты 4 и 6 поступит nm периодов Тр опорной частоты. На выходе управляемого делителя частоты 4 появляется импульс каждый раз, когда на его счетный вход поступает определенное число импульсов, равное числу, записанному в запоминающем регистре и подаваемому на управляющие входы делителя. Следовательно, за один период Т X на выходе управляемого делителя 4 появится m импульсов. Поскольку каищый раз с появлением импульса на выходе управляемого делителя частоты 4 в дополнительном управляемом делителя частоты 6 теряется с единиц из-за сброса его в нулевое состояние импульсом свыхода делителя частоты 4, за один период TX на выходе дополнительного управляемого делителя частоты б будет следующее число импульсов nin-mc (abc)-m-mc abCCabo - m -T-:1OttlFT cTb - ati Следовательно, на выходе Дополнительного управляемого делителя частоты 6 формируется последовательность импульсов с частотой . В общем случае при нечетном числе i декад- в запоминающем регистре 3 в предлагаемом умножителе обеспечивается повышение коэффициента умно1 -( жения на порядков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования им-пульСОВ | 1979 |

|

SU839031A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU945962A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU894847A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Умножитель частоты следования периодических импульсов | 1976 |

|

SU540363A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| Умножитель частоты следования импульсов | 1979 |

|

SU809526A1 |

Авторы

Даты

1979-04-30—Публикация

1976-11-10—Подача