Изобретение относится к вычислительной технике и предназначено для реализации сетевых управляющих структур с распределенной вычислительной мощностью.

Цель изобретения - уменьшение объема оборудования и исключение потерь информации.

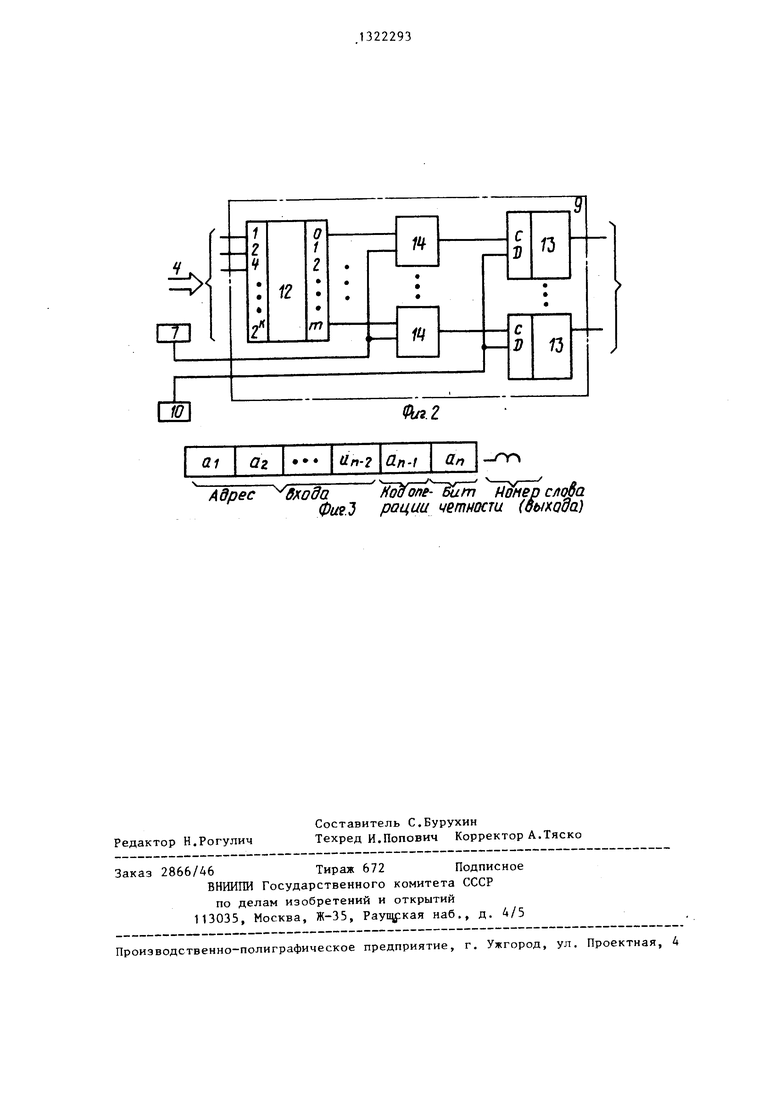

На фиг,1 представлена блок-схема устройства; на фиг.2 - схема регистра; на фиг.З - структура размещения информации в блоке памяти.

Устройство содержит генератор 1 импульсов, счетчик 2, блок 3 памяти,

сматриваемого слова программы, являющийся одновременно кодом номера очередного коммутируемого выхода устройства. Этот код поступает на вход

5 блока 3 памяти и на вход блока 9, подготавливая к приему информации, соответствующий D-триггер 13, На первом выходе блока 3 памяти появляется код адреса входа {а,,

О поступающий на управляющий вход мультиплексора 8, в результате чего на выходе последнего появляется сигнал, зквивалентный сигналу на одном из входов устройства, номер которого -у .. у у

первую 4 и вторую 5 шины адреса, пер- ответствует коду на управляющем входе вый элемент 6 равнозначности, ждущий мультиплексора 8. Этот сигнал посту- мультивибратор 7, мультиплексор 8, блок 9 вьадачи информации, элемент И 10 и второй элемент 11 равнозначности.

Блок 9 () содержит дешифра20

пает на первый вход элемента 6 равнозначности. Одновременно на второй вход этого элемента поступает сигнал а. с второго выхода блока 3 памяти.

тор 12, блок 13 триггеров и блок 14 элементов И.

30

При этом на выходе элемента 6 появляется сигнал прямой или инверсный по отношению к сигналу на его первом Принцип работы устройства заключа-, входе в зависимости от значения а„,, , ется в последовательном опросе вход- равного 1 или О соответственно. Этот ных сигналов, их логической обработки сигнал поступает на второй вход эле- и выдаче в соответствии с программой мента И 10 и активизирует на его вы- коммутации в блок 9, который обеспечивает хранение сигналов до следующего цикла работы.

Структура размещения информации в блоке 3 памяти такова (фиг.З), что каждому выходу устройства соответствует одно слово в программе. При этом

слово образовано множеством ячеек па- 5 держит информации об отказе блока мяти 1,2,...п, из которых 1... (п-2) памяти (содержит четное число еди- содержат закодированный адрес входа устройства а, ,а,а,,.. .,а„.,, с которым выход, соответствующий данному слову, должен быть связан. Код, записанный в ячейках 1 ... (п-2), активизирует при считывании каждого слова первый выход блока 3 памяти. Ячейка под номером п-1 содержит код операции (а,) над переменной, пере- тового импульса генератора 1, на син- даваемой по ;аналу вход-выход устрой- хронизирукщий вход блока 9 происходит ства. Ячейка под номером п содержит контрольный бит информации (а), до- полняннций выходной код блока 3 памяти

ходе эквивалентный сигнал при наличии на первом входе сигнала, равного 1, поступающего с выхода элемента 11. Последнее имеет место в случае, если код, образуемый всеми сигналами на входе элемента 11, используемого в функции контроля на четность, не сониц). В противном случае на выходе элемента И 10 появляется сигнал, равный нулю, независимо от значения сигнала на его втором входе. Сигнал с вькода элемента И 10 поступает на информационный вход блока 9. С поступлением сигнала, вырабатьшаемого мультивибратором 7 под воздействием такзапись сигнала, присутствующего на его информационном входе в соответствующий D-триггер 13, подготовленный

до четного. Две последние ячейки ак- к записи кодом на первой адресной юи- тивизируют при считьшании каждого не 4. При этом значение сигнала на слова соответственно второй и третий выходы блока 3 памяти.

В процессе работы устройства гене- ратор 1 вьфабатывает очередной импульс, переводящий счетчик 2 в новое состояние. При этом на его выходе поочередном коммутируемом выходе устройства становится эквивалентным (или инверсным согласно программе) по отношению к значению сигнала на одном из ее входов.

Таким образом, соответствие множества выходов устройства множеству

является код номера очередного просматриваемого слова программы, являющийся одновременно кодом номера очередного коммутируемого выхода устройства. Этот код поступает на вход

блока 3 памяти и на вход блока 9, подготавливая к приему информации, соответствующий D-триггер 13, На первом выходе блока 3 памяти появляется код адреса входа {а,,

поступающий на управляющий вход мультиплексора 8, в результате чего на выходе последнего появляется сигнал, зквивалентный сигналу на одном из входов устройства, номер которого со

ответствует коду на управляющем входе мультиплексора 8. Этот сигнал посту-

пает на первый вход элемента 6 равнозначности. Одновременно на второй вход этого элемента поступает сигнал а. с второго выхода блока 3 памяти.

0

При этом на выходе элемента 6 появляется сигнал прямой или инверсный по отношению к сигналу на его первом , входе в зависимости от значения а„,, , равного 1 или О соответственно. Этот сигнал поступает на второй вход эле- мента И 10 и активизирует на его вы-

ходе эквивалентный сигнал при наличии на первом входе сигнала, равного 1, поступающего с выхода элемента 11. Последнее имеет место в случае, если код, образуемый всеми сигналами на входе элемента 11, используемого в функции контроля на четность, не содержит информации об отказе блока памяти (содержит четное число еди- тового импульса генератора 1, на син- хронизирукщий вход блока 9 происходит

ниц). В противном случае на выходе элемента И 10 появляется сигнал, равный нулю, независимо от значения сигнала на его втором входе. Сигнал с вькода элемента И 10 поступает на информационный вход блока 9. С поступлением сигнала, вырабатьшаемого мультивибратором 7 под воздействием такдержит информации об отказе блока памяти (содержит четное число еди- тового импульса генератора 1, на син- хронизирукщий вход блока 9 происходит

запись сигнала, присутствующего на его информационном входе в соответствующий D-триггер 13, подготовленный

к записи кодом на первой адресной юи- не 4. При этом значение сигнала на

к записи кодом на первой адресной юи не 4. При этом значение сигнала на

очередном коммутируемом выходе устройства становится эквивалентным (или инверсным согласно программе) по отношению к значению сигнала на одном из ее входов.

Таким образом, соответствие множества выходов устройства множеству

3132229

его входов устанавливается программой, хранящейся в блоке 3 памяти. В процессе работы устройства производится последовательная циклическая запись информации в каждый D-триггер 5 13 блока 9, где она сохраняется на протяжении цикла работы счетчика 2, При этом каждый раз адрес источника информации (входа устройства) определяется кодом на второй адресной шине 10 5, а характ;ер операции над переменной при переносе ее значения с входа на выход устройства логическим уровнем

сигнала а„,, на втором выходе блока 3 памяти. При искажении информации, 15 содержащейся в блоке 3 памяти и нарушающей четность кода на входе элемента 11, на его выходе появляется сигнал нулевого уровня, вследствие чего.

в подготовленный кодом на первой ад- 20 ности, первый, второй, третий входы, ресной шине 4 D-триггер 13 блока 9 записывается логический О независимо от значения сигнала, считанного со входа устройства. При считывании адресов, неискаженных отказом, экви- -5 валентность выхода устройства значению, обусловленному программой коммутации и сигналами на ее входе, сохраняется.

выходы которого соединены соответственно с первого по третий выходами блока памяти и первым входом элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента равнозначности и первым информационным входом блока выдачи информации, вход которого соединен с выходом счетчики.

Формула изобретения

1. Устройство для сопряжения информационных каналов программно-коммутируемой логической сети, содержа- 35 щее генератор импульсов, счетчик, блок памяти, первый элемент равнозначности, ждущий мультивибратор, мультиплексор и блок выдачи информа2. Устройство по п.1, о т л и - чающееся тем, что блок выдачи информации содержит дешифратор, блок элементов И и блок триггеров, причем второй, первый информационные и синхронизирующий входы блока соеди нены соответственно с входом дешифратора, информационным входом блока триггеров и первым входом блока элементов И, выход дешифратора подклюции, причем выход блока выдачи инфор- 0 чен к второму входу блока элементов

мации соединен с выходом устройства для подключения выходного информационного канала, выход генератора импульсов соединен- с тактирующим входом счетчика и входом ждущего-мультивибратора, выход которого соединен с входом синхронизации блока выдачи информации выход счетчика соединен с адресным входом блока памяти, первый выход которого соединен с управляющим входом мультиплексора, информационный вход которого соединен с входом устройства для подключения входного информационного канала, выход мультиплексора соединен с первым входом первого элемента равнозначности, второй вход которого подключен к второму выходу блока памяти, отличающееся тем, что, с целью уменьшения объема оборудования и исключения потерь информации, в него введены элемент И и второй элемент равнозначности, первый, второй, третий входы,

выходы которого соединены соответственно с первого по третий выходами блока памяти и первым входом элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента равнозначности и первым информационным входом блока выдачи информации, вход которого соединен с выходом счетчики.

2. Устройство по п.1, о т л и - чающееся тем, что блок выдачи информации содержит дешифратор, блок элементов И и блок триггеров, причем второй, первый информационные и синхронизирующий входы блока соединены соответственно с входом дешифратора, информационным входом блока триггеров и первым входом блока элементов И, выход дешифратора подклюИ, выход которого соединен с входом синхронизации блока триггеров, выход которого соединен с выходом блока.

10

Адрес

-nn

ffxoda1Шопе Вигп c/io6a

Фи. роции чвтност (оыкода

Редактор Н.Рогулич

Составитель С.Бурухин

Техред И.Попович Корректор А.Тяско

Заказ 2866/46Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рау1цркая наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, Д

ff.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для программного управления намоточным станком | 1985 |

|

SU1259216A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

| Программируемый контроллер | 1984 |

|

SU1262451A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

Изобретение относится к области вычислительной техники и предназначено для реализации сетевых управляющих структур с распределенной вычислительной мощностью. Цель изобретения - уменьшение объема оборудования и исключение потерь информации. Устройство содержит генератор 1 импульсов, счетчик 2, блок 3 памяти, первую, вторую шины адреса 4,5, первый зле- мент 6 равнозначности, ждущий мультивибратор 7, мультиплексор 8, блок 9 вьщачи информации, элемент И 10, второй элемент 11 равнозначности. При случайных искажениях содержимого отдельных ячеек блока памяти в устройстве происходит автоматическая блокировка каналов связи, работу которых регламентируют слова программы, включающие ячейку с искаженной информацией. 1 з.п. ф-лы, 3 ил. € (Л

| Система циклового программногоупРАВлЕНия | 1978 |

|

SU819792A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 3810118, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-07—Публикация

1986-01-02—Подача