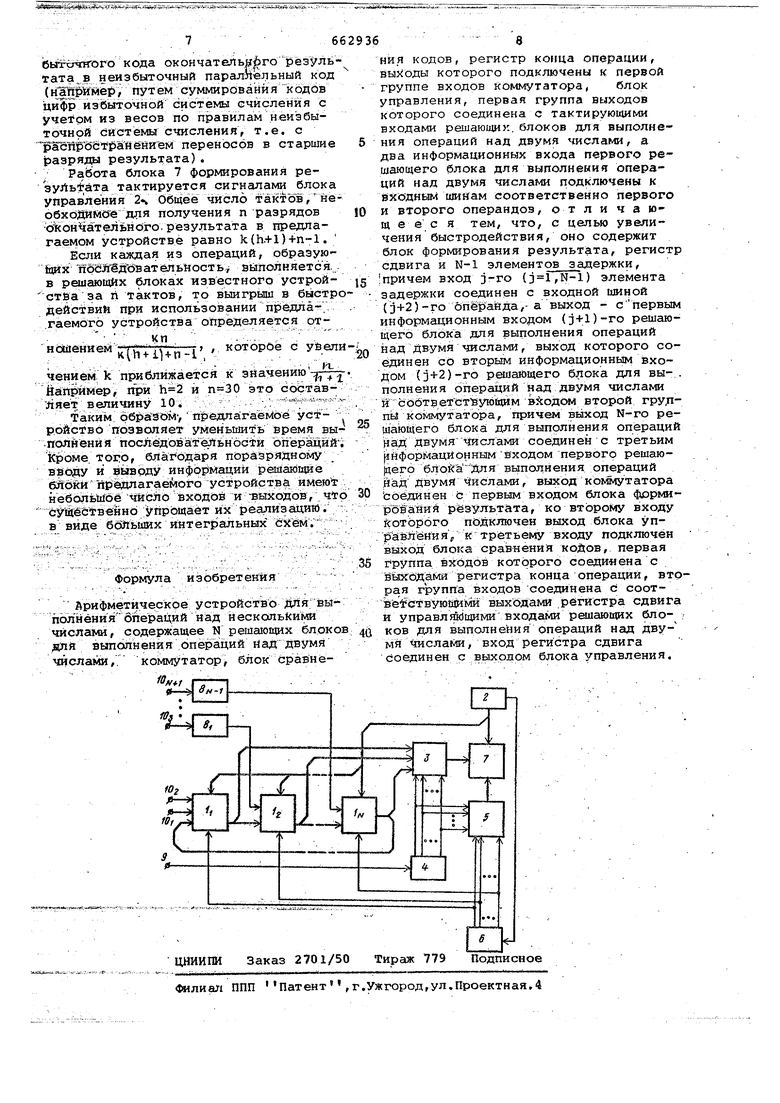

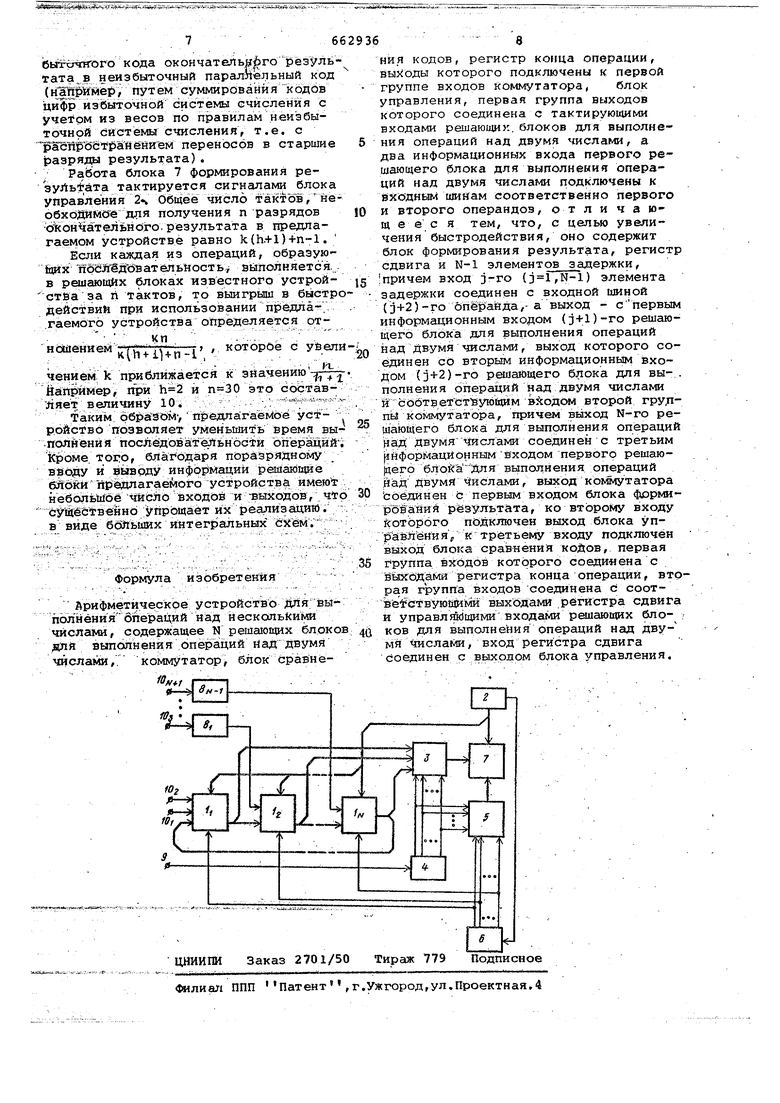

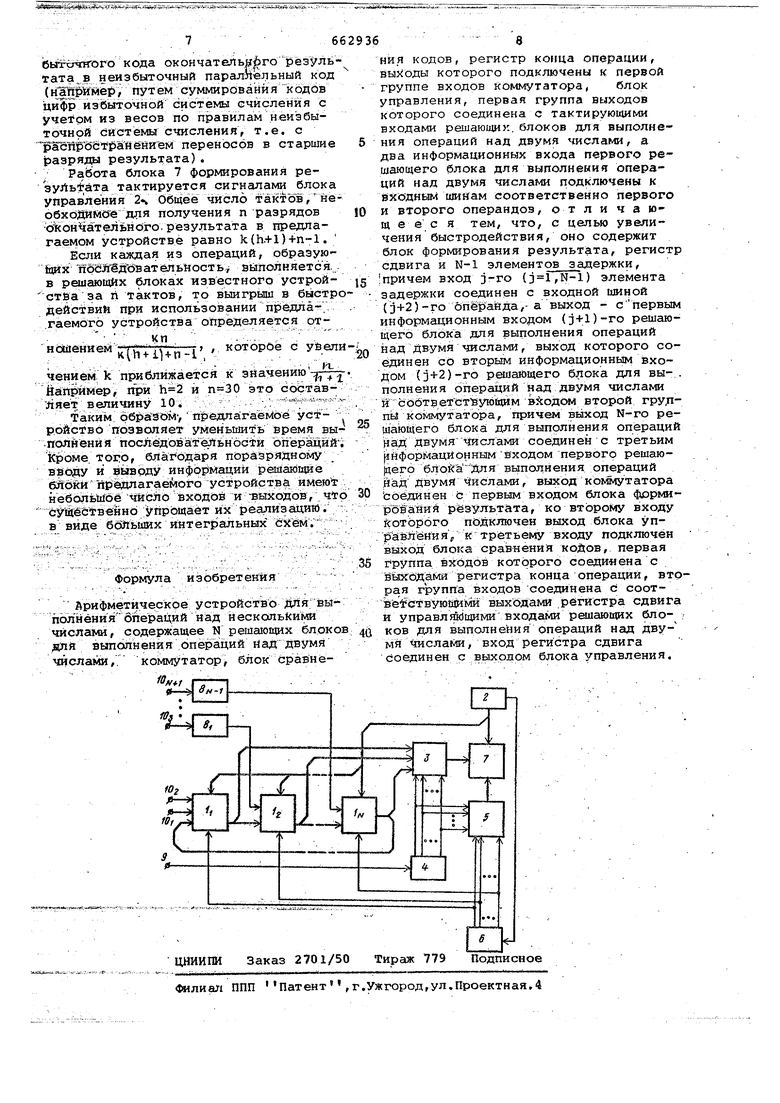

.J,- -.......- J :. - . .v....x.-u:-. Целью изобретения является увеличение быстродействия. В предлагаемом устройстве это достигается тем, что оно содержит блок формирования результата, регистр сдвига и N-1 эле-ментов задержки, причем вход j-ro (, N - 1) элемента задержки cqeдинен с входной шиной (j+2)-ro опе ранда, а выход - с первым информационным входом (j+l)-ro решающего -блока для выполнения операций над двумя чис лами, выход которого соединен со вто рым информационным входом (j+2)-ro решающего блока для выполнения операций над двумя числами и соответствующим входом второй группы коммутатора причем ёыход N-ro решающего блока для выполнения операций над двумя числами соединен с третьим информационным вхо дом первого решающего блока для выполнения операций над двумя числами, выход коммутатора соединен с первым входом блока формирования результата ко второму входу которого подключен выход блока управления, к третьему входу подключен выход блока сравнени кодов, первая группа входов которого соединена с выходами регистра конца операции, вторая группа входов соединена с соответствующими выходами регистра сдвига и управляющими входа ми решающих блоков для выполнения операций над двумя числами, вход регистра сдвига соединен с выходом бло ка управления.. На чертеже представлена структурная схема предлагаемого арифметического устройства. Оно содержит N решающих блоков 1ц для выполнения операций над двумя числами, блок управления 2, коммутатор 3, N-разрядный регистр 4 конца операции, блок 5 сравнения кодов, N-разрядный регистр сдвига 6, блок 7 формирования результата, N-1 элементов задержки 81..г управляющую шину 9 и входные шины операндов 10|-10||(4.1 , В качестве решающих блоков применяют блоки, позволяющие совмещать во времени процессы по разрядного ввода операндов и поразрядного формирования результата, на. ч:инйя со старших разрядов. Для предртавлениярезультата в решающих бЛрках применяют избыточйую однйродную позиционную систему счисления,цифры которой кодируются неиэбы:тЬчным двоичным кодом tO/l3 -Цифры из бытЪчной систег ы счисления представл ются на выходах решающих блоков единичными или нулевыми сигналами на различных шинах, где cj, количество цифр (символов) избыточной системы счисления. Например, для двоичной систе№л счисления с цифрами ,r,6,ljj имеет место Чис ло ре{яающих блоков не зависит от чис ла операций , образующих последрва(ельность, и определяется выражением Vhr JhTiL где п-разрядность операн-. дев, ah- задержка формирования первого разряда результата (выраженная в числе тактов) в решающих блоках I(-IN после ввода первых разрядов операндов. Например, если , то после ввода первых разрядов операндов на первом такте вычисления пер-. вый разряд результата получают через два такта, т.е. на третьем такте. Выходы каждого решающего блока 1j (,. N-1) подключены к группе входов решающего .блока Ij+t, а выходы решающего блока 1 yj соединены с группой входов решающего блока 1. Группа выходов блока управления 2 подключена к тактирующим входам блока 7 фор1«1рования результата и к тактирующим входам решающих блоков , выходы которых через коммутатор 3 соединены с информационными входами блока 7 формирования результата, а к управляющему входу последнего подключен выход блока 5 сравнения кодов. Выходы регистра 4 конца операции подключены к управляющим входам коммутатора 3 и к одной группе информационных входов блока 5 сравнения кодов, вторая группа йнформа1;ионных входов которого соединена с выходами регистра сдвига 6. Выход каждого j-го разряда регистра сдвига 6 (,N) подключен к управляющему входу решающего, блока Ij, а управляющий вход регистра сдвига б соединен с одним выходом блока управления 2. Входные шины операндов 10. и 102 подключены к двум соответствующим информационным входам решающего блока If, а к одному информационному ВХОДУ каждого решающего блока 1(,N) через элементы задержки 8J-I подключены входные шины операндов . Управляющая шина 9 подключена к цепи выдачи кода регистра 4 конца операции. Блок 7 формирования результата является преобразователем чисел, представленных последовательным избыточным кодом, в неизбыточную (каноническую) систему счисления. .. Допустим, необходимо выполнить последовательность, состоящую из k двухместных операций. Если число операций, образующих последовательность, равно числу решающих блоков, т.е. , то последовательность oneраций выполняется за один цикл. Если же , то процесс вычисления условно разбивается на несколько циклов, в каждом из которых выполняется не более N операций. В первом цикле вычислений на входные шины операндов lO -lOn+i поступает первая группа, включающая N+1 операндов, представленных последовательным кодом. В последующих циклах на входные шины операндов lOj-lOK-n поступают

:группы из N операндов (в последнем цикле число операндов может быть меньше N).

В исходном состоянии в первом разряде регистра сдвига 6 записана единица, а в регистре 4 конца операции единица записана в разряде с номером 5

,ecAMK(modN) L N, если к (modN) 0.

в каждом i-M такте первого цикла на, ю входные шины операндов ( + j поступают i-e разряды соответствуюй х операндов. Каждый решающий блок li-lf выполняет определенную операцию, а

тактирующие сигналы для них вырабатывает блок управления 2. После выполнения первых h+1 тактов на выходах решающего блока 1 присутствует первый разряд избыточного кода первого промежуточного результата. В (h+2)-M такте этот разряд начинает Обрабатываться в решающем блоке Ij, для которого данный разряд является первым разрядом одного операнда. Одноименный разряд неизбыточного кода

другого операнда для решающего блока 25 12 поступает с выхода элемента задержки 8j ,который задерживает разряды операнда на такое же число тактов, как и решающий блок Ij, т.е. на h+1 тактов. В дальнейшем разряд промежу- 30 точного результата, полученный в решающем блоке , в следующем такте начинает обрабатываться в решающем блоке 1 и т.д., т.е. разряд промежуточного результата, полученный в i-м 35 такте на выходах решающего блока Ij используется в качестве очередного

разряда операнда в решающем блоке на (i+D-M такте. Каждый элемент задержки 8 j задерживает разряды соот- ,,, ветствующих операндов на j(h+l) тактов, обеспечив.ая тем самым подачу разрядов операндов на вход решающего блока Ij4i одновременно с разрядом промежуточного результата, сформированного в решающем блоке Ij , который поступает на другие информационные входы решающего блока Ij+i . После . выполнения первых n+h тактов решающий блок 1 j выдает на входы решгаощего блока 12 п-й(последний) разряд перво- 50 го промежуточного результата, т.е. освобохедается от выполнения возложенной на него операции, в последующих тактах решающий блок 1 может обрабатывать разряды промежуточного ре-- -55 зультата, формирующиеся в решающем блоке IN т

Число N выбрано таким, что к моменту появления первого разряда промежуточного результата на выходах gQ решающегй блока IK решающий блок 1 оказывается свободным.

На этом заканчивается первый цикл вычислений.

Второй цикл вачислений начинается с момента поступления первого (старfiiero) разряда промежуточного результата с выходов решающего блока 1) на входы решающего блока 1{. Одновременно с этим на входные шины операндов Юз -10 41Н инают поступать разряды операндов следующей группы. Циклы работы устройства повторяются до тех пор, пока на входные шины операндов 10; не будут приняты операнды всех k операций,

Одновременно с подачей последней группы операндов на управлж1щую шину 9 поступает си.гнал, действующий до окончания работы устройства и осущесвляющий выдачу кода регистра 4 конца операции. Номер Л разряда регистра 4 конца операции, в котором записана единица перед .началом вычислений, соответствует номеру решающего блока который в последнем цикле выполняет k-ю операцию в заданной последователности операций.

В каждом цикле вычислений после выполнения h+1 очередных тактов по сигналу блока управления 2 осуществляется сдвиг единицы в регистре сдви;га 6 на один разряд вправо и в результате этого на управляющий вход решающего блока ij поступает, единичный сигнал с выхода разряда регира сдвига 6. Этот сигнал тактируется сигналами блока управления 2, поступающими на определенные тактирующие шины решающих блоков , в результате чего решающий блок 1J устанавливается в исходное состояние для выполнения определённой операции непосредственно перед тактом поступления на его входы первых разрядов операндов данной операции.

Таким образом, в момент формирования первого разряда промежуточного результата в решающем блоке 1J присутствует единичный сигнал на выходе j-ro разряда регистра сдвига 6. В . последнем цикле работы после сдвига единицы в разряд с номером об регистра сдвига 6 решающий блок начинает .вы11олнять последнюю операцию в задан:ной последовательности и на его выходах в каждом последующем такте прйсутствуют очередные разряды окончательного результата. Так как в исходном состоянии в регистре 4 конца операции записана единица в разряде с номером об, то после сдвига единицы в регистре сдвига 6 в разряд с номером и блок 5 сравнения кодов выдает на. управляющий вход блока 7 формирования результата сигнал, соответствую щий равенству кодов, который иниции-: рует н:ачало работы блока 7 формирования результата. В этом случае очередные разряды окончательного результата с выходов решающего блока 1 у, через коммутатор 3, которым управляет регистр 4 конца операции, поступают на 1нформационные ;входы блока 7 формирорания результата, где осуществляется преобразование последовательного избьггхгчпгого кода окончательного тата.в неизбыточный параллельный код (нШримёр, путем суммирования кодов цифр избыточной системы ечйсленйя с учетом из весов по правилам неиэбыточнрй системы счисления, т.е. с рЗспрбстрайёнием переносов в старшие разряда результата). Работа блока 7 формирования реsyrtbtaxa тактируется сигналаш блока управления 2-k Общее число тактоТв, не обходимее для получения п разрядов Ькончё1тельного. результата в предлагаемом устройстве равно k{h.+l)+n-l. Если казкдая из операций, образую {цйх йрёлёДдватёЛЬМостьу вйполкяется, в решающих блоках известного устрой стйаэа п тактов, то выигрыш в быстр действий при использовании прёдла-.. .гаемото устройства определяется от к п найбнием , -1 УЧ чением k приближается к эначению р;Йап ймер, при и это соЬтавЛяеТ величину 10; ..- л, - ;; :; ;--Таким. рбраЭбМ,Il|)eдЛaгa€ fOё устройство позволяет уменьшить время вы .пояйёнйя последовательности 6пёрЩйЙ Кроме, того, благодаря поразрядному вйоду и выводу информации решающие ейбйй предлагаемого устройства нмеют небсхпШбё Числовходов и -выходов,; ч йуй1ё&Фвенно уйрЬща:ёт их в виде больших интег ральных ckeM. Формула изобретения Арифметйческре устройство ДЛя;выполйёния 6пераций на:д йескаль ими числами, содержащее N решающих блоко для выполнения операций йаДдвумя числами,, коммутатор/ блок сравнения кодов, регистр конца операции, выводы которого подключены к первой группе входов коммутатора, блок управления, первая группа выходов которого соединена с тактирующими входами решающи :, блоков для выполнения операций над двумя числами, а два информационных входа первого решающего блока для выполнения операций над двумя числами подключены к входным Шияам соответствейно первого и второго операндов, отличающ ее с я тем, что, с целью увеличения быстродействия, оно содержит блок формирования результ;ата, регистр сдвига и N-1 элементов задержки, ;причем вход j-ro (,N-l) элемента задержки соединен с входной шиной (J+2)-го опёрайда,-а выход - спервым информационным входом (j+l)-ro решающего блока для выполнения операций йад Двумя числами, выход которого соединен сР вторым информационным входом (j+2)-ro рояающего блока для вы- . полнения операций над :двумя числами И србтветствующйм вводом второй гру,пnbJ коммутатора, причем выход N-ro рещающего блока для выпрлнения операций над Двумя числами соединей с третьим |1Йформационным входом первого решаю|цег6 бЛрйа Для выполнения операций Над Двумя числами, выход кО№1утатора соединен Ь первым входом блока фюрмирб айий результата, ко второму входу котЬрбго подключен выход блока Управлёни я , к третьему входу подключен выход блока сравнения койов, первая группа входов которого соединена с выходами регистра конца операций, втррая группа входов соединена с соотйё1 ствую шмй выхбдамй регистра сдвига и управляйащими входами решающих бло- : ков для выполнения операций над двумя шслами, вход регистра сдвига с о еди и ен с выход ом блок а у правл ени я.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Вычислительное устройство для решения дифференциальных уравнений | 1979 |

|

SU935954A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

Авторы

Даты

1979-05-15—Публикация

1976-08-01—Подача