I

Изобретение относится к вычислительной технике и может быть применено цля решения систем цифференциальных уравнений.

Известно устройство, решающее дифференциальные уравнения, представляющие собой интегрирующее устройство и предназначенное цля решения цифференциаль- ных уравнений, заданных в форме Шеннона 1.

Недостатком этого решения является невозможность использования достаточно точных самоначинающихся методов численного интегрирования, что обуславливает низкое быстродействие, особенно на начальном участке.

Наиболее близким техническим решением к изобретению является устройство, содержащее регистры приращений, первый регистр остатка, выходы которого поцвеаены ко входам первого сумматора, соединенного со входами блока выаелания цифры, второй сумматор, связанный со вхоаами второго блока выделения цифры,

В котором шаг интегрирования выполня. ется за время авух сложений и одного умножения.

Однако это устройство не обладает недостаточным быстродействием.

Целью предлагаемого изобретения является повышение быстродействия.

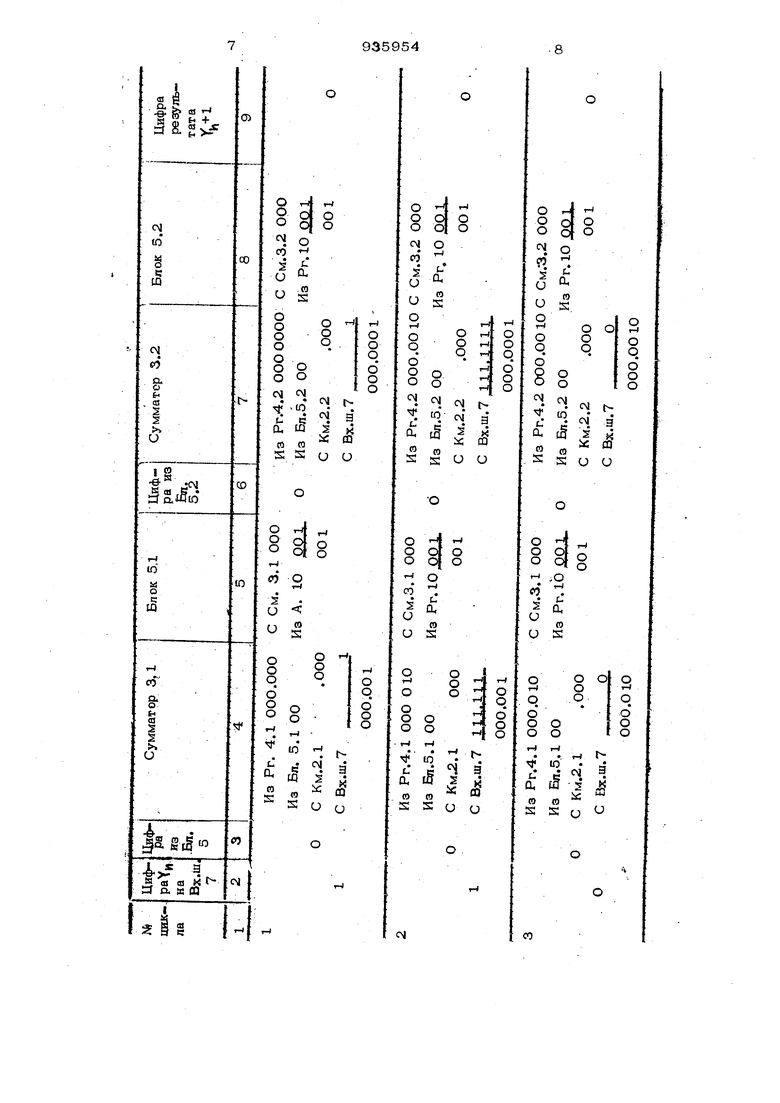

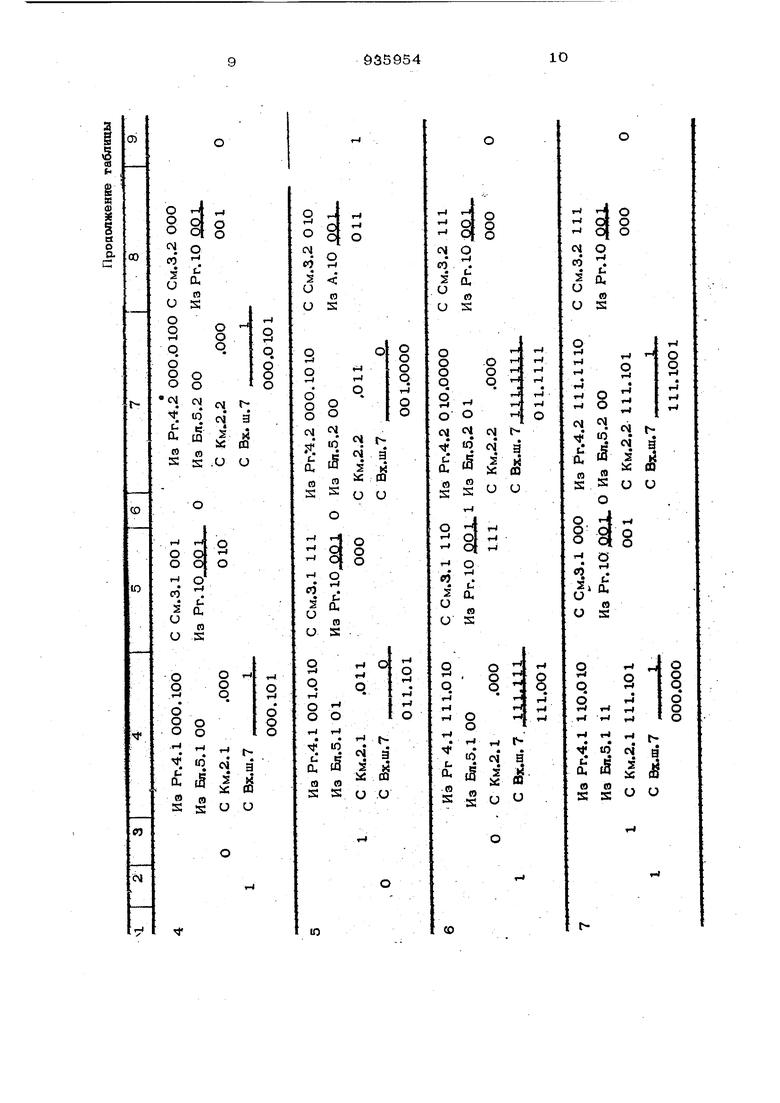

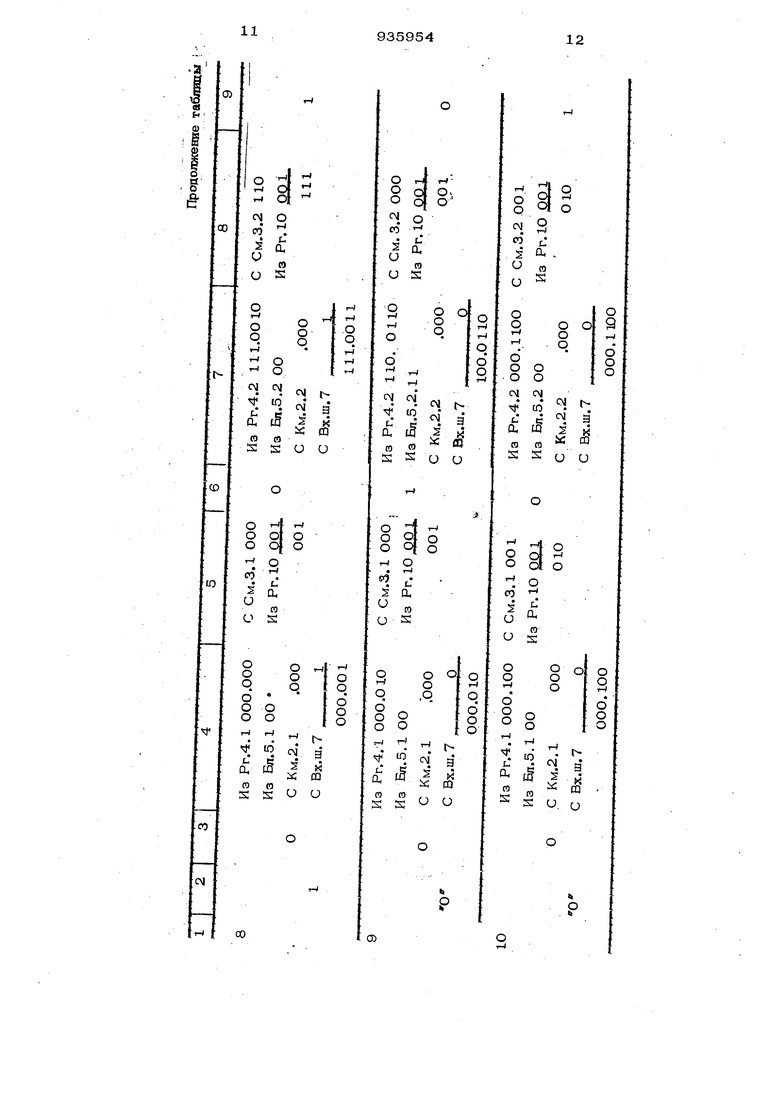

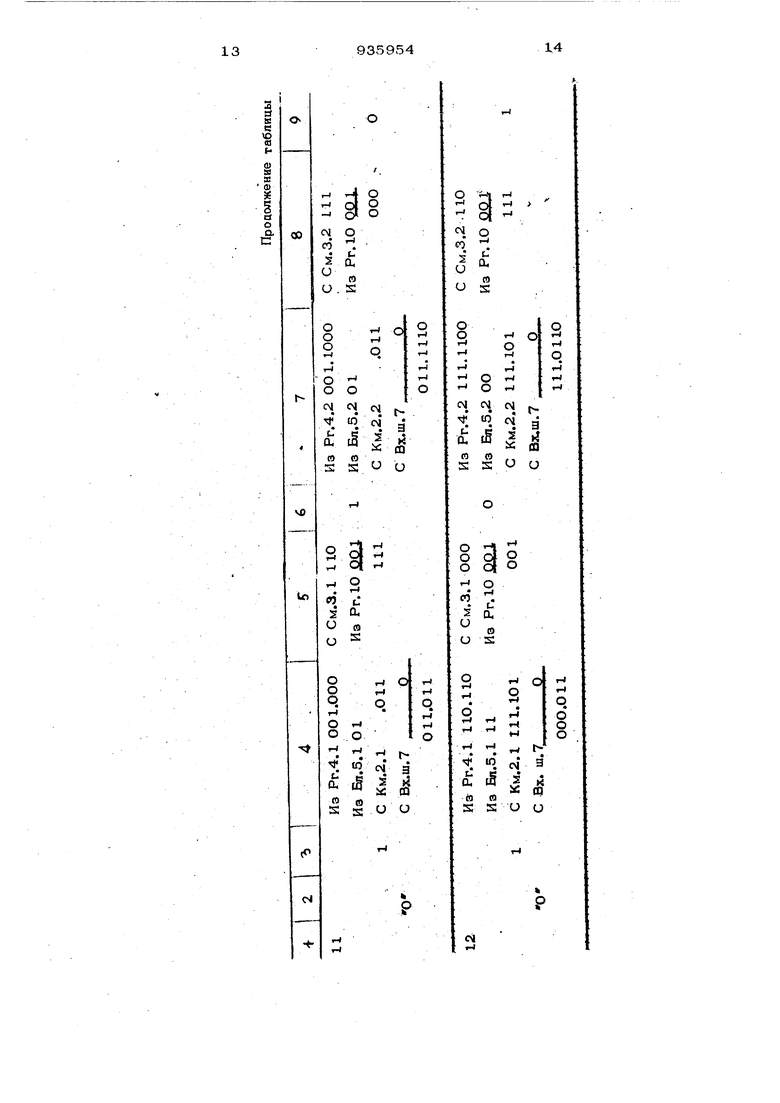

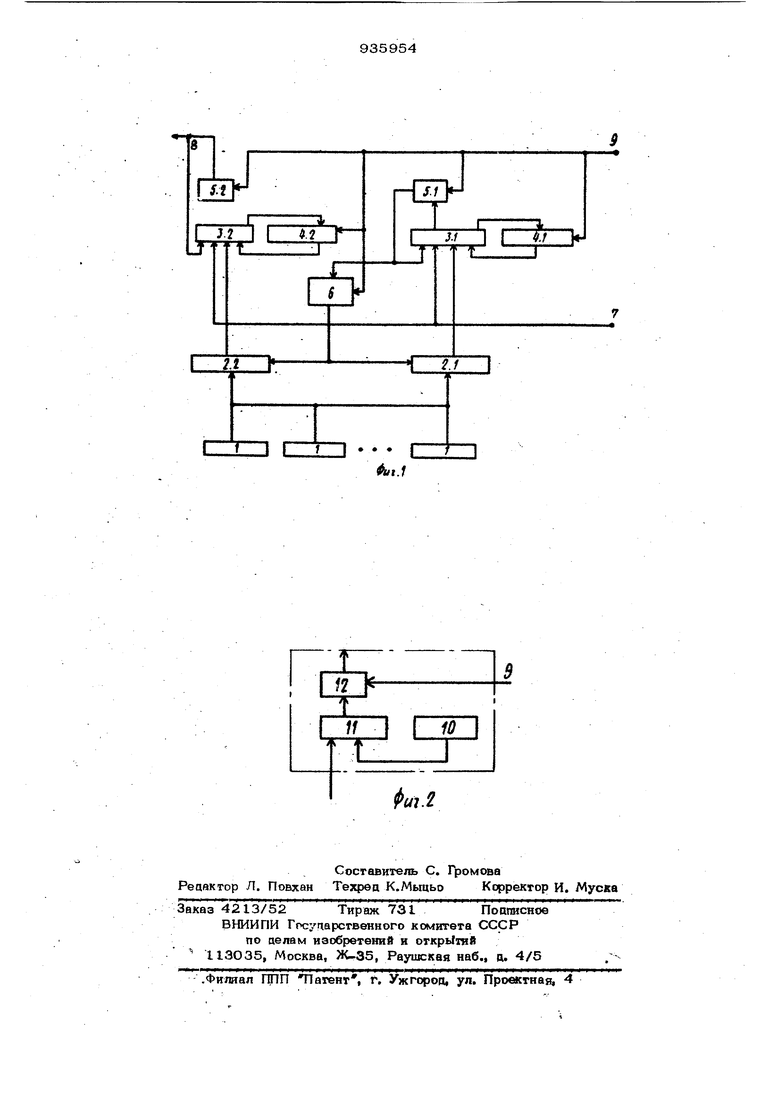

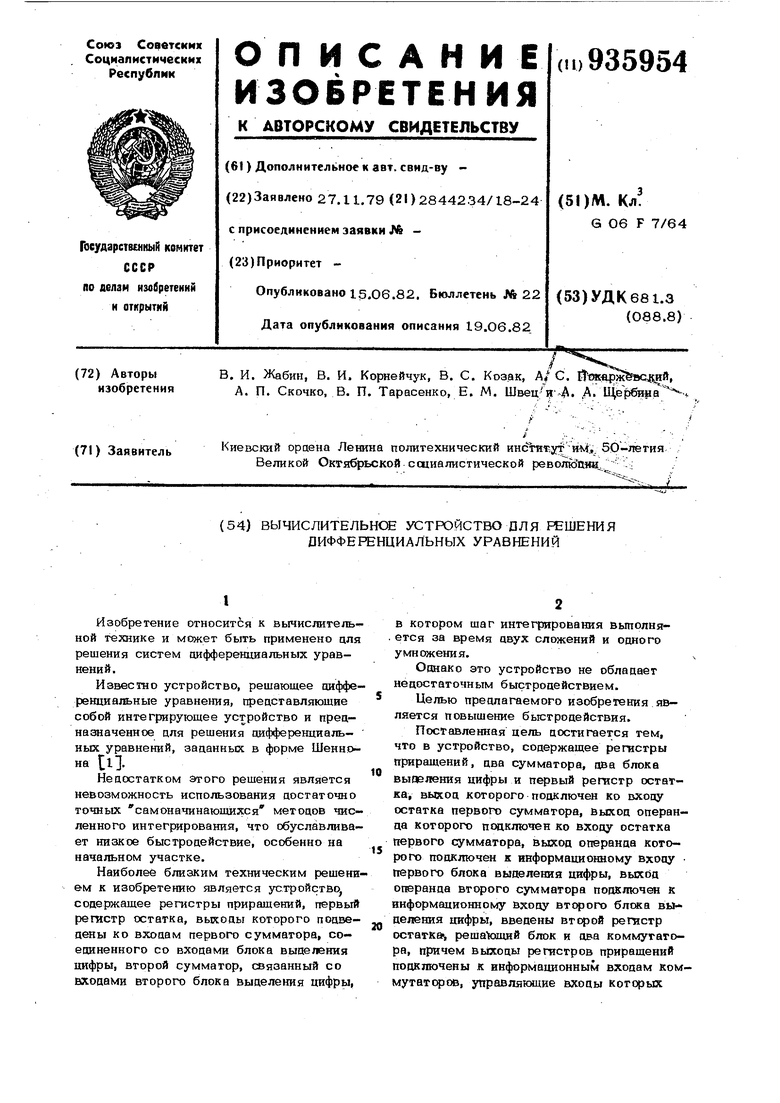

Поставленная цель достигается тем, что в устройство, содержащее регистры приращений, два сумматора, два блока выделения цифры и первый регистр остатка, выход которого подключен ко входу остатка первого сумматора, выход операнда которого подключен ко входу остатка первого сумматора, выход операнда которого подключен к информационному входу первого блока выделения цифры, выход операнда второго сумматора подключен к информационному входу второго блока выцеления цифры, введены втфой регистр остатка, реща1о(щий блок и ова коммутатора, причем выэсоды регистров приращений подключены к информационным входам коммутаторов, управлякщие входы которых соединены с выходом решающего блока, к информационному входу которого подключен выход первого блока выделения цифры, выход первого и Выход второго коммутаторов подключены ко входам приращений первого и второго сумматоров соответственно, вхо ды операндов сумматоров подключены ко входу цифры операнда устройства, выходы первого и второго блока выделения цифры подключены к соответствующим входам пер вого и второго сумматоров соответственно выходы остатка сумматоров подключены к входам соответствующих регистров, к тактирующему ВХОДУ устройства подключены управляющие входы блоков выделения цифры, регистров остатка и решающего блока а выход второго блока выделения цифры подключен к выходу результата устройства, и тем, что блок выделения цифры содержит регистр констант, сумматор и регистр цифры, причем выход регистра цифры соединен с вьссодом блока, управляющий вход - с управляющим вхЬдом блока, S информационный вход - с выходом сумматора, первый , вход которого соединен с выходом регистра констант, а второй вход подключен к информационному входу блока На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока выделения цифры. Устройство содержит регистры (Рр приращений 1, коммутаторы (Кцд) 2,1 и 2,2, сумматоры (С) остатка 3,1 и 3.2, регистры (Рр ) остатка 4,1 и 4.2, блокн (Bf,) выаелення цифры 5.1 и 5.2, решающий блок 6, ВХОД (Вх) 7 цифры операнда и выхоп 8 результата и тактирующий вход (Вх.) 9. Выходы гегистров приращений 1 подключены ко входам коммутаторов 2.1 и 2.2, выходы которых со сдвигом соответственно на S и U разрядов влево соеоинены со входами сум маторов 3,1 и 3.2, т.е. в коммуматоре 2.1 выхоп разряда, имеющего вес 2 , подключен. в сумматоре 3 1 ко входу разряда, нмекмцего вес 2, а в коммутаторе 2,2 вькод разряда с весом 2, поцведен ко входу разряда с весом в сумматоре 3.2. Выходы регистров 4 и блоков 5 со сдвигом на один разряд влево подведены ко входам сумматоров 3, выходы которых соединены со входами регистров 4 и блоков 5. Вход 7 со сдвигом соответственно на у и U разрядов вправо подключен ко входам сумматоров 3.1 и 3.2, где --p-eogpCi-p -H), W- i4eogp(. 5 - выраженная в кош:чесгве циклов задержка появления на выходе блока 6 цифры результата с весом р относительно поступления на сг-о вход цифры аргумента с таким же весом, а /f | - функция округ ления до блин айшего большего целого. Кроме того выходы блока 5.1 подсоединены ко входам блока 6, в котором вычисляется правая часть, связанная.с управляющими входами коммутаторов 2, выходная шина 8 подключена к. выходам блока 5.2, а тактирующая шина 9 связана с управляющими входами регистров 4 и блоков 5 и 6, БЛОКИ выделения цифры 5 содержат регистры константы 10, сумматор 11 и регистр цифры 12, Входы блока 5 и выходы регистра 10 подключены ко входам сумматора 11, выходы которого подведены ко входам регистра цифры 12, управляющий вход и вькоды которого являются управляющим входом и выходами блока 5, В качестве решающего блока может быть использовано любое арифметическое устройство, позволяющее формировать разряды результата последовательно, по мере постутгхйния на его входы соответствующих разрядов операндов, (т.е. устройство, позволяющее сов1С1ещать во времени процессы поразрядного ввода операндов и поразрядной выдачи результата). Устройство реализует неявный метод средней точки., . / Y (, 1) и работает в избыточной Р -ичной системе счисления,, где цифры принимают значения из множества |R,.2,...,Ra5,R2. исходном состоянии (цепи установки исходного состояния не похас-аны) в регистрах приращений 1 записаны коды: R()ti,....R2,()ii|2,...,RifiK; в регистрах константы 10 записаны кодыР йл , а в регистрах 4 и 12 й , а в регистр записаны нули. В каждом I-ом цикле вычисления на входную шину 7 поступает цифра операнХ , имеющая вес , где умколичест о разрядов, после которых фиксируется запятая, и складывается в соответствующих разрядах сумматоров 3 с поступающими также на них кодами с выходов регистров 4, блоков 5 и коммутаторов 2. Причем цифра , поступающая с выхода блока 6 управляет коммутаторами 2 таким образом, что ко входам сумматора 3.1 подключаются выходы регистра I, соцержащего код f: ll/2 a к сумматору 3.2 - penicrp I, соцержащий коц - . . При этом с вызсоца блока 5.2 на выходную шину 8 поступает значение цифры результата имеющей вес Каждый цикл занимается сигналом в тактирующей шине 9, по которому коцы, сформированные на выходе сумматоров 3, заносятся в регастры 4, коды, сформированные на выходе сумматора 11, занос5ггся в регистр 12, а блок 6 подготавливается к приему очередной цифры. Работа устройства на примере интегрирования дифференциального уровня Y -Y для двоичной системы счисления с цифрами I, О, I, при Ч, 11010 fll, иллюстрируется прилагаемой таблицей, где получен результат X Ilfcooof. Предлагаемое устройство позволяет формировать на выходе разряды значения искомой функции в М +1 -ой точке с вь держкой на U+1 циклов относительно ввода в устройство соответствующих разрядов функции в точке. Это позволяет при последовательном соецинении устройств приступить к выполнению очередного шага интегрирования не после окончания предыдущего шага, а непосредственно после получения первых разрядов результате этого шага. Таким образом, пршессы интегрирования на И-ом, И + 1 -ом,гУ1+2 -ом,.., шагах при использовании предлагаемых устройств могут быть совмещены во времени, и время выполнения М шагов составляет:T-KW+O - -O S где У1 - разрядность представления функдни; -fcti - время суммирования, а среднее время выполнения одного шага интегриро вания при достаточно бобьшом количестве шагов М практически не зависит от разрядности функций и стремится к (0+1). (Для примера из это время равно четырем тактам сложения).В известном устройстве процесс интегрирова1гая на данном шаге не может быть ct мещен с процессом интегрирования на последукяиих шагах; а каждый шаг интегрирования выполняется за время двух сложений и одного умножения, т.е. время интегрирования в известном устройстве возрастает с увеличением разрядности и превосходит среднее время выполнения шага в предлагаемом, устройстве. Если учесть, что в известном устройстве (реализующем ффмуду интегрирования первого порядка) для получения той же то шости, что и в предлагаемом (где реализована формула второго порядка) требуется значительно уменьшить величину шага интегрирования, (а при этом во столько же раз увеличивается время вычисления) то вполне очевидно, что цель изобретения с помощью предлагаемого технического реше1гая досстигается. Предлагаемое устройство позволяет не только уменьшать время вычисления (за счет совмещения во емени операций, относящихся как к одному, так и разным щагам интегрирования), но и сохранить обьем вычислений по сравнению с устройствами реалиаукяцими $1вныв методы интегрирования. В предлагаемом устройстве на каждом шаге интегрирования вычисляется только одно значение правой части, тогда как в известном устройстве при реализации метода Рунге-Кутта же порядка на каждом шаге интегрирования правую часть необходимо вычислять два раза.

1593595416

Получаем резульгаг Vu4. ЮОЮЮ 1 входу цифры операицов усгройсгва, выходы

Формула изобретения

1. Вычислительное ycipoftcrBo для ре- 5 венно, выходы остатка сумматоров подклгошенйя Дифференциальных уравнений, содер- чены к входам соответствующих регистжащее регистры приращений, два сумматора, два бл(жа Выделения цифры и первый регистр остатка, вькод которого подключен к входу Ьстатка первого сумматора, . Ёыход операнда которого подключен к информационному входу первого блока выделения 1гаФр1, выход операнда второго сумматора подключен к информационному входу второго блока выделения цифры, о т личающееся тем, что, с целью повышения быстродействия, в него введены решающий блок, два коммутатора и второй регистр остатка вАдеод которого соединен с входом . остатка второго сумматора, причем выходы регистров приращений подключояы к информационным вхрцам коммутаторов, управляющие входы которых соединены с выходом решающего блока, к ин формационному входу которого подключен выХод первого блока выделения цифры, выход первого и вбссод второго коммутатфов подключены к входам гфиращений первого и второго сумматоров соответстбенно, входы операндов сумматоров подключены к

первого и вгорого блоков выделения цифры подключены к соогвегствуюшим вхоцам первого и второго сумматоров соогветст- ров, к такгируюацему входу устройства подключены управляющие входы блоков выявления цифры, регистров остатка и решакацего блока, а выход второго блока выделения цифры подключен к выходу результата устройства. 2. Устройство по п. I, отличающееся тем, что блок выделения цифры содержит регистр констант, сумматор и регистр цифры, причем выход регистра цифры соединен с выходом блока, управляющий вход - с управляющим входом блока, -.а информационный вход - с выходом сумматора, первый входКоторого соединен с выходом регистра констант, а второй вход подключен к информационному входу блока, Источники информации, принятяе во внимание при жспертизе 1.Авгооское свидетельство СССР N 637833, кл. G 06 Jl/02, 1975, 2.Авторское свидетельство СССР / 568060, Кл. G Об J 1/02, 1974 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для вычисления дробнойРАциОНАльНОй фуНКции | 1979 |

|

SU842796A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

Авторы

Даты

1982-06-15—Публикация

1979-11-27—Подача