1

Изобретение относится к области вычислительной техники и может быть применено в цифровых вычислительных машинах и устройствах, построенных на основе больших интегральных схем.

Известны устройства сложения 1, oneрирующие с числами, представленными в позиционной системе счисления. Однако с помощью таких устройств нельзя совмещать во времени процесс поразрядного ввода слагаемых со старших разрядов с процессом формирования цифр результата. Это приводит к увеличению времени получения кода результата при последовательном поступлении очередных разрядов слагаемых, особенно если период их поступления ограничен внещними по. отношению к устройству факторами (например, быстродействием источников информации).

Наиболее близким техническим решением к настоящему является устройство для сложения чисел, содержащее элементы И, выходной регистр, сумматор, выходы младщих разрядов которого подключены ко входам выходного регистра, выходы которого подключены к соответствующим входам сумматора, выходы двух старших разрядов которого соединены с выходными щинами устройства через элементы И, другие входы которых подключены к первой управляющей щине устройства 2. Это устройство позволяет совмещать во времени процессы поразрядного ввода операндов и формирования результата, однако при одновременном сложении нескольких чисе.ч бь стродействие этого устройства 11евслико.

Целью настоящего изобретения является у вел и чей lie быстродействия.

Постав.чениая це.чь достигается тем, что устройство содержит шифраторы, выходы которых подключены к соответствующим входам сумматора, и функциональные регистры, выходы которых подключены ко входам соответствующих ишфраторов, входы функциональных регистров соединены с соответствующими информационными шинами устройства, а управляющие входы функциональных регистроЁз подключены ко второй и третьей уиравляюии М шинам устройства, четвертая уиравляющая шина устройства соединена с управляющим входом выходного регистра, причем функциональные регистры содержат элементы запрета, элементы И, элементы ИЛИ и триггеры, причем j-e информационные входы (j 1, ..., k) функциональных регистров через j-e элементы И nepBOPi группы подключены ко входам установки в еяинице -х триггеров и через элементы запрета - ко входам устагюБКи в нуль j-x триггеров, а вторые входы всех элементов запрета и элементов И первой группы подключены к первому управляющему входу функционального регистра, второй управляющий вход которого подключен к первым входам каждого j-ro элемента И второй группы, выходы которых через j-e элементы ИЛИ подключены к тактирующим входам j-x триггеров и через fj - l)-e элементы ИЛИ - к тактирующим входам (J 1)-х триггеров, единичные выходы которых подключены к информационным входам j-x триггеров, единичные выходы которых соединены с первыми входами j-x элементов И третьей группы, выходы которых являются выходами j-x разрядов функционального регистра, а вторые входы j-x элементов И третьей группы соединены с нулевыми выходами (j - 1)-х триггеров и со вторыми вxoдaми(j - элементов И второй группы.

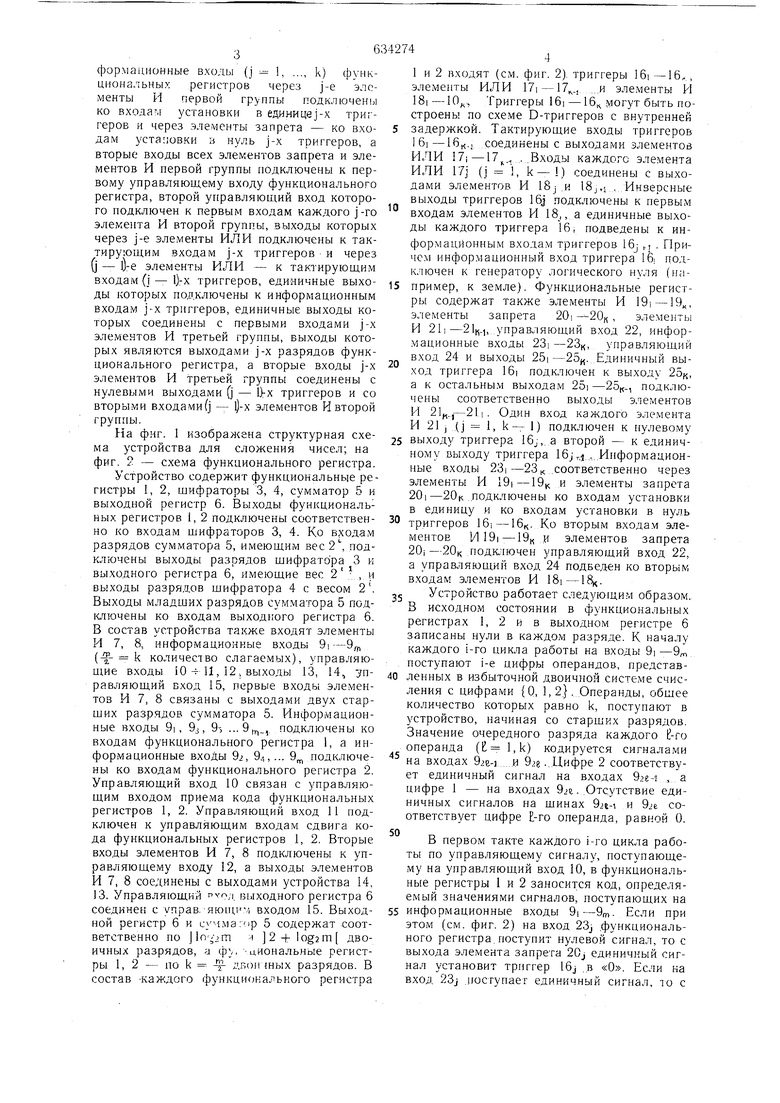

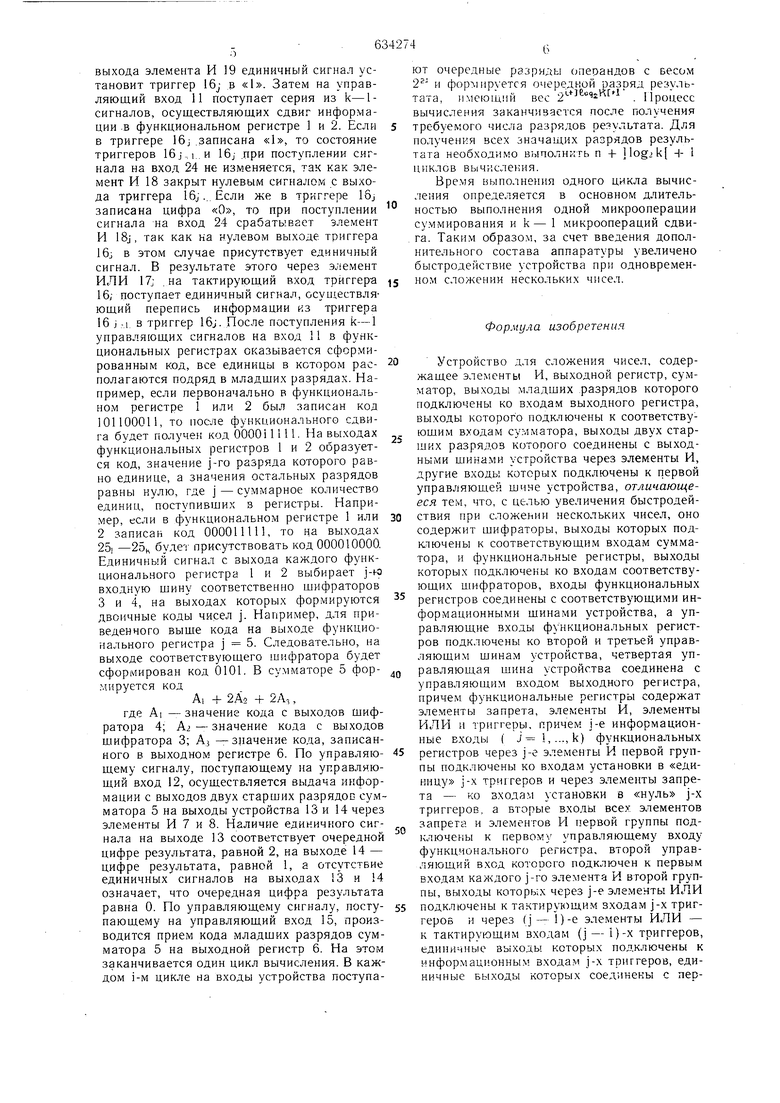

На фиг. 1 изображена структурная схема устройства для сложения чисел; на фиг. 2 - схема функционального регистра.

Устройство содержит функциональные регистры 1, 2, цдифраторы 3, 4, сумматор 5 и выходной регистр 6. Выходы функциональных регистров 1, 2 подключены соответственно ко входам щифраторов 3, 4. Ко входам разрядов сум.матора 5, имеющим вес 2 подключены выходы разрядов шифратора 3 к выходного регистра 6, и.меющие вес 2 ;. , и выходы разрядов шифратора 4 с весом 2. Выходы младших разрядов сумматора 5 подключены ко входам выходного регистра 6. В состав устройства также входят элементы И 7, 8, информационные входы 9i-9 (-f- k количество слагаемых), управляющие входы 10- 11, 12, выходы 13, 14, управляющий вход 15, первые входы элементов И 7, 8 связаны с выходами двух старших разрядов сумматора 5. Информационные входы 9i, 9j, 9, ... 9,,. подключены ко входам функционального регистра 1, а информационные входы 9, 9.1,.., 9 подключены ко входам функционального регистра 2. Управляющий вход 10 связан с управляющим входом приема кода функциональных регистров 1, 2. Управляющий вход 11 подключен к управляющим входам сдвига кода функциональных регистров 1, 2. Вторые входы элементов И 7, 8 подключены к управляющему входу 12, а выходы элементов И 7, 8 соединены с выходами устройства 14, 13. Управляющий выходного регистра 6 соединен с управ, июни- входом 15. Выходной регистр 6 и c}4. 5 содержат соответственно по jloorn - j2+log2m двоичных разрядов, а ф, циональные регистры 1,2 - по k дБон шых разрядов. В состав -каждого фyнкциoнaJ ьнoгo регистра

1 и 2 входят (см. фиг. 2). триггеры 16i -16,,, эле.менты ИЛИ 17i -17,,. ...и элементы И 18| -10д, Триггеры 16 -16 могут быть построены по схеме D-триггеров с внутренней

задержкой. Тактирующие входы триггеров 1 6|-16к.; соединены с выходами элементов ИЛИ 7|-17,, ,.,Входы каждого элемента ИЛИ r7j (j 1, k-) соединены с выходами элементов И 18j .и 18j,i. Инверсные выходы триггеров 16j подключены к первым входам элементов И 18,, а единичные выходы каждого триггера 16, подведены к информационным входам триггеров 16j fj . Приче.м информационный вход триггера 16 подключен к генератору логического нуля (например, к земле). Функциональные регистры содержат также элементы И 19i-19„, элементы запрета 20;--20„ , элементы И 21i-2lf|.,, управляющий вход 22, инфор.мационные входы 23i -23, управляющий вход 24 и выходы 25i-25(,. Единичный выход триггера 16i подключен к выходу 25, а к остальным выходам 25i -25., подключены соответственно выходы элементов И 21.,-21|. Один вход каждого элемента И 21 J .(j 1, k-r 1) подключен к нулевому

5 выходу триггера 16,, а второй - к единичному выходу триггера 16j%.i,.....Информационные входы 23i-23 к .соответственно через элементы И i9i-19 и элементы запрета 20i-20к ..подключены ко входам установки в единицу и ко входам установки в нуль

0 триггеров 16i-16к. Ко вторым входам элементов 1/1 19| -19|, .и элементов запрета 20| -20 нодю1ючен управляющий вход 22, а управляющий вход 24 подведен ко вторым входам элементов И 18i-18.

35 Устройство работает следующи.м образом. В исходном состоянии в функциональных регистрах 1, 2 и в выходном регистре 6 записаны нули в каждом разряде. К началу каждого i-ro цикла работы на входы 9i -9„ поступают i-e цифры операндов, представленных в избыточной двоичной системе счисления с цифрами (О, 1, 2.} ..Операнды, общее количество которых равно k, поступают в устройство, начиная со старших разрядов. Значение очередного разряда каждого Е-го операнда (Е l,k) кодируется сигналами

на входах 9.ге-).и 92g ...Цифре 2 соответствует единичный сигнал на входах 92e-i , а цифре 1 - на входах 9jt. .Отсутствие единичных сигналов на шинах 9.ч-1 и 92и соответствует цифре Е-го операнда, равной 0.

В первом такте каждого i-ro цикла работы по управляющему сигналу, поступающему на управляющий вход 10, в функциональные регистры 1 и 2 заносится код, определяемый значениями сигналов, поступающих на 5 информационные входы 9i-9m. Если при этом (см. фиг. 2) на вход 23j .функционального регистра.поступит нулевой сигнал, то с выхода элемента запрета 20j единичный сигнал установит триггер 16j ..в «О. Если на вход 23j .поступает единичный сигнал, ю с

выхода элемента И 19 единичный сигнал установит триггер 16j в «1. Затем на управляющий вход 11 поступает серия из k-1сигналов, осуществляющих сдвиг информации ,в функциональном регистре 1 и 2. Если в триггере 16j .записана «1, то состояние триггеров 16;,1..и 16j при поступлении сигнала на вход 24 не изменяется, так как элемент И 18 закрыт нулевым сигналом с выхода триггера 16...Если же в триггере loj записана цифра «О, то при поступлении сигнала на вход 24 срабатывает злемент И 18j, так как на нулевом выходе триггера 16j в этом случае присутствует единичный сигнал. В результате этого через элемент ИЛИ 17; .на тактирующий вход триггера 16; поступает единичный сигнал, осуществляющий перепись информации кз триггера 16 j ...1. в триггер 16j. .После поступления k-1 управляющих сигналов на вход 11 в функциональных регистрах оказывается сформированным код, все единицы в котором располагаются подряд в младщих разрядах. Например, если первоначально в функциональном регистре 1 или 2 был записан код 101100011, то после функционального сдвига будет получен код 000011111. На выходах функциональных регистров 1 и 2 образуется код, значение j-ro разряда которого равно единице, а значения остальных разрядов равны нулю, где j - суммарное количество единиц, поступивщих в регистры. Например, если в функциональном регистре 1 или

2записан код 000011111, то на выходах 25| -25к будет присутствовать код 000010000. Единичный сигнал с выхода каждого функционального регистра 1 и 2 выбирает j-ю входную щину соответственно щифраторов

3и 4, на выходах которых формируются двоичные коды чисел j. Например, для приведенного выше кода на выходе функционального регистра j 5. Следовательно, на выходе соответствующего шифратора будет сформирован код 0101. В сумматоре 5 формируется код

AI + 2А-2 + 2А,,

где А| - значение кода с выходов щифратора 4; А - значение кода с выходов щифратора 3; Aj -значение кода, записанного в выходном регистре 6. По управляющему сигналу, поступающему на управляющий вход 12, осуществляется выдача информации с выходов двух старщих разрядов сумматора 5 на выходы устройства 13 и 14 через элементы И 7 и 8. Наличие единичного сигнала на выходе 13 соответствует очередной цифре результата, равной 2, на выходе 14 - цифре результата, равной 1, а отсутствие единичных сигналов на выходах 13 и 4 означает, что очередная цифра результата равна 0. По управляющему сигналу, постунающему на управляющий вход 15, производится прием кода младщих разрядов сум.матора 5 на выходной регистр 6. На этом заканчивается один цикл вычисления. В каждом i-M циКле на входы устройства поступают очередные разряды операндов с весом и формируется очередной разряд результата, имеющий вес . Процесс вычисления заканчивается после получен.ия требуемого числа разрядов результата. Для получения всех значащих разрядов результата необходимо выполнить п -Ь logjk Ч- 1 циклов вычисления.

Время Е ыполнения одного цикла вычисления определяется в основном длительностью выполнения одной микрооперации су.ммирования и k- 1 микроопераций сдвига. Таким образом, за счет введения дополнительного состава аппаратуры увеличено быстродействие устройства при одновременном сложении нескольких чисел.

Формула изобретения

Устройство для сложения чисел, содержащее элементы И, выходной регистр, сумматор, выходы младщих .разрядов которого подключены ко входам выходного регистра, выходы которого подключены к соответствующим входам сумматора, выходы двух старших разрядов которого соединены с выходными щинами устройства через элементы И, другие входы которых подключены к цервой управляющей щине устройства, отличающееся тем, что, с целью увеличения быстродействия при сложении нескольких чисел, оно содержит щифраторы, выходы которых подключены к соответствующим входам сумматора, и функциональные регистры, выходы которых подключены ко входам соответствующих шифраторов, входы функциональных регистров соединены с соответствующими информационными щинами устройства, а управляющие входы функциональных регистров подключены ко второй и третьей управляющим щинам устройства, четвертая управляющая шина устройства соединена с управляющим входом выходного регистра, нричем функциональные регистры содержат элементы запрета, элементы И, элементы ИЛИ и триггерь, причем j-e информационные входы ( J l,...,k) функциональных регистров через j-e элементы И первой группы подключены ко входам установки в «единицу J-X триггеров и через элементы запрета - ко входам установки в «нуль j-x триггеров, а вторые входы всех элементов запрета и элементов И первой группы под1слючены к первому управляющему входу функционального регистра, второй управляющий вход которого подключен к первым входам каждого j-ro элемента И второй группы, выходы которых через j-e элементы ИЛИ подключены к тактирующим входам j-x триггеров и через (j- 1)-е элементы ИЛИ - к тактирующим в.ходам (j - 1)-х триггеров, единичные вьгходы которых подключены к информационны.м входам j-x триггеров, единичные выходы которых соединены с первыми входами j-x элементов И третьей группы, выходы которых являются выходами j-x разрядов функционального регистра, а вторые входы j-x элементов И третьей группы соединены с нулевыми выходами (j -1)-х триггеров и со вторыми входами (j -1)-х элементов И второй группы.

Источники информации, принятые во внимание при экспертизе;

1.Карцев М. А. «Арифметика цифровых машин, М., «Наука, 1969, с. 294, рис. 3-1.

2.Заявка № 2104692/24, кл. G 06 F 7/385, 1975, по которой принято положительное решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для алгебраического сложения чисел | 1976 |

|

SU638959A1 |

| Устройство для вычисления многочленов вида @ @ | 1978 |

|

SU868767A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для возведения в квадрат двоичных чисел | 1976 |

|

SU602941A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

Авторы

Даты

1978-11-25—Публикация

1976-03-18—Подача