- .

Изобретение относится к вычислительной технике и Может быть применено в арифметических устройствах цифровых вьгчислительных машии, особенно в случаях повышения требований по быстродействию.

Известно устройство, состоящее из сдвиговых регистров множимого и мно)Ю1теля и сумматора,, в которых бпераиия умножения реализуется путем сдвига регистров множимого и множителя и многократных сложений в сумматоре множимого, сдвинутого на определенное число разрядов, определяемое положением единиц в разрядах множителя, с частными произведениями, храиящимися в сумматоре 1 .

Недостатком этого устройства является низкое быстродействие.

Наиболее близкое к предлагаемому изобретению устройстве содержит сумматор, регистр множителя, регистр множимого, блок умножения множимого на три, блок управления, входы которого соединены с выходами пяти младших разрядов регистра множителя, блок выдачи в сумматормножимого в прямом коде без сдвига блок выдачи в сумматор множимого в прямом

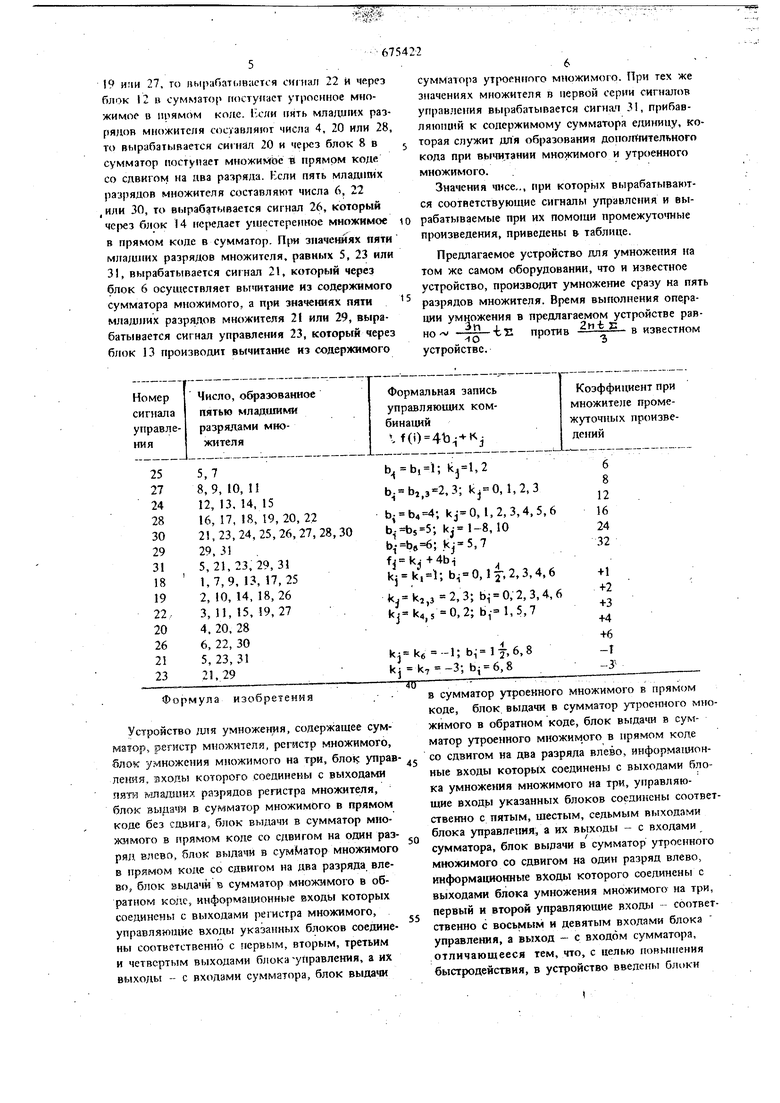

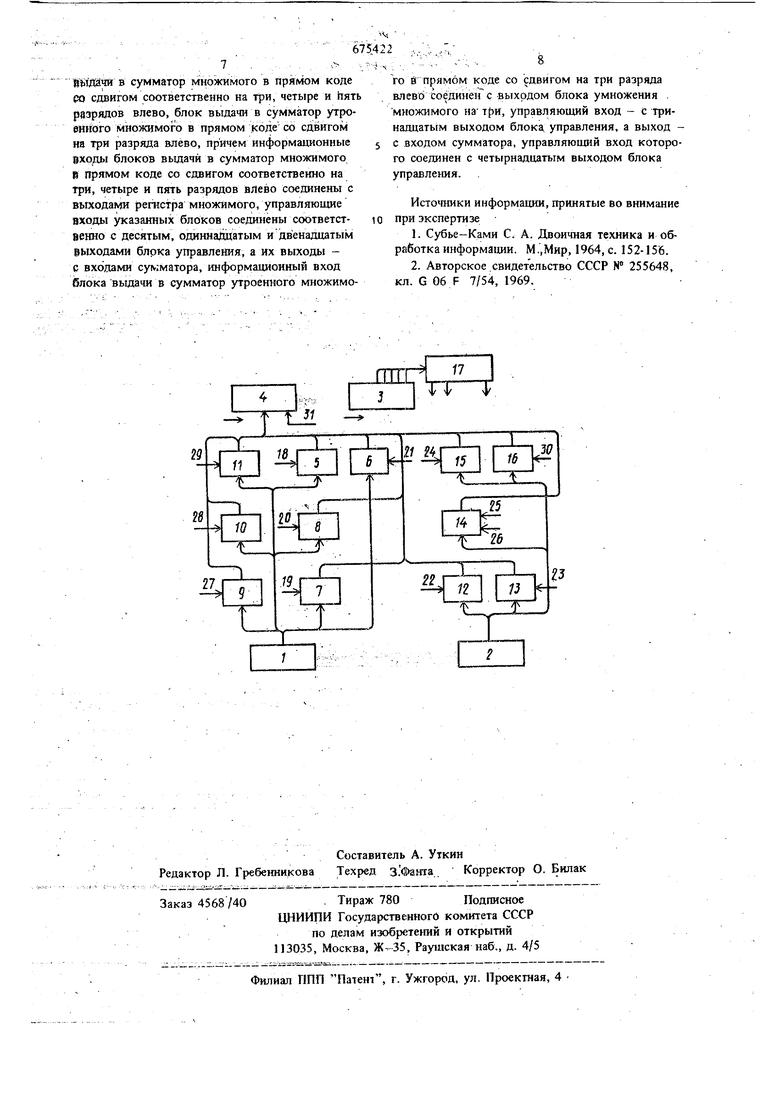

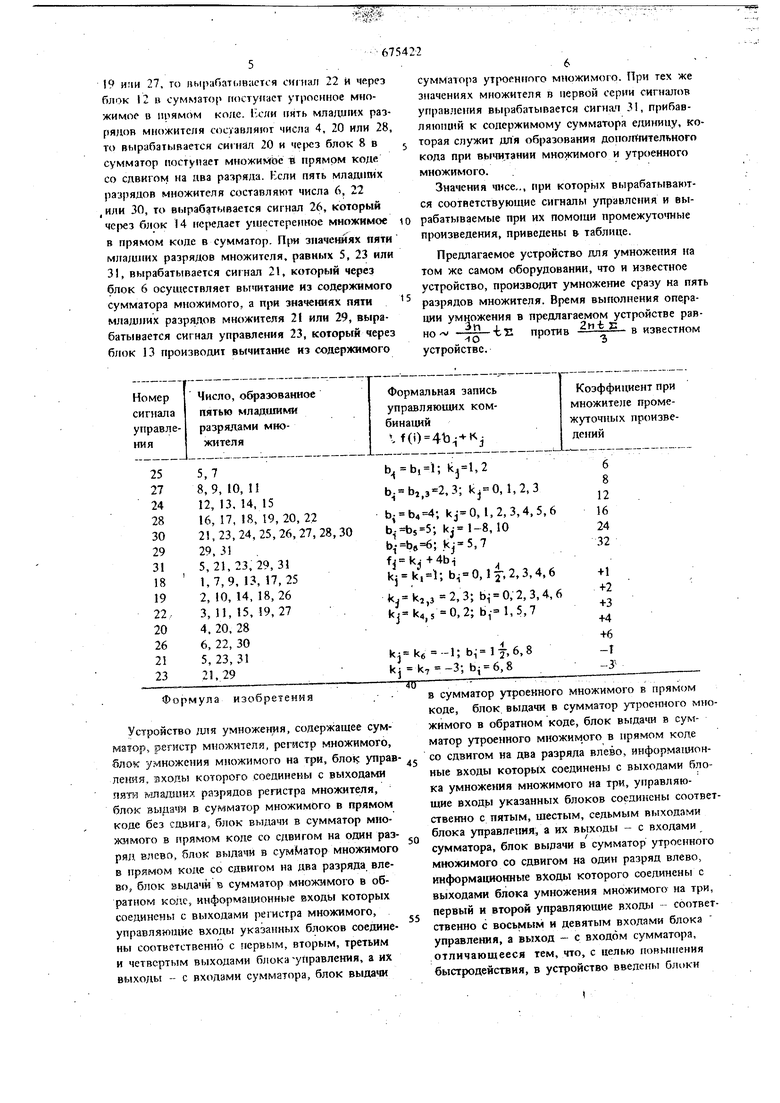

коде со .сдвигом на один разряд влево, блок выдачи в сумматор множимого в прямом коде со сдвигом на два разряда, влево, блок выдачи в сумматор множимого в обратном коде, информационные входы которых соединены с выходами решстра множимого, управляющие входы указанных блоков соединены соответственно с первым, вторым, третьим и четвертым выхода- . ми блока управления, а их выходы - с входами сумматора блок выдачи в сумматор утроенного множимого в прямом коде, блок выдачи в сумматор утроенного множимого в обратном коде, блок выдачи в сумматор утроенного мно-. жимого в прямом коде со сдвигом на два разряда влево, информационные входы которых соединены с выходами блока умножения множимого на три, управляющие входы указанных блоков соединены соответственно с пятым, шестым, седьмым выходами блока управления, а их выходы - с входами сумматора, блок выдачи в сумматор утроенного множимого со сдвигом на один разряд влево, информационные входы которого соединены с выходами блока умножения множимого на три, первый и второй управляющие входы -- соответствегпю с посьмым и девятым входами блока управления, а вы.ходсо входом сумматора 2. Недостатком такого устройства является нилкое быстродействие. Цель изобретения - повышение быстродействия. Для этого в устройство введены блоки выдачи в сумматор множимого в прямом коде со сдвигом соответственно на три, четыре и пять разрядов влево, блок выдачи в сумматор утроен ного множимого в прямом коде со сдвигом на три разряда влево, причем информационные входы блоков выдачи в сумматор множимого в прямом коде с6 сдвйг6мс 6от:вётствённо На три, четыре и пять разрядов влево соединены с выходами регистра множимого, управляющие входь указанных блоков соединены соответственно с десятым, одиннадцатым и двенадцатым выходами блока управления, а их выходы - с входами сумматора, информационный вход блока выдачи в сумматор утроенного множимого в прямом коде со сдвигом на три разряда влево соедлнен с выходом блока умножения множимого на три, управляющий вход - с тринадцатым выходом блока управления, а выход - с входом сумматора, управляющий вход которо го соединен с четырнадцатым выходом блока управления. . . На чертеже дана блок-схема предлагаемого устройства для умножения. Устройство содержит регистр 1 множимого, блок 2 умноже шя множимого на три, регистр 3 множителя, сумматор 4, блок 5 выдачи в сум матор множимого в прямом коде, блок 6 выдг чи в сумматор множимого в обратном коде, блок 7 выдачи в множимого в прямом коде со сдвигом на один разряд влево, блок 8 выдачи в сумматор множимого в прямом коде со сдвигом на дьа разряда влево,бло 9-11 вбщачи в сумматор множимого в прямом коде со сдвигом соответственно на три, четыре, п:ять разрядов влево, блок 12 выдачи в сумматор утроенного множимого в прямом коде, блок 13 выдачи в сумматор утроенного множимого в обратном коде, блок 4 выдачи в сумматор утроенного множимого в прямом коде со сдвигом на один разряд влево, блок 15 выдачи в сумматор утроенного множимого в прямом коде со сдвигом на два разряда влево, блок 16 выдачи в сумматор утроенного множимого в прямом коде со сдвигом на три разряда влево, блок 17 управления, выходы 18-31 блока управления. Устройство функционирует следующим образом. В соответствии со значениями младншх разрядов множителя блок 17 управления выра 6а1Ш ШррГ й сигнгиШГ Ф К1В1ия, если число, записанное и пяти мл:щп1их разрядах регистра 3 множителя, равно 5 или 7 (п двоичном коде (Ю101 и 00111), то вырабатывается сигнал 25. осуществляющий выдачу в сумматор множимого, умноженного на 6 в прямом коде с блока 14. Если на вход блока 17 управления подано числа 8, 9, 10 или П, то вырабатывается сигнал 27 и через блок 9 на вход сумматора 4 поступает сдвинутое на три разряда множимое в прямом коде (т.е. множимое умноженное на число 8). Ксли пять младших разрядов множителя составляют числа 12, 13, 14 или 15,то вырабатывается сигнал управления 24 и через блок 15 в сумматор подается множимое в прямом коде, умноженное на 12. Если пять младщих разрядов регистра 3 множителя составляют числа 16, 17, 18, 19, 20, то управляющий сигнал 28 через блок 10 подает в сумматор множимое в прямом коде, умноженное на число 16.Если пять малдщих разрядов Множителя составляют числа 21, 23, 24, 25, 26, 27, 28 или 30, то вырабатывается сигнал управления 30 и через блок 16 в сумматор выдается мно}кимое в прямом коде, умноженное на 24. Если пять младщих разрядов множителя составляют числа 29 или 31, то вырабатывается сигнал управления 29. и через блок И в суМматор поступает промежуточное произведение, равное множимому в прямом коде, умноженному на 32. Если число, образующееся пятью младшими разрядами множителя, равно 5, 21, 23, 29 или 31, то вырабатывается управляющий сигнал 31, поступающий на вход младшего разряда сумматора и записывающий в него единицу: так как любое из записываемых, в сумматор чисел 6 первую серию сигналов управления имеет в младшем разряде ноль, поскольку все они передаются в него со сдвигом влево, прибавление этой еданицы производится без потери времени, по сигналу 31 в сумматор записывается промежуточное произведение плюс единица, в младший разряд обрабатываемых пяти разрядов сумматора. Если пять младщих разрядов множимого равны нулю, то происходит сдвиг сумматора на пять разрядов вправо. Вторая серия управляюишх. сигналов вырабатывается блоком 17 с задержкой относительно первой на время суммирования содержимого сумматора с первым промежуточным произведением. Если число, записанное в пяти младишх разрядах множителя, равно 1, 7, 9, 13, 17 или 25, то вырабатывается сигнал 18, передающий через блок 5 в суммачор мкожиМое в прямом коде без сдвига. Если пять младших разрядов множителя составляют числа 2, 10, 14, 18, 26, то вырабатывается управляющий сигнал 19 и через блок 7 в сумматор вводится удвоенное множимое в прямом коде. Если пять младишх разрядов множителя составляют числа 3, 11, 15, 9 и;1И 27, то )атывастся сигнал 22 и через блок I 2 в суммато( поступает утроенное множимое в ПРЯМОМ коде. пять младитх разрялов множителя составляют числа 4, 20 или 28, то вырабатывается сигнал 20 и блок 8 в сумматор поступает множимое в прямом коде со сдвигом на два разряда. Ксли пять мла1и1тх разрядов множителя составляют числа 6, 22 , или 30, то вырабатывается сигнал 26, который че()ез блок 14 передает ушестеренное множимое в прямом коде в сумматор. При значениях пяти мла/щ1их разрядов множителя, равных 5, 23 или 31, вырабатьшается сигнал 21, который через блок 6 осуществляет вычитание из содержимого сумматора множимого, а при значениях пяти младших разрядов множителя 21 или 29, вырасумматора утроенного множимого. При тех же значениях множителя в первой серии сигналов управления вырабатывается сигн;ш 31, прибавЛЯЮ11ШЙ к содержимому сумматора единицу, которая служит для образования допотгйительного кода при вычитании множимого и утроенного множимого. Значения wee.., при которых вырабатываются соответствующие сигналы управления и вырабатываемые при их помощи промежуточные произведения, приведены в таблице. Предлагаемое устройство для умножения на том же самом оборудовании, что и известное устройство, производит умножете сразу на пять разрядов множителя. Время выполнения опе:ра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на п-разрядов множителя | 1977 |

|

SU717764A1 |

| Устройство для умножения | 1977 |

|

SU662940A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ | 1969 |

|

SU255648A1 |

| Устройство для умножения на -разрядов множителя | 1977 |

|

SU750487A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения | 1985 |

|

SU1290301A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

Устройство ;щя умножения, содержащее сумматор., регистр множителя, регистр множимого, блок умножетгия множимого на три, управ пения, входы которого .соединены с выходами пяти ivuiajiiUHx разрядов регистра множителя, блок выдачи в сумматор множимого в прямом коде без сдвига, блок выдачи в сумматор множимого в прямом коде со сдвигом на один разряд влево, блок выдачи в сум1Матор множимого в прямом коде со сдвигом на два разряда влево, блок вьшачй в сумматор множимого в обратном коде, информационные входы которых соединены с выходами регистра множимого, управляющие входы указанных блоков соединены соответственно с первым, вторым, третьим и четвертым выходами блока -управления, а их выходы - с входами сумматора, блок выдачи коде, блок выдачи в сумматор утроенного множимого в обратном коде, блок выдачи в сумматор утроенного множимого в прямом коде со сдвигом на два разряда влево, информационные входы которых соединены с выходами бло ка умножения множимого на три, управляющие входы указанных блоков соединены соответственно с пятым, шестым, седьмым выходами блока управления, а их выходы - с входами сумматора, блок выдачи в сумматор утроенного множимого со сдвигом на один разряд влево, информационные входы которого соединены с выходами блока умножения множимого на три, первый и второй управляющие входы - соответственно с восьмым и девятым входами блока управления, а выход - с входом сумматора, отличающееся тем, что, с целью повыигения быстродействия, в устройство введены блоки

8Ь1Дачй в сумматор множимого в прялюм коде ео сдвигом соответственно на три, четыре и Ьять разрядов влево, блок выдачи в сумматор утроенного множимого в прямом коде со сдвигом на три разряда влево, причем информационные входы блоков вьщачй в сумматор множимого В прямом коде со сдвигом соответственно на три, четыре и пять разрядов влево соединены с выходами penictpa множимого, управляющие входы указанных блоков соединены соответственно с десятым, одиннадцатым и двенадцатым выходами блока управления, а их выходы с входами сумматора, информационный вход блока вьщачй в сумматор утроенного множимоVo и прямом коде со сдвигом на три разряда влево соединен с выходом блока умножения . множимого нз три, управляющий вход - с тринадцатым выходом блока управления, а выход с входом сумматора, управляющий вход которого соединен с четырнадцатым выходом блока управления.

Источники информации, принятые во вннмание при экспертизе

Авторы

Даты

1979-07-25—Публикация

1977-04-01—Подача