1

Изобретение относится к вычислительной технике и может использоваться при создании последовательных цифровых вычислительных машин, Б частности электронных клавишных вычислительных машин (ЭКВМ), выполняющих вычисление элементарных функций аппаратными средствами.

Представление информации может быть как двоичным, так и двоично-десятичным.

Известны устройства для вычисления элементарных функций 1, 2.

Указанные устройства содержат сумматор, блок управления и по два блока для сдвига аргументов на произвольное число разрядов, что требует значительных аппаратурных затрат. Кроме того, они способны реализовать процесс умножения, начиная только со старших разрядов множителя, это понижает точность вычисления результата.

Из известных устройств для вычисления элементарных функций наиболее близким но технической сущности к изобретению является устройство 3, содержащее элементы И, НЕ, регистры данных, первые входы которых соединены с информационным входом устройства, выход первого регистра данных подключен к первому входу первого сумматора, второй вход которого через первый коммутатор связан с выходом второго регистра данных, второй, третий и четвертый входы третьего регистра данных соединены соответственно с первым, вторым н третьим выходами блока управления, нервый управляющий вход нервого коммутатора - с третьим выходом блока унравления, четвертый выход которого нодключен к входу счетчика сдвигов модификатора, выходом подсоединенного к входу дешифратора. Кроме того, устройство содержит регистр синхронизации, вход которого НОДКЛИчен к управляющему входу устройства и к первому входу блока управления.

Это устройство имеет такие недостатки, как сложность и низкое быстродействие.

Сложность устройства онределяется исиользованнем дополнительного регистра модификатора, который нрн большой разрядности регистров данных является весьма громоздким.

Кроме того, в рассматриваемое устройство введены унравляюшие цепи для сдвига регистра модификатора на произвольное чнсло разрядов. Реализация этих цепей требует больших аппаратурных затрат.

В известном устройстве реализована схема деления с восстановлением остатка, это объясняется тем, что знак остатка определяется по наличию переноса из старшего разряда. Такая структура не позволяет параллельно производить обработку делимого (частичного нроизведения) и модификацию делителя (множимого), что в совокупности с необходимостью сдвига регистра модификатора вызывает увеличение времени вычисления функции.

Прямая реализация такого устройства для случая носледовательных машин приведет к существенному понижению быстродействия и излишним затратам оборудования.

Цель изобретения - упрощение устройства и повышение его быстродействия.

Это достигается тем, что известное устройство дополнительно содержит блок модификатора, входы которого соединены с выходами разрядов второго регистра данных, дешифратора, регистра синхронизации, с пятым выходом блока управления и выходом первого элемента НЕ, вход которого подключен к пятому выходу блока управления, второй сумматор, первый вход которого соединен с выходом второго регистра данных, второй вход - с выходом второго коммутатора, первый информационный вход которого связан с выходом первого регистра данных, а второй информационный вход - с выходом блока модификатора и с информационным входом первого коммутатора. Первый управляющий вход второго коммутатора соединен с третьим выходом блока управления, второй управляющий вход - с выходом первого элемента И, пер вый вход которого связан с выходом первого элемента НЕ, а второй вход - с шестым выходом блока управления и первым входом второго элемента И, вторым входом подключенного к пятому выходу блока управления, а выходом - к первым входам третьего и четвертого элементов И и входу второго элемента НЕ, выход которого соединен с первыми входами пятого и щестого элементов И. Вторые входы третьего и пятого элементов И соединены с седьмым выходом блока управления и входом третьего элемента НЕ, выход которого подключен к вторым входам четвертого и шестого элементов И, а выход третьего элемента И - к второму управляющему входу первого коммутатора и к третьему управляющему входу второго коммутатора. Выход четвертого элемента И подключен к третьему управляющему входу первого коммутатора и к четвертому управляющему входу второго коммутатора, выход пятого элемента И - к четвертому управляющему входу первого коммутатора, пятый управляющий вход которого соединен с выходом щестого элемента И. Кроме того, в устройство введен блок сравнения, первый вход которого соединен с выходом первого сумматора и вторым входом первого регистра данных, а второй вход - с выходом второго сумматора и вторым входом второго регистра данных, третий вход - с пятым выходом блока управления, второй вход которого связан с выходом блока сравнения. Нервые входы первого и второго входных элементов И первого и второго регистров данных соединены с первым и вторым выходами блока управления соответственно, вторые входы первого и второго входных элементов И первого регистра данных - с выходом первого элемента НЕ,

а вторые входы первого и второго входных элементов И второго регистра данных - с пятым выходом блока управления. Первые входы третьих входных элементов И первого и второго регистров данных подключены к выходам второго и первого регистра данных соответственно, а вторые входы - к восьмому выходу блока управления.

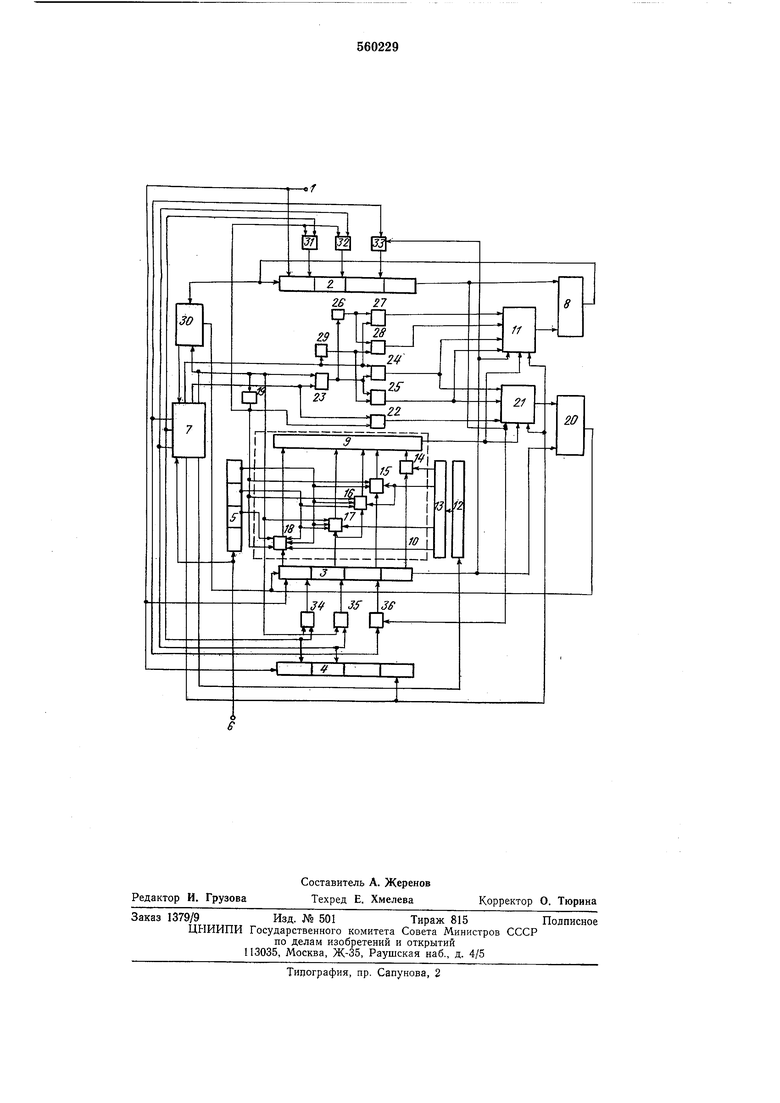

Схема предлагаемого устройства представлена на чертеже, где 1 - вход устройства для записи информации в регистры данных; 2, 3, 4 - регистры данных; 5 - регистр синхронизации; 6 - вход устройства для внешнего синхронизирующего сигнала; 7 - блок управления; 8 - одноразрядный сумматор; 9 - элемент ИЛИ; 10 - блок модификатора; И - коммутатор; 12 - счетчик сдвигов модификатора; 13 - дешифратор; 14-18 - элементы И блока модификатора; 19 - элемент НЕ; 20 - одноразрядный сумматор; 21 - коммутатор; 22-25 - элементы И; 26 - элемент НЕ; 27, 28 - элементы И; 29 - элемент НЕ; 30 - блок сравнения; 31, 32, 33 - входные элементы И регистра 2 данных; 34, 35, 36 - входные элементы И регистра 3 данных.

Устройство может работать в шести режимах: вычисление функций пх, ё, arctgx, tgx, умножение, деление.

Работает устройство следуюшим образом.

Аргумент вычисляемой функции задается отношением двух чисел, записываемых по входу 1 в первый 2 и во второй 3 регистры данных. При этом делимое всегда записывается в регистр 2, а делитель - в регистр 3. Регистры данных являются динамическими сдвиговыми регистрами, информация в которых непрерывно циркулирует. Для определения положения информация в регистрах данных служит регистр 5 синхронизации, в котором циклически сдвигается единица. Номер разряда регистра синхронизации, в котором находится единица, соответствует номеру разряда числа в первом (младшем) разряде регистра данных. Запуск регистра синхронизации осуществляется с помощью сигнала, поступающего по входу 6.

Для обеспечения режима модификации используется блок 10 модификатора, на выходе элемента ИЛИ 9 которого вырабатывается информация, сдвинутая вправо на определенное количество разрядов относительно информации, содержащейся в регистре 3 данных.

Величина сдвига зависит от состояния счетчика 12 сдвигов модификатора и от вида сигнала, поступающего с пятого выхода блока 7. Перед началом вычислений состояние счетчика 12 равно «О. Сдвиг осуществляется при помощи совокупности элементов И, количест. „ In - 1 , во которых равно () п - количество разрядов регистров данных).

В качестве примера на чертеже представлена схема для четырех разрядов. В этом случае используются элементы И 14-18. Элемент И 14 соединен с выходом младшего разряда регистра 3 данных. Если содержимое

счетчика 12 сдвигов модификатора равно «О, то на выходе дешифратора 13, соединенном с вторым входом элемента И 14, присутствует сигнал «ЛОГ 1, и информация из регистра 3 данных без изменений нроходит через элемент И 14. Элемент И 15 связан с выходом второго разряда регистра 3 данных. Если содержимое счетчика 12 равно «1, то на выходе дешифратора 13, соединенном с вторым входом элемента И 15, присутствует сигнал «ЛОГ 1. На входе элемента И 15, подключенном к выходу элемента НЕ 19, появляется сигнал «ЛОГ 1 в случае, когда значение сигнала, поступаюшего с пятого выхода блока 7, равно «ЛОГ О. Четвертый вход элемента И 15 соединен с инверсным выходом старшего разряда регистра 5 синхронизации, что обеспечивает обнуление информации на выходе элемента И 15 после прохождения через него сдвинутой вправо на один разряд инфопмапии, содержащийся в регистре 3 данных. Элементы И 16, 18 работают аналогичным образом при последующих состояниях счетчика 12. Элемент И 17 работает только при наличии «ЛОГ 1 на пятом выходе блока 7, что соответствует вычислению функций . . Информация, сформированная элементами И 14-18 через элемент ИЛИ 9 подается на соответствующие входы первого 11 и ВТОРОГО 21 коммутаторов, первого 8 и второго 20 сумматоров. Информания с сумматоров 8, 20 проходит на входы блока 30 сравнения, на другой вход которого поступает сигнал с пятого выхода блока 7. При нулевом значении сигнала происходит «прямое сравнение, т. е. сигнал на выходе блока 30 сравнения Равен «ЛОГ I, если число, находящееся в регистпе 2 данных, больше или равно ЧИСЛУ в пегистре 3 данных. ПРИ наличии сигнала «ЛОГ 1 на пятом выходе блока 7 происходит «обратное сравнение, т. е. сигна.л на выходе блока 30 сравнения равен «ЛОГ 1, если число, находящееся в регистре 3, больще или равно ЧИСЛУ в регистре 2. Этот режим используется при вычислении arete л-.

При вычислении функции пх для обеспечения режима псевдоделения на пятом, шестом и седьмом выходах блока 7 устанавливается код 011 соответственно. На выходах элементов И 22, 27 появляется сигнал «ЛОГ 1. Это обеспечивает поступление инверсной информации из регистра 3 через коммутатор 11 на второй вход сумматора 8.

На первый вход сумматора 8 попадает информация из регистра 2, сигнал «ЛОГ 1 с выхода элемента И 22 - на второй вход коммутатора 21, что обеспечивает поступление информации с элемента ИЛИ 9 на второй вход сумматора 20. Наличие сигнала «ЛОГ 1 на выходе блока 30 сравнения обеспечивает выдачу сигнала по третьему выходу блока 7, поступающего на управляющие входы коммутаторов И и 21 и на вход младшего разряда третьего регистра 4 данных. Этим достигается получение остатка на выходе сумматора 8, модифицированного делителя на выходе сумм тора 20 и прибавление единицы к младшему разряду регистра 4. Информация с выходов сумматоров 8, 20 поступает в регистры 2 и 3 соответственно.

Описанный процесс продолжается до тех пор, пока сигнал на выходе блока 30 сравнения не примет значение «ЛОГ О. Это соответствует окончанию вычисления очередной цифры псевдочастного в регистре 4. После

этого по первому выходу из блока 7 выдается сигнал «Сдвиг влево, поступаюший на входы элементов И 31, 34 и на вход регистра 4 данных. На вход элемента И 34 по пятому выходу блока 7 приходит сигнал «ЛОГ О, а на

элемент И 31 через элемент НЕ 19 сигнал «ЛОГ 1. Это обеспечивает сдвиг информации на один разряд влево в регистрах 2 и 4. Одновременно к счетчику 12 с помощью сигнала, выдаваемого по четвертому выходу блока 7, прибавляется «I. Далее вычисляется следующая цифра псевдочастного. Процесс продолжается до полного заполнения третьего регистра данных. По окончании процесса псевдоделения в регистре 4 находится псевдочастное.

Далее выполняется процесс умножения констант вида 10J-1n(l+ 10--) на полученное псевдочастное (/ - число, содержап-1ееся в

счетчике 12). Константы записываются в регистр 3 по входу 1. Для обеспечения режима умножения на пятом, шестом и седьмом выходах блока 7 устанавливается код 000 соответствентто, а регистр 2 обнуляется. На выходе

элемента И 23 появляется сигнал «ЛОГ О, а на выходе элемента И 28 - сигнал «ЛОГ 1. В результате информация поступает из регистра 3 через коммутатор 11 на второй вход сумматора 8. По третьему выходу блока 7 выдается сигнал, поступаюший на первые управляющие входы коммутаторов 11 и 21 и на вход младшего разряда регистра 4. Это обеспечивает получение частичного произведения на выходе сул1матора 8 и вычитание единицы

от младшего разряда регистра 4. Информация в регистре 3 не меняется при умножении на одну цифру множителя. Умножение на одну цифру множителя заканчивается после обнуления младшего разряда регистра 4. После

этого из б,тока 7 по второму выходу подается сигнал «Сдвиг вправо, поступаюший на входы элементов И 32, 35 и на вход регистра 4. На вход элемента И 35 по пятому выходу блока 7 приходит сигнал «ЛОГ О, а на элемент

И 32 через элемент НЕ 19 - сигнал «ЛОГ 1. Происходит сдвиг информации, находящейся в регистрах 2 и 4, на один разряд вправо. Одновременно от содержимого счетчика 12 с помощью сигнала, выдаваемого по четвертому выходу блока 7, вычитается единица. Затем по входу 1 в регистр 3 записывается новая константа и она умножается на следующую цифру множителя. Процесс продолжается до полного обнуления регистра 4. Результат умножения находится в регистре 2.

Вычисление функции е происходит аналогично вычислению функции 1п л; с той разницей, что вначале производится деление аргумента на константы вида 10 1п(1 + 10), а затем псевдоумноженне модификацией множимого. При делении на константу на пятом, шестом и седьмом выходах блока 7 устанавливается код 001 соответственно. При этом на выходе элемента PI 27 оказывается сигнал «ЛОГ 1, а на выходе элемента И 22 - сигнал «ЛОГ О. Далее выполняется процесс делення аналогично описанному, только без модификации делителя. После определения очередной цифры частного в регистр 3 данных по входу 1 записывается соответствующее новое значение константы.

Перед началом нсевдоумножения множимое по входу 1 зап сывается в регистр 3, а регистр 2 обнуляется. Для выполнения псевдоумноження на пятом, шестом и седьмом выходах блока 7 устанавливается код 010 соответственно. При этом на выходе элементов И 22, 28 появляется сигнал «ЛОГ 1. Благодаря этому выполняется псевдоумнол ение с модификацией множимого. Модификация множимого происходит аналогично описанной модификации делителя.

При вычислении функции arctg.; на пятом, шестом и седьмом выходах блока 7 устанавливается код 111. Перед началом работы по восьмому выходу блока 7 выдается сигнал, поступающий на элементы И 33, 36, что обеспечивает обмен информацией между регистрами 2 и 3. При этом делимое оказывается в регистре 3, а делитель - в регистре 2. На выходе элемента И 24 в соответствии с кодом на пятом, шестом и седьмом выходах блока 7 образуется сигнал «ЛОГ I. Это обеспечивает поступление через коммутатор 11 сдвинутой на определенное число разрядов информации, содержащейся в регистре 3, на вход сумматора 8 и через коммутатор 21 инверсной информации из регистра 2 на вход сумматора 20. Так как сигнал на пятом выходе блока 7 равен «ЛОГ 1, то на блоке 30 происходит «обратное сравнение. Процесс получения очередной цифры псевдочастного аналогичен описанному. После вычисления очередной цифры псевдочастного по первому выходу блока 7 выдается сигнал, поступающий на входы элементов И 31, 34 и на входы регистра 4, на вход элемента И 34 по пятому выходу блока 7 приходит сигнал «ЛОГ 1, а на элемент И 31 через элемент НЕ 19 - сигнал «ЛОГ О. Этим достигается сдвиг информации на один разряд влево в регистрах 3 и 4. В остальном процесс получения псевдочастного аналогичен описанному процессу псевдоделения.

Затем для обеспечения процесса умножения констант вида arctg на полученное псевдочастное, на пятом, шестом и седьмом выходах блока 7 устанавливается код 100 соответственно. Процесс получения произведения аналогичен описанному процессу умножения констант,

Вычисление функции igx происходит аналогично вычислению фуикцит arctg л- с той лишь разницей, что вначале 1 ро::одится деление аргумента на КОНСТРЛГГЫ вида 10- arctg

, а затем псевдоумножепие с модификацией множимого. При делении на константы на пятом, шестом и седьмом выходах блока 7 устанавливается код 101 соответственно. При этом на выходе элемента И 27 имеется сигнал

«ЛОГ 1, а на выходе элемента И 22 - сигнал «ЛОГ О. Далее выполняется процесс деления на константы, аналогичный описанному. Перед началом псевдоумножения множимое по входу 1 записывается в регистр 3, а регистр 2 обнуляется. По восьмому выходу блока 7 выдается сигнал, поступающий на элементы И 33, 36, благодаря этому происходит обмен информацией между регистрами 2 и 3, причем множимое оказывается в регистре 2.

Для выполнения псевдоумнол ения на пятом, шестом и седьмом выходах блока 7 зстанавливается код ПО, на выходе элемента И 25 - сигнал «ЛОГ 1. Это обеспечивает поступление через коммутатор И сдвинутой на определенное число разрядов инверсной информации, содержащейся в регистре 3, на вход сумматора 8 и через коммутатор 21 информации из регистра 2 на вход сумматора 20. Умножение на одну цифру множителя заканчивается

после обнуления младшего разряда регистра 4. После этого из блока 7 по второму выходу выдается сигнал, поступающий на входы элементов И 32, 35 и на сдвиговый вход регистра 4. На вход элемента И 35 по пятому выходу

блока 7 приходит сигнал «ЛОГ 1, а на элемент И 32 через элемент НЕ 19 - сигнал «ЛОГ О. Это обеспечивает сдвиг информации, находящейся в регистрах 3 и 4, на один разряд вправо. Одновременно от содержимого счетчика 12 с помощью сигнала, выдаваемого по четвертому выходу блока 7, происходит вычитание единицы. Процесс продолжается до полного обнуления регистра 4. Результат находится в регистре 3.

В случае выполнения операции умножения по входу 1 множимое записывается в регистр 3, множитель - в регистр 4, а регистр 2 обнуляется. На пятом, шестом и седьмом выходах блока 7 устанавливается код 000 соответственно. Процесс аналогичен описанному процессу умножения констант.

При выполнении операции деления на пятом, шестом и седьмом выходах блока 7 устанавливается код 001 соответственно. Процесс

аналогичен описанному процессу деления на константы.

Из приведенного описания работы устройства очевидно, что блок управления является полностью универсальным для всех шести режимов работы, что дает возможность упростить его путем выделения стандартных циклов и микрокоманд.

Наличие блоков сравнения и модификатора позволяет реализовать алгоритм деления без

восстановления остатка, а также прочодить

параллельно обработку делимого (частичного произведения) и модификацию делителя (множимого). Это обеспечивает снижение аппаратурных затрат, так как в устройстве, в отличие от известных, отсутствует дополнительный регистр модификатора.

Кроме того, повышается быстродействие, устройства за счет исключения затрат време-. ни на восстановление остатка и сдвиг регист-. ра модификатора.

Формула изобретения

Устройство для вычисления элементарных функций, содержащее элементы И, НЕ, регистры данных, первые входы которых соединены с информационным входом устройства, выход первого регистра данных подключен к первому входу первого сумматора, второй вход которого через первый коммутатор соединен с выходом второго регистра данных, второй, третий и четвертый входы третьего регистра данных соединены соответственно с первым, вторым и третьим выходами блока управления, первый управляющий вход первого коммутатора соединен с третьим выходом блока управления, четвертый выход которого подключен к входу счетчика сдвигов модификатора, выход которого соединен с входом дешифратора, регистр синхронизации, входкоторого подключен к управляющему входу устройства и к первому входу блока управления, отличающееся тем, что, с целью упрощения устройства и увеличения его быстродействия, оно содержит блок модификатора, входы которого соединены соответственно с выходами разрядов второго регистра данных, дешифратора, регистра синхронизации, с пятым выходом блока управления и выходом первого элемента НЕ, вход которого подключен к пятому выходу блока управления, второй сумматор, первый вход которого соединен с выходом второго регистра даных, а второй вход соединен с выходом второго коммутатора, первый информационный вход которого соединен с выходом первого регистра данных, а второй информационный вход соединен с выходом блока модификатора и с информационным входом первого коммутатора, первый управляющий вход .второго коммутатора соединен с третьим выходом блока управления, второй управляющий вход - с выходом первого элемента И, первый вход которого соединен с выходом первого элемента НЕ, а второй вход соединен с шестым выходом блока управления и пеовым входом второго элемента И, второй

вход которого соединен с пятым выходом блока управления, а выход - с первыми входами третьего и четвертого элементов И и входом второго элемента НЕ, выход которого соединен с первыми входами пятого и щестого элементов И, вторые входы третьего и пятого элементов И соединены с седьмым выходом блока уцравления и входом третьего элемента НЕ, выход которого подключен к вторым входам четвертого и шестого элементов И, выход третьего элемента И подключен к второму управляющему входу первого коммутатора и к третьему управляющему входу второго коммутатора, выход четвертого элемента И подключен к третьему управляющему входу первого коммутатора и к четвертому управляющему входу второго коммутатора, выход пятого элемента И подключен к четвертому управляющему входу первого коммутатора, пятый управляющий вход которого соединен с выходом щестого элемента И, блок сравнения, первый вход которого соединен с выходом первого сумматора и вторым входом первого регистра данных, а второй вход соединен с выходом

второго сумматора и вторым входом второго регистра данных, третий вход соединен с пятым выходом блока управления, второй вход которого соединен с выходом блока сравнения, первые входы первого и второго входных

элементов Н первого и второго регистров данных соединены с первым и вторым выходами блока управления соответственно, вторые входы первого и второго входных элементов И первого регистра данных соединены с выходом первого элемента НЕ, а вторые входы первого и второго входных элементов И второго регистра данных соединены с пятым выходом блока управления, первые входы третьих входных элементов И первого и второго регистров данных соединены с выходами второго и первого регистра данных соответственно, а вторые входы соединены с восьмым выходом блока управления.

Нсточники информации, принятые во внимание при экспертизе:

1.Башлаков Е. П. и др. Вопросы развития структур малых ЦВМ с произвольной значностью используемой системы счисления. Кибернетика № 1, 1972.

2.Парини Д. А. Система Дивик для решения сложных навигационных задач. Электроника № 18, 1966.

3.I. Е. Meggit «Psendo Division and Pseudo Multiplication Processes JEM Journal, April

1962 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Устройство для вычисления элементарных функций | 1973 |

|

SU546890A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

Авторы

Даты

1977-05-30—Публикация

1974-04-04—Подача