(54) СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции погрешности аналого-цифровых преобразователей | 1986 |

|

SU1341717A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU930650A2 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Счетчик импульсов с визуальной индикацией | 1978 |

|

SU767973A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1336029A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 2016 |

|

RU2633095C1 |

I

Изобретение относится к измерительной технике и может быть использовано для построения аналого-цифровых преобразователей.

Известен способ аналого-цифрового преобразования, содержащий равношаговое урановешивание входной величины компенсирующим напряжением 1.

Однако известный способ отличаетсясложностью и непостоянством диапазона разброса относительной погрещности по диапазону измерения.

Ближайшим техническим решением к предлагаемому способу является способ . аналого-цифрового преобразования, основанный на дискретном урановешивании входной величины компенсирующим напряжением 2.

Недостатком такого способа является непостоянство относительной погрешности преобразования по диапазону измерения.

Цель изобретения - выравнивание относительной погрешности по всему диапазону преобразования.

Указанная цель достигается тем, что осуществляют тактированный сдвиг выходного

цифрового результата в регистре памяти до появления единицы в его старшем разряде с одновременным подсчетом числа тактов сдвига, определяющего положение «запятой в цифровом результате.

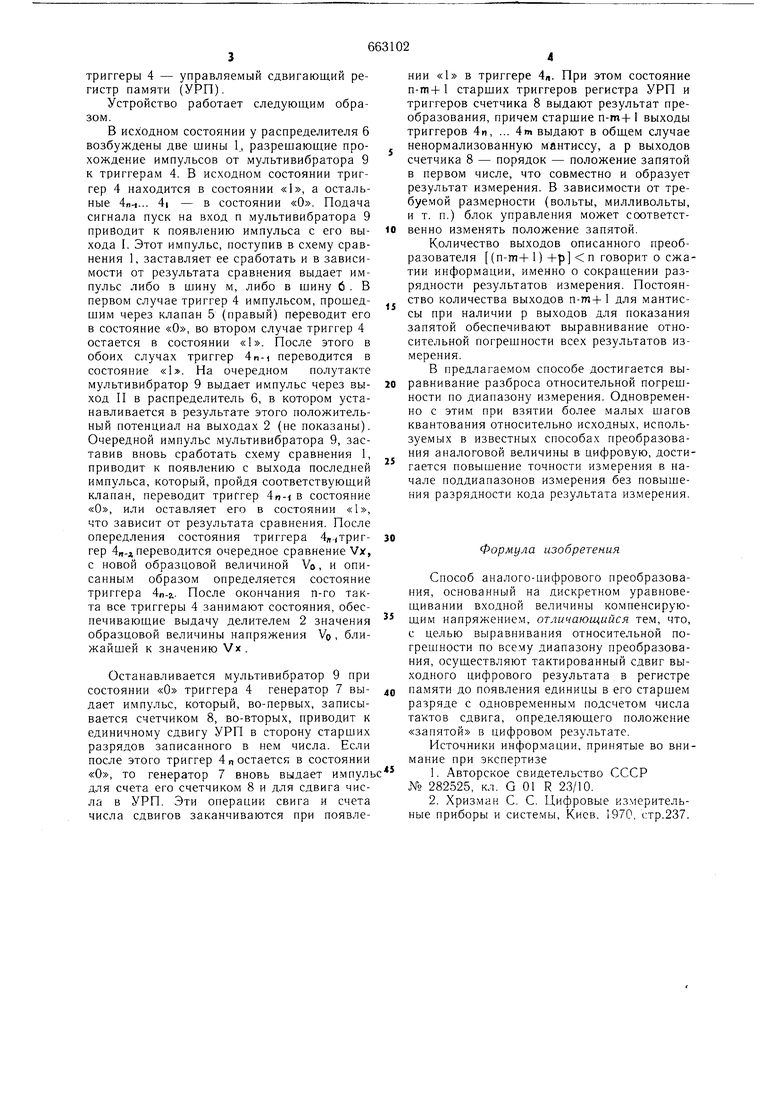

На чертеже представлена блок-схема устройства для реализации способа, выполненного согласно данному изобретению.

Блок-схема содержит схему сравнения 1, один из входов которой подключен к выходу резистивного п-разрядного делителя 2, входами подключенного через ключи управления 3 к выходам триггеров 4 сдвигающего регистра, входы которых подключены через клапаны 5 к выходам распределителя импульсов 6. Тактовый вход сдвигающего регистра подключен к выходу ждущего генератора 7 импульсов сдвига и входу счетчика 8, при этом первый и второй выходы управляемого мультивибратора 9 подключены соответственно к входам распределителя 6 и схемы сравнения, выходами подключенной к управляющим входам клапанов 5. Делитель 2 и ключи управления 3 составляют преобразователь код-напряжение (ПКН), а триггеры 4 - управляемый сдвигающий регистр памяти (УРП). Устройство работает следующим образом. В исходном состоянии у распределителя 6 возбуждены две шины 1, разрешающие прохождение импульсов от мультивибратора 9 к триггерам 4. В исходном состоянии триггер 4 находится в состоянии «1, а остальные 4п-1... 4| - в состоянии «О. Подача сигнала пуск на вход п мультивибратора 9 приводит к появлению импульса с его выхода I. Этот импульс, поступив в схему сравнения 1, заставляет ее сработать и в зависимости от результата сравнения выдает импульс либо в шину м, либо в шину 6 . В первом случае триггер 4 импульсом, прошедшим через клапан 5 (правый) переводит его в состояние «О, во втором случае триггер 4 остается в состоянии «1. После этого в обоих случах триггер 4пм переводится в состояние «1. На очередном полутакте мультивибратор 9 выдает импульс через выход II в распределитель 6, в котором устанавливается в результате этого положительный потенциал на выходах 2 (не показаны). Очередной импульс мультивибратора 9, заставив вновь сработать схему сравнения 1, приводит к появлению с выхода последней импульса, который, пройдя соответствующий клапан, переводит триггер 4г7- в состояние «О, или оставляет его в состоянии «1, что зависит от результата сравнения. После опередления состояния триггера 4п-(Триггер 4„-, переводится очередное сравнение Vx, с новой образцовой величиной Vo, и описанным образом определяется состояние триггера 4п-г.. После окончания п-го такта все триггеры 4 занимают состояния, обеспечивающие выдачу делителем 2 значения образцовой величины напряжения УО , ближайшей к значению Vx . Останавливается мультивибратор 9 при состоянии «О триггера 4 генератор 7 выдает импульс, который, во-первых, записывается счетчиком 8, во-вторых, приводит к единичному сдвигу УРП в сторону старших разрядов записанного в нем числа. Если после этого триггер 4постается в состоянии «О, то генератор 7 вновь выдает импуль для счета его счетчиком 8 и для сдвига числа в УРП. Эти операции свига и счета числа сдвигов заканчиваются при появлеНИИ «1 в триггере 4п. При этом состояние n-m-l-l старших триггеров регистра УРП и триггеров счетчика 8 выдают результат преобразования, причем старшие п-т-ь 1 выходы триггеров 4п, ... 4т выдают в общем случае ненормализованную мантиссу, а р выходов счетчика 8 - порядок - положение запятой в первом числе, что совместно и образует результат измерения. В зависимости от требуемой размерности (вольты, милливольты, и т. п.) блок управления может соответственно изменять положение запятой. Количество выходов описанного преобразователя (п-т+ 1) +|з п говорит о сжатии информации, именно о сокращении разрядности результатов измерения. Постоянство количества выходов п-т+ 1 для мантиссы при наличии р выходов для показания запятой обеспечивают выравнивание относительной погрещности всех результатов измерения. В предлагаемом способе достигается выравнивание разброса относительной погрешности по диапазону из.мерения. Одновременно с этим при взятии более .малых шагов квантования относительно исходных, используемых в известных способах преобразования аналоговой величины в цифровую, достигается повышение точности измерения в начале поддиапазонов измерения без повышения разрядности кода результата измерения. Формула изобретения Способ аналого-цифрового преобразования, основанный на дискретном уравновешивании входной величины компенсирующим напряжением, отличающийся тем, что, с целью выравнивания относительной погрешности по всему диапазону преобразования, осуществляют тактированный сдвиг выходного цифрового результата в регистре памяти до появления единицы в его старшем разряде с одновременным подсчетом числа тактов сдвига, определяющего положение «запятой в цифровом результате. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 282525, кл. G 01 R 23/10. 2.Хризман С. С. Цифровые измерительные приборы и системы, Киев, 1970, стр.237.

т /

Авторы

Даты

1979-05-15—Публикация

1971-07-20—Подача