.1I 2

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройст согласования ЭВМ с различными форматами данных.

Цель изобретения - расширение класса решаемых задач путем обеспечения преобразования шестнадцатиричных чисел;

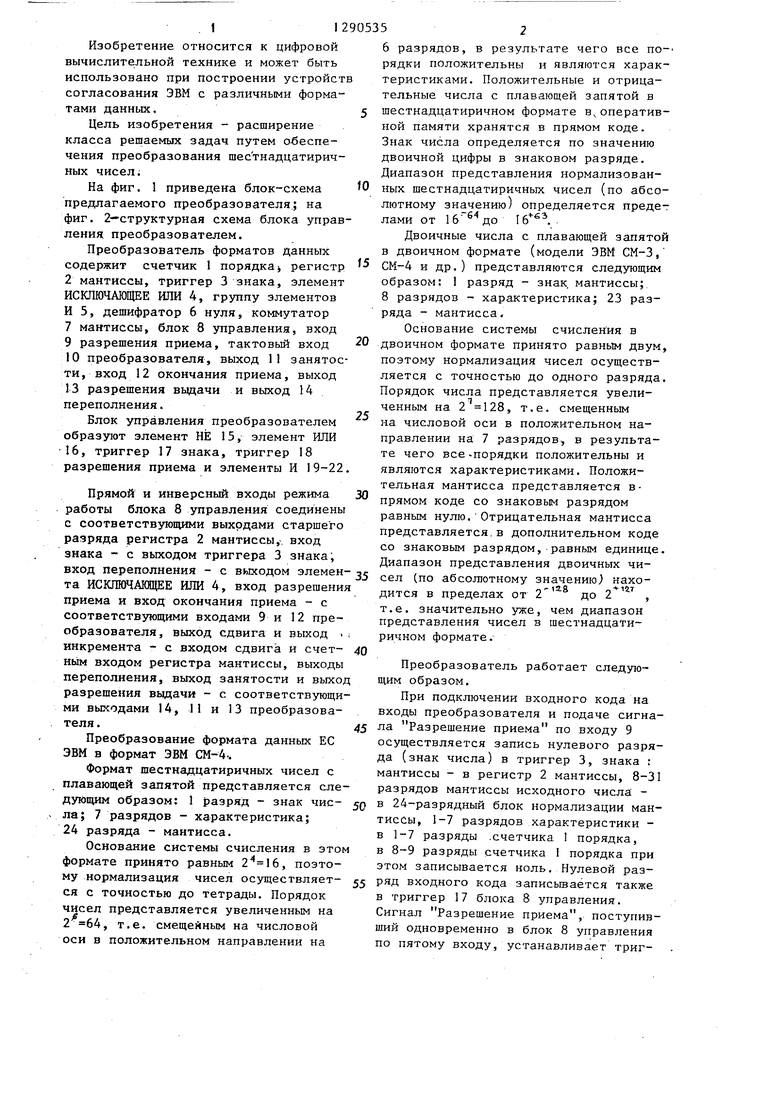

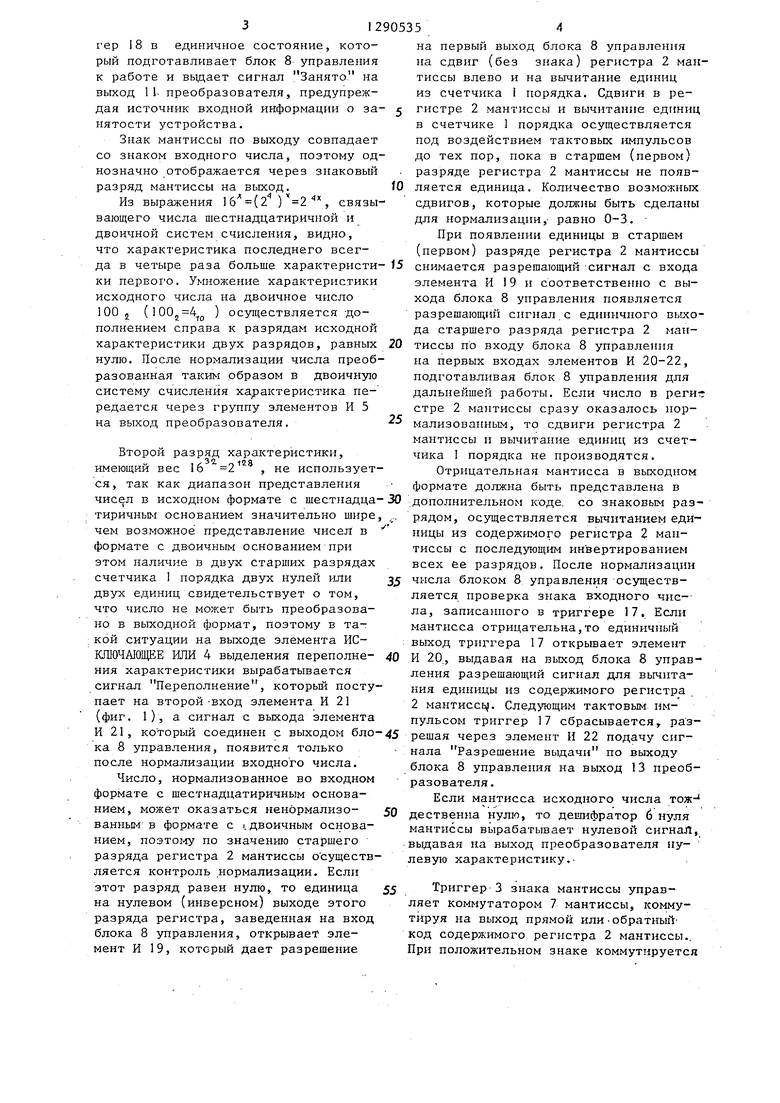

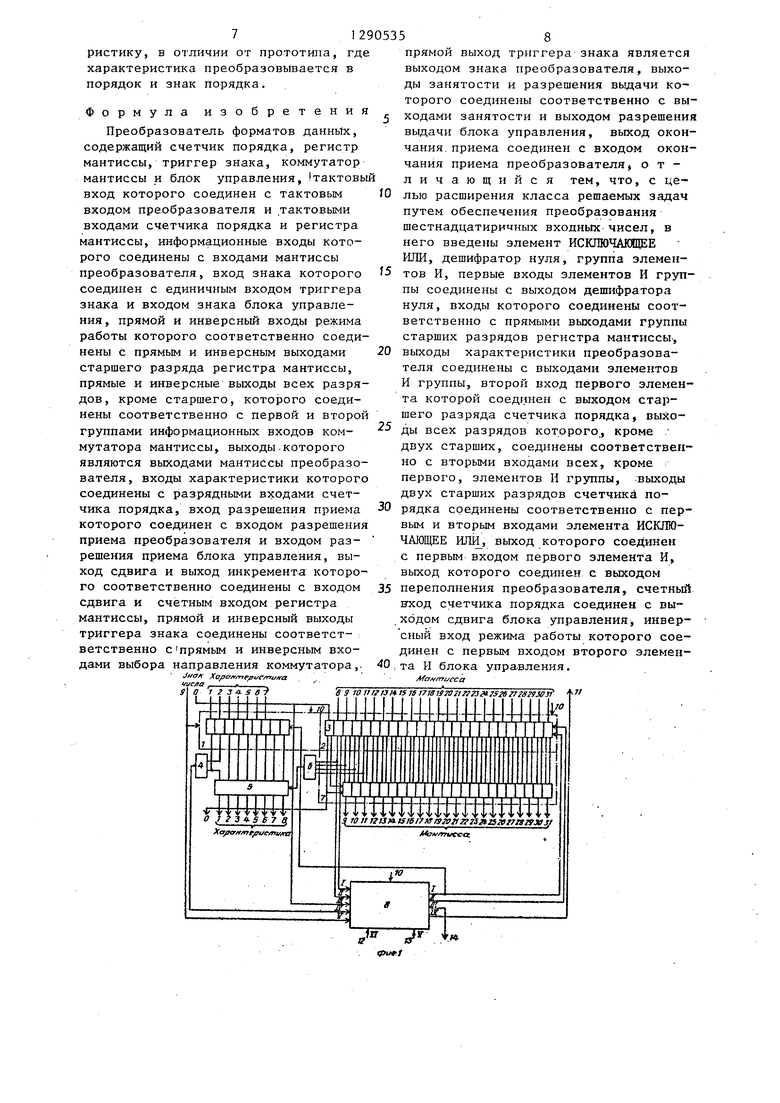

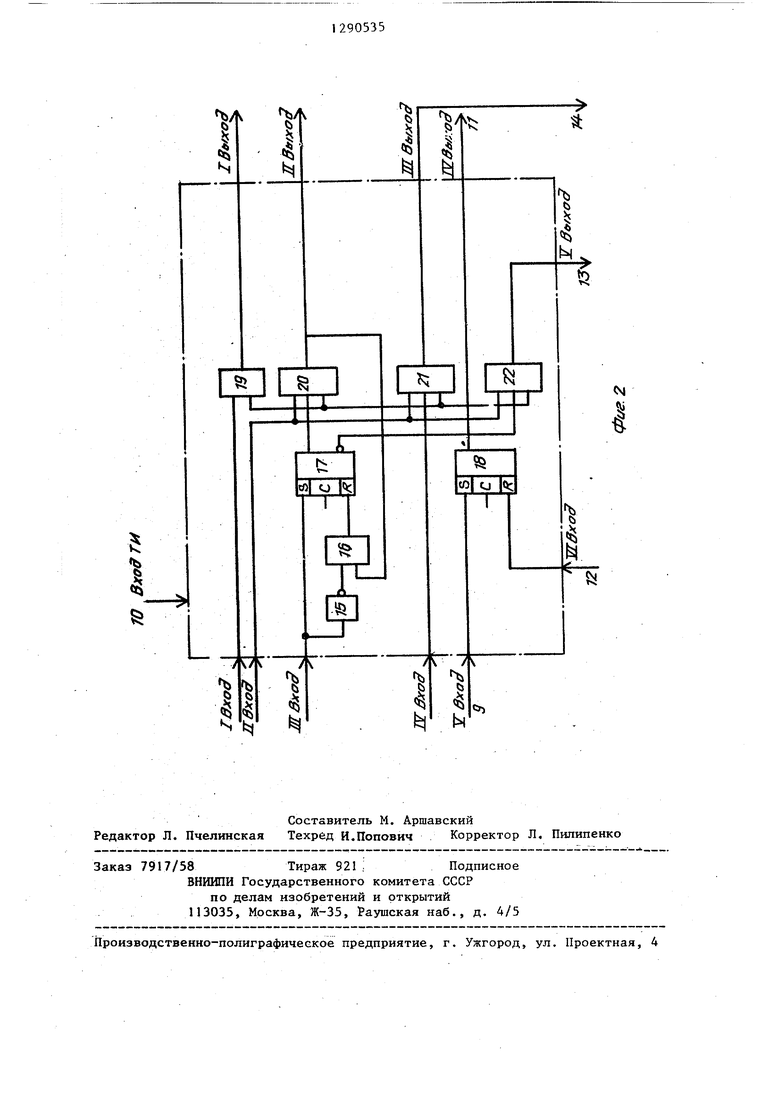

На фиг. 1 приведена блок-схема предлагаемого преобразователя; на фиг. 2-структурная схема блока управления преобразователем.

Преобразователь форматов данных содержит счетчик 1 порядка регистр 2 мантиссы, триггер 3 знака, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, группу элементов ИЗ, дешифратор 6 нуля, коммутатор 7 мантиссы, блок 8 управления, вход

9разрешения приема, тактовый вход

10преобразователя, выход 11 занятое ти, вход 12 окончания приема, выход 13 разрешения выдачи и выход 14 переполнения.

Блок управления преобразователем образуют элемент НЕ 15, элемент ИЛИ 16, триггер 17 знака, триггер 18 разрешения приема и элементы И 19-22

Прямой и инверсный входы режима работы блока 8 управления соединены с соответствующими выходами старшего разряда регистра 2 мантиссы,-, вход знака - с выходом триггера 3 знака; вход переполнения - с выходом элемен- та ИСКЛЮЧАКИЦЕЕ ИЛИ 4, вход разрешения приема и вход окончания приема - с соответствующими входами 9 и 12 преобразователя, выход сдвига и выход . инкремента - с входом сдвига и счет- ным входом регистра мантиссы, выходы переполнения, выход занятости и выход разрешения выдачи - с соответствующими выходами 14, 11 и 13 преобразователя.

Преобразование формата данных ЕС ЭВМ в формат ЭВМ СМ-4..

Формат шестнадцатиричных чисел с плавающей запятой представляется следующим образом: 1 разряд - знак чис- ла; 7 разрядов - характеристика; 24 разряда - мантисса.

Основание системы счисления в этом формате принято равным , поэтому нормализация чисел осуществляет- ся с точностью до тетрады. Порядок

чисел представляется увеличенным на 2 64, т.е. смещенным на числовой оси в положительном на.правлении на

O

6

5

0

5

0 0

6 разрядов, в результате чего все по- рядки положительны и являются характеристиками. Положительньш и отрицательные числа с плавающей запятой в шестнадцатиричном формате в оперативной памяти хранятся в прямом коде. Знак числа определяется по значению двоичной цифры в знаковом разряде. Диапазон представления нормализованных шестнадцатиричных чисел (по абсолютному значению) определяется преде-т лами от Гб .

Двоичные числа с плавающей запятой в двоичном формате (модели ЭВМ СМ-3, СМ-4 и др.) представляются следующим образом: 1 разряд - знак, мантиссы; 8 разрядов - характеристика; 23 разряда - мантисса.

Основание системы счисления в двоичном формате принято равным двум, поэтому нормализация чисел осуществляется с точностью до одного разряда. Порядок числа представляется увеличенным на 2 128, т.е. смещенным на числовой оси в положительном направлении на 7 разрядов, в результате чего все-порядки положительны и являются характеристиками. Положительная мантисса представляется в- прямом коде со знаковым разрядом равным нулю.Отрицательная мантисса представляется.в дополнительном коде со знаковым разрядом, равным единице. Диапазон представления двоичных чисел (по абсолзотному значению нахо/i l2.8

дится в пределах от 2 до 2 ,

т.е. значительно уже, представления чисел в

ричном формате.

Преобразователь работает следующим образом.

При подключении входного кода на входы преобразователя и подаче сигна- ла Разрешение приема по входу 9

осуществляется запись нулевого разряда (знак числа) в триггер 3, знака : мантиссы - в регистр 2 мантиссы, 8-31 разрядов мантиссы исходного числа - в 24-разрядный блок нормализации ман- тисСы, 1-7 разрядов характеристики - в 1-7 разряды .счетчика 1 порядка, в 8-9 разряды счетчика 1 порядка при этом записывается ноль. Нулевой разряд входного кода записьшается также в триггер 17 блока 8 управления. Сигнал Разрешение приема, поступивший одновременно в блок 8 управления по пятому входу, устанавливает триг

312

rep 18 в единичное состояние, который подготавливает блок 8 управления к работе и выдает сигнал Занято на выход 11- преобразователя, предупреждая источник входной информации о занятости устройства.

Знак мантиссы по выходу совпадает со знаком входного числа, поэтому однозначно отображается через знаковый разряд мантиссы на выход.

Из выражения 16(2 ) , связывающего числа шестнадцатиричной и двоичной систем счисления, видно, что характеристика последнего всегда в четыре раза больше характеристи ки первого. Умножение характеристики исходного числа на двоичное число 100 J ( осуществляется -дополнением справа к разрядам исходной характеристики двух разрядов, равных нулю. После нормализации числа преобразованная таким образом в двоичную систему счисления характеристика передается через группу элементов И 5 на выход преобразователя.

Второй разряд характеристики,

, зг 123

имеющий вес 16 2 , не используется, так как диапазон представления чисел в исходном формате с шестнадца- 30 тиричным основанием значительно шире, ,,. чем возможное представление чисел в ормате с двоичным основанием при этом наличие в двух старших разрядах счетчика 1 порядка двух нулей или 35 двух единиц свидетельствует о том, что число не может быть преобразовано в выходной формат, поэтому в та- кой ситуации на выходе элемента PIC- ; КШОЧА10ЩЕЕ ИЛИ 4 выделения переполне- 40 ния характеристики вырабатывается сигнал Переполнение, который поступает на второй-вход элемента И 21 (фиг. 1), а сигнал с выхода элемента И 21, который соединен с выходом бло-45 ка 8 управления, появится только после нормализации входного числа.

Число, нормализованное во входном формате с шестнадцатиричным основанием, может оказаться ненормализо- 50 ванным в формате с . двоичным основанием, поэтому по значению старшего разряда регистра 2 мантиссы осуществляется контроль нормализации. Если этот разряд равен нулю, то единица 55 на нулевом (инверсном) выходе этого разряда регистра, заведенная на вход блока 8 управления, открывает элемент И 19, который дает разрешение

fO

f5 0

5

0 ,,. 5 ; 0 5

0 5

на первый выход блока 8 управления па сдвиг (без знака) регистра 2 мантиссы влево и на вычитание единиц из счетчика 1 порядка. Сдвиги в регистре 2 мантиссы и вычитание единиц в счетчике 1 порядка осуществляется под воздействием тактовых импульсов до тех пор, пока в старшем (первом) разряде регистра 2 мантиссы не появляется единица. Количество возможных сдвигов, которые должны быть сделаны для нормализации,- равно 0-3.

При появлении единицы в старшем (первом) разряде регистра 2 мантиссы снимается разрешающий сигнал с входа элемента И 19 и соответственно с выхода блока 8 управления появляется разрешающий сигнал,с единичного вько- да старшего разряда регистра 2 мантиссы по входу блока 8 управле П1я па первых входах элементов И 20-22, подготавливая блок 8 управления для дальнейшей работы. Если число в регистре 2 мантиссы сразу оказалось нормализованным, то сдвиги регистра 2 мантиссы и вычитание единиц из счетчика 1 порядка не производятся.

Отрицательная мантисса в выход ом формате должна быть представлена в дополнительном коде, со знаковым разрядом, осзтцествляется вычитанием единицы из содержимого регистра 2 мантиссы с последующим инвертированием всех ее разрядов. После нормализации числа блоком 8 управления осуществляется проверка знака входного чис-- ла, записанпого в триггере 17. Если мантисса отрицательна,то единичный выход триггера 17 открывает элемент И 20., выдавая на выход блока 8 управления разрешающий сигнал для вычитания единицы из содержимого регистра 2 мантиссЕ. Следующим тактовым импульсом триггер 17 сбрасывается, разрешая через элемент И 22 подачу сигнала Разрешение выдачи по выходу блока 8 управления на выход 13 преобразователя.

Если мантисса исходного числа тож- дественна нулю, то дешифратор б нуля мантиссы вырабатывает нулевой сигнал, выдавая на выход преобразователя нулевую характеристику.Триггер 3 знака мантиссы управляет коммутатором 7 мантиссы, коммутируя на выход прямой или-обратный- код содержимого регистра 2 мантиссы.. При положительном знаке коммутируется

512905356

прямой код, при отрицательном до- по входу 12 блока 8 управления, кото- полнительный,рый сбрасывает триггер 18 в нулевое

После того, как выходной код при- состояние, снимает сигнал занятости нят приемником информации,- из него. по выходу 11, после чего устройство должен поступить сигнал Принято 5 -,готово к приему нового числа.

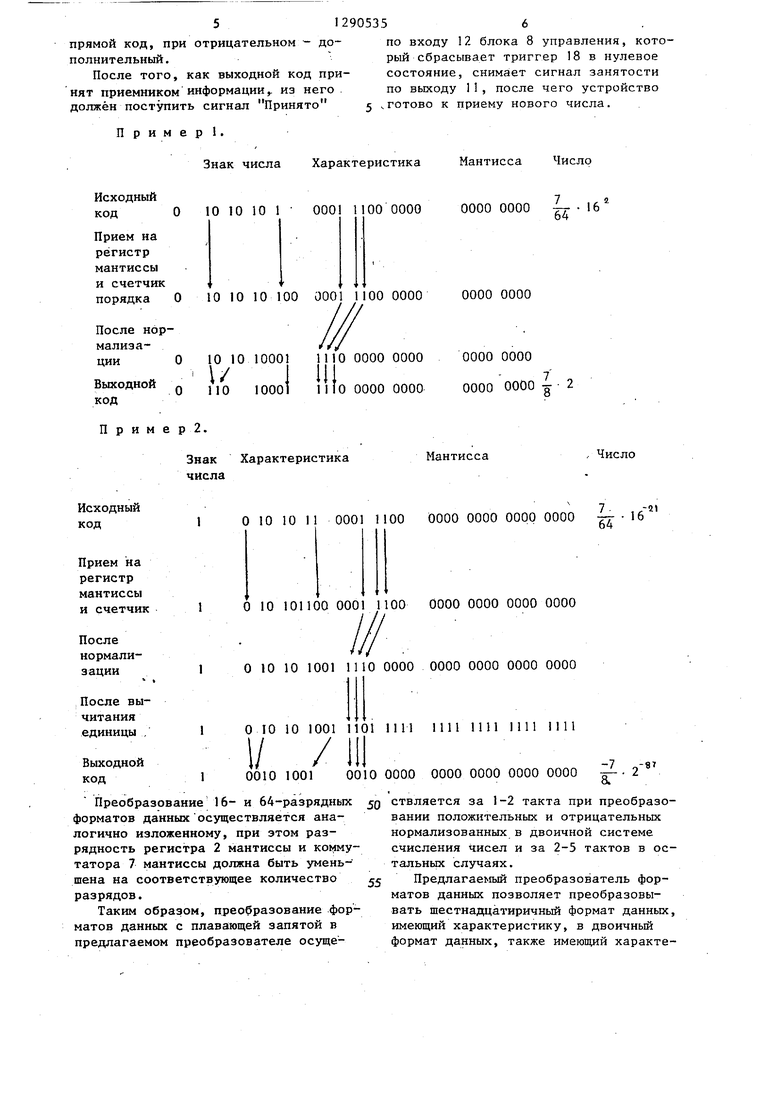

р.

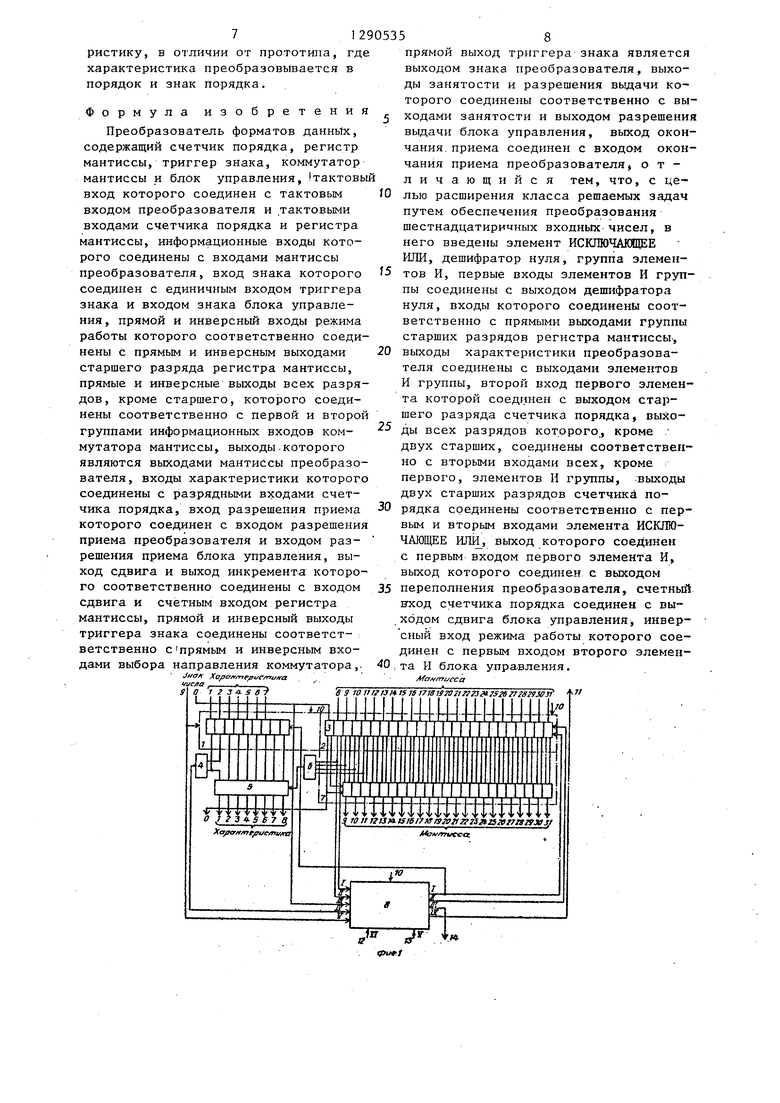

Знак числа

10 10 10 1

Характеристика

000 1100 0000

код и р и м е р 2.

Знак Характеристика числа

Мантисса

Число

0000 0000 тт 64

0000 0000

0000 0000 0000 0000 д- 2

Мантисса

Число

Исходный код

Прием на регистр мантиссы и счетчик

После нормализации

1

После вычитанияединицы ,

Выходной код

7 -21

О 10 10 II 0001 1100 0000 0000 0000 0000 г 16 I ...64

6 10 0001 1100 0000 0000 0000 0000

1

о 10 10 1001 1110 0000 0000 0000 0000 0000

1 о 10 10 1001 1101 1111 1111 1111 1111

I/ /ill

1 0010 1001 0010

0000 0000 0000 0000 0000 -

СХ

0000 0000 0000 0000 0000 -

СХ

Преобразование 16- и 64-разрядных форматов данных осуществляется аналогично изложенному, при этом разрядность регистра 2 мантиссы и коммутатора 7 мантиссы должна быть уменьшена на соответствующее количество разрядов.

Таким образом, преобразование форматов данных с плавающей запятой в предлагаемом преобразователе осуществляется за 1-2 такта при преобразовании положительных и отрицательньк нормализованных в двоичной системе счисления чисел и за 2-5 тактов в остальных случаях.

Предлагаемый преобразователь форматов данных позволяет преобразовывать шестнадцатиричный формат данных, имеющий характеристику, в двоичный формат данных, также имеющий характеристику, в отличии от прототипа, где характеристика преобразовывается в порядок и знак порядка.

Формула изобретения

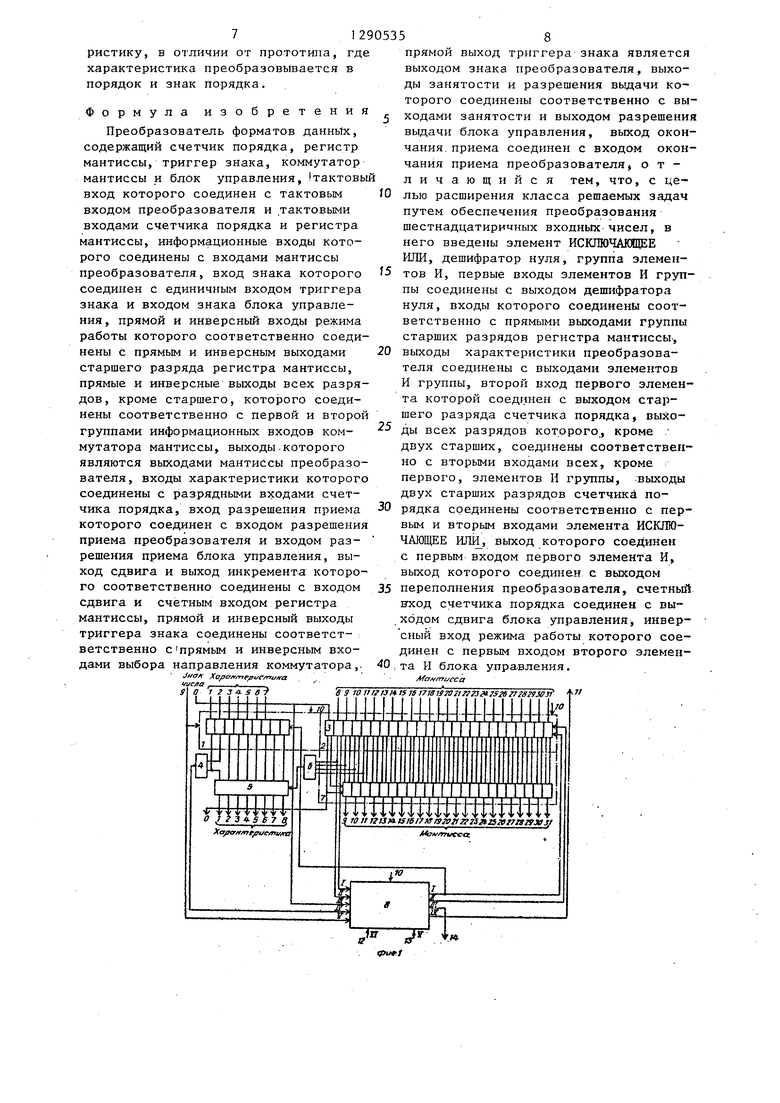

Преобразователь форматов даннь1х, содержащий счетчик порядка, регистр мантиссы, триггер знака, коммутатор мантиссы и блок управления, тактовый

вход которого соединен с тактовым входом преобразователя и .тактовыми входами счетчика порядка и регистра мантиссы, информационные входы которого соединены с входами мантиссы преобразователя, вход знака которого соединен с единичным входом триггера знака и входом знака блока управления, прямой и инверсный входы режима работы которого соответственно соединены с прямым и инверсным выходами старшего разряда регистра мантиссы, прямые и инверсные выходы всех разрядов, кроме старшего, которого соединены соответственно с первой и второй группами информационных входов коммутатора мантиссы, выходы-которого являются выходами мантиссы преобразователя, входы характеристики которого соединены с разрядными входами счетчика порядка, вход разрешения приема которого соединен с входом разрешения приема преобразователя и входом разрешения приема блока управления, выход сдвига и выход инкремента которого соответственно соединены с входом сдвига и счетным входом регистра мантиссы, прямой и инверсный выходы триггера знака соединены соответст- ветственно с прямым и инверсным входами выбора направления коммутатора,.

нак Xa/ cf/rfne/tt/f/mtjfa иасла

JO лью расширения класса путем обеспечения пре шестнадцатиричных вхо него введены элемент ИЛИ, дешифратор нуля

15 тов И, первые входы э пы соединены с выходо нуля, входы которого ветственно с прямыми старших разрядов реги выходы характеристик теля соединены с выхо И группы, второй вход та которой соединен с шего разряда счетчика ды всех разрядов KOTo двух старших, соедине но с вторыми входами первого, элементов И двух старших разрядов

30 рядка соединены соотв вым и вторым входами ЧАЮЩЕЕ ИЛИ, выход кот с первым входом перво выход которого соедин

35 переполнения преобраз вход счетчика порядка ходом сдвига блока уп сный вход режима рабо динен с первым входом

40. та И блока управления

AfCff f77UCC О

20

25

в 3 10 //tf/J/ /51617ieiS ll2IK232t f26 tS2}XSf

.иштп

./ Z 3 is 671

Xa /rmtpafirrt/fra

я

ый

оа а ияойогоаия ом,.

2905358

прямой выход триггера знака является выходом знака преобразователя, выходы запятости и разрешения вьздачи которого соединены соответственно с выходами занятости и выходом разрешения выдачи блока управления, выход окончания, приема соединен с входом окончания приема преобразователя, отличающийся тем, что, с цеJO лью расширения класса решаемых задач путем обеспечения преобразования шестнадцатиричных входных чисел, в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор нуля, группа элемен15 тов И, первые входы элементов И группы соединены с выходом дешифратора нуля, входы которого соединены соответственно с прямыми выходами группы старших разрядов регистра мантиссЫ , выходы характеристики преобразователя соединены с выходами элементов И группы, второй вход первого элемента которой соединен с выходом старшего разряда счетчика порядка, выходы всех разрядов KOToporOj кроме . двух старших, соединены соответственно с вторыми входами всех, кроме первого, элементов И группы, выходы двух старших разрядов счетчика по30 рядка соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с выходом

35 переполнения преобразователя, счетньй вход счетчика порядка соединен с выходом сдвига блока управления инверсный вход режима работы которого соединен с первым входом второго элемен40. та И блока управления.

AfCff f77UCC О

20

25

7/

K232t f26 tS2}XSf

J ffrrtfCCtZ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Преобразователь форматов данных | 1986 |

|

SU1466012A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь форматов данных | 1989 |

|

SU1728971A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Преобразователь форматов данных | 1989 |

|

SU1686701A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

Изобретение относится к области ., автоматики и цифровой вычислительной техники и может быть использовано при построении устройств сопряжения с ЭВМ, работающими с различными форматами данных. Целью изобретения является расширение функциональных возможностей за счет обеспечения преобразования шестнадцатиричных чисел. Поставленная цель достигается за счет введения в преобразователь, содержащий счетчик порядка, регистр мантиссы, коммутатор мантиссы и блок управления, дешифратора нуля, группы элементов И и элемента ИСКЛЮЧАЮОЩЕ ИЛИ, обеспечивающего контроль диапазона чисел, формирование, смещенной характеристики и нормализацию мантиссы. 2 ил. (Л сг N3 со О ел 00 СП

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| G,06 F 5/02, 1982. | |||

Авторы

Даты

1987-02-15—Публикация

1985-08-16—Подача